【PCIe在嵌入式系统中的集成】:优化与创新策略

发布时间: 2025-01-05 06:10:33 阅读量: 14 订阅数: 15

高级FPGA设计 结构、实现和优化_中英文

# 摘要

PCIe技术作为高性能计算机和嵌入式系统的关键互连技术,在数据传输和硬件集成中扮演着核心角色。本文首先概述了PCIe技术及其在嵌入式系统中的应用,深入探讨了硬件集成的基础知识,包括接口标准、硬件设计、布局以及驱动程序开发。进而,文章分析了PCIe软件集成与优化实践,涉及软件栈、性能调优和故障诊断。创新策略的应用在提高PCIe集成效率和安全性方面发挥了重要作用,包括硬件设计的创新、软件虚拟化技术以及安全合规性。本文最后通过案例分析,预测了PCIe集成技术的未来趋势与行业影响,为相关领域提供了深刻的见解和技术方向。

# 关键字

PCIe技术;嵌入式系统;硬件集成;软件优化;创新策略;技术趋势

参考资源链接:[Synopsys DesignWare PCIe Dual Mode IP控制器产品指南](https://wenku.csdn.net/doc/7sg0xe4zbz?spm=1055.2635.3001.10343)

# 1. PCIe技术概述及其在嵌入式系统中的作用

## 1.1 PCIe技术的历史与发展

PCI Express(PCIe)是一种高性能的通用串行总线标准,用于连接主机处理器与外围设备。自从PCI总线技术诞生以来,PCIe以其高速率、高带宽、点对点串行连接等优势迅速取代了传统的PCI技术,成为当今计算机和嵌入式系统中的主流接口标准。随着科技发展,PCIe技术也在不断的演进,从最初的PCIe 1.0到现在广泛采用的PCIe 4.0,其传输速率已经提升数十倍,满足了数据密集型应用的需求。

## 1.2 PCIe在嵌入式系统中的重要性

嵌入式系统是高度专用的计算机系统,常用于实时控制、工业自动化、医疗设备等领域。PCIe在这些系统中的作用是至关重要的,因为它提供了一种高速、稳定的连接方式,可以有效地将各种功能模块集成到系统中。例如,在高性能计算和图形处理场景中,使用PCIe可以实现高带宽的GPU直连,显著提高系统的数据处理和图形渲染能力。

## 1.3 PCIe技术的关键优势

PCIe技术相较于其他总线标准,具有以下关键优势:

- **更高的数据传输速率**:通过增加通道数量(lane),PCIe可以提供超过1GB/s的数据吞吐量。

- **更好的扩展性和灵活性**:PCIe支持热插拔和即插即用功能,便于系统扩展和维护。

- **点对点连接**:消除了共享总线时的竞争和延迟问题,提高了传输效率。

- **低延迟**:针对高性能应用,PCIe总线可提供非常低的通信延迟,是实时应用的理想选择。

PCIe技术的这些特点使其成为嵌入式系统设计中的首选技术,尤其在要求高性能处理能力和高效数据通信的场景中。

# 2. PCIe硬件集成基础

### 2.1 PCIe接口标准及其工作原理

PCIe(Peripheral Component Interconnect Express)是一种高速串行计算机扩展总线标准,主要用于计算机内部组件之间的连接。它的设计旨在替代传统的PCI和PCI-X总线标准,提供更高的带宽和更低的延时。

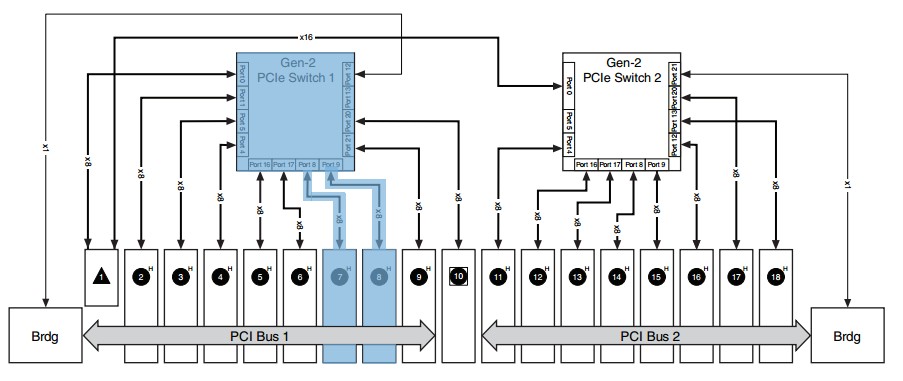

#### 2.1.1 PCIe架构简介

PCIe架构采用点对点连接,每个设备独享带宽,不像PCI总线那样需要在多个设备之间共享。其基本的构建单元是"链路"(Link),多个链路可以组合成一个"通道"(Lane)。每个通道包括一对差分信号线,用于数据的发送和接收。

PCIe采用分层的协议结构,包括事务层、数据链路层和物理层。事务层负责处理读写请求;数据链路层确保数据正确传输;物理层负责信号的传输。

#### 2.1.2 PCIe信号与电气特性

PCIe信号包括传输信号(如TX+、TX-)和接收信号(如RX+、RX-),以及辅助信号,如时钟信号、复位信号和电源信号。电气特性包括信号的电压水平、信号完整性要求和串扰限制等。为确保信号质量,PCIe要求使用阻抗匹配的布线,并对信号的反射和串扰进行严格控制。

### 2.2 PCIe硬件设计与布局

设计和布局阶段是PCIe集成的重要组成部分,它决定了硬件的电气性能和信号完整性。

#### 2.2.1 硬件连接要求

在硬件连接方面,PCIe需要采用特定的连接器和插槽,例如M.2、U.2和PCIe卡插槽。连接时需确保正确的插拔顺序和方向,避免物理损坏。另外,不同版本的PCIe接口对信号线的数量和电气特性有不同的要求,设计时应严格遵守相应的标准。

#### 2.2.2 布线与信号完整性考量

布线时必须考虑信号线的长度、间距、走线方式以及层间对齐等因素。通常需要采用专用的高速布线工具和遵循特定的布线策略,例如:采用微带线和带状线结合的布线技术,保证阻抗匹配;采用差分信号走线以减少干扰;确保足够的返回路径等。信号完整性分析包括但不限于阻抗连续性检查、时序分析、信号反射和串扰等。

### 2.3 PCIe设备驱动程序开发

为了在操作系统中使用PCIe设备,需要开发相应的设备驱动程序。

#### 2.3.1 驱动程序架构基础

设备驱动程序通常是操作系统内核的一部分,它负责管理硬件资源和提供设备访问接口给应用程序。PCIe设备驱动程序需要实现标准的驱动模型接口,例如在Linux中是PCI核心API,以及特定的驱动框架,如Windows的WDM/WDF。

#### 2.3.2 设备通信机制与接口实现

PCIe设备与CPU之间的通信通常通过直接内存访问(DMA)来实现,这种机制允许设备直接读写系统内存,从而高效传输数据。驱动程序必须正确设置DMA缓冲区,并管理好内存映射和访问权限。此外,驱动程序还需要提供一套用于与应用程序交互的接口,如文件操作接口、设备控制接口等。

在设计驱动程序时,开发者应当遵循最佳实践,如使用锁来同步并发访问,避免死锁;优化数据结构以减少内存占用和提高处理速度;测试驱动程序的健壮性以确保系统稳定运行。这些措施能显著提升PCIe设备的性能和可靠性。

# 3. PCIe软件集成与优化实践

## 3.1 PCIe软件栈和通信协议

### 3.1.1 PCIe软件栈概述

PCIe软件栈是一系列软件组件的集合,它们共同工作以实现PCI Express设备的发现、配置、管理和数据传输。软件栈的层次结构从硬件设备开始,向上延伸至操作系统内核,最终到达用户应用程序。在PCIe的上下文中,软件栈包括了从PCIe固件接口到操作系统驱动程序,再到应用程序接口的各个组件。

一个典型的PCIe软件栈由以下几个层次组成:

- **固件层**:通常称为固件或固件接口层(Firmware Interface Layer),它是软件栈与硬件连接的最底层。固件层负责PCIe设备的初始化、枚举和基本配置。这个层次的代码通常是嵌入式系统制造商根据硬件规格书开发的。

- **内核层**:位于固件层之上的是操作系统内核中的PCIe驱动程序。该驱动程序负责管理PCIe设备,提供配置空间访问,以及处理错误和中断。操作系统通常提供一个标准的PCIe驱动程序,但特定设备可能需要定制化驱动。

- **中间件层**:这一层包括在内核层和应用程序层之间的任何软件组件。这些组件通常提供更高级别的抽象,使得应用程序更容易与PCIe设备通信。

- **应用程序层**:这是软件栈的最上层,提供直接与PCIe设备交互的接口,例如通过读写操作来获取数据或控制设备。

在不同操作系统中,软件栈的实现方式可能会有所差异。例如,在Linux系统中,PCIe设备的发现和配置由内核中的PCI子系统自动处理,而Windows系统中则可能涉及到不同厂商提供的专有驱动程序。

### 3.1.2 协议层与数据传输

PCIe数据传输涉及到的协议层在软件栈中起着关键作用。数据传输流程通常涉及三个主要的协议层:**事务层**、**数据链路层**和**物理层**。

- **事务层**:该层处理与PCIe事务相关的逻辑。它负责生成和解析PCIe事务层包(TLPs),这些包包含了如内存读写、I/O操作和配置操作等请求。

- **数据链路层**:数据链路层位于事务层和物理层之间,提供了事务层包的可靠传输机制。该层负责确保数据在PCIe链路两端的正确交换,并处理链路状态的管理,如链路训练和错误检测与校正。

- **物理层**:物理层负责在PCIe设备之间传输事务层包和数据链路层包。它包含了发送和接收数据所需的电气和机械接口,管理物理连接的建立、维护和断开。

在数据传输中,需要软件来处理事务层包的构造和解析,确保数据在不同协议层之间正确地进行传递。例如,在事务层,软件可能需要准备内存读写请求,并将其打包成TLP。在数据链路层,软件将确保这些TLP被成功发送到接收方,并且如果在传输过程中发生错误,能够重传这些包。在物理层,软件需要与硬件交互以控制数据的发送和接收。

在Linux系统中,例如,事务层的逻辑通常由用户空间应用程序或内核模块实现,而数据链路层和物理层通常由内核中的PCIe驱动程序处理。这些驱动程序与硬件紧密集成,确保数据能够高效且正确地传输。

## 3.2 PCIe性能优化方法

### 3.2.1 系统级性能调优

PCIe设备的系统级性能调优涉及到多个层面,包括硬件和软件的配合优化。以下是几个重要的系统级性能调优策略:

- **DMA(直接内存访问)优化**:通过使用DMA,设备可以直接在内存中读写数据,避免CPU的介入,从而大幅提高数据传输速率。优化DMA传输可以减少数据传输过程

0

0