验证Verilog代码的最佳实践:30个案例深入分析,确保代码质量

发布时间: 2024-12-19 11:20:16 阅读量: 18 订阅数: 20

Verilog典型电路设计--华为公司案例分析

# 摘要

随着集成电路设计复杂性的增加,对Verilog代码进行彻底验证成为保证产品质量的关键环节。本文着重强调了Verilog代码验证的重要性,并系统地介绍了其基础、测试环境搭建、验证方法论及其实践案例。文中详细探讨了如何构建验证环境、采用的功能覆盖率和断言技术,并分析了性能验证、验证计划与持续集成策略。案例研究部分通过具体实例讲述了同步异步问题、资源冲突、边界条件等问题的解决方法。最后,展望了未来验证技术和验证工具的发展趋势,以期帮助工程师们提高验证效率和质量。

# 关键字

Verilog代码验证;测试环境搭建;功能覆盖率;断言技术;性能验证;持续集成;案例研究;未来趋势

参考资源链接:[Verilog实战:135个经典设计实例解析](https://wenku.csdn.net/doc/7d93ern6o2?spm=1055.2635.3001.10343)

# 1. Verilog代码验证的重要性

验证是数字电路设计流程中不可或缺的一个环节,其目的是确保设计满足其规格要求。在现代电子系统设计中,复杂度不断增加,任何小小的错误都可能导致昂贵的代价。因此,通过使用Verilog代码验证,我们可以提前发现并解决这些问题,提高设计的可靠性与质量,最终加速产品的上市时间。

## 1.1 验证在设计周期中的位置

验证工作主要在设计的早期阶段进行,其主要作用是确保设计的功能正确性。在设计、综合、布局布线等阶段之前,验证可以提前发现问题,避免这些问题在后续阶段的放大和修复。

## 1.2 验证工作的重要性

验证不仅仅是找出设计中的bug,更重要的是通过验证,能够证明设计满足了其功能和性能的需求。一个完整的验证过程,可以给设计团队带来以下好处:

- 提高产品的可靠性

- 减少后期修正成本

- 缩短开发周期

- 增加设计的可重用性

## 1.3 验证方法和策略

随着设计复杂度的提升,传统的验证方法已经无法满足需求,因此产生了多种验证策略:

- **单元测试**:针对设计中的单个模块进行验证。

- **集成测试**:将多个模块组合起来进行验证。

- **系统测试**:将设计放入整个系统中进行全面测试。

为了进行有效的验证,设计团队需要采用正确的工具和技术,例如使用模拟器执行测试用例、使用断言进行异常检测、利用覆盖率工具来量化验证的完整性。

了解了Verilog代码验证的重要性之后,下一章将介绍Verilog的基础知识以及如何搭建一个测试环境,为后续的验证流程打下坚实的基础。

# 2. Verilog基础和测试环境搭建

在本章节中,我们将深入探讨Verilog语言的基本语法元素,包括数据类型、操作符和模块端口的定义。然后,我们将聚焦于如何构建一个测试平台,涵盖了激励生成、时钟复位信号处理以及测试案例的组织。最后,我们将分析验证环境中的关键组件,例如驱动器、监视器、评分器和事务记录。

### 2.1 Verilog基本语法回顾

#### 2.1.1 数据类型和操作符

在Verilog中,数据类型可以是基本的线网(wire)或寄存器(reg),以及由它们衍生的其他复杂类型。操作符包括算术运算符、逻辑运算符、位运算符等。

```verilog

module basic_syntax_review;

// 数据类型示例

wire [7:0] wire_data; // 定义8位宽的线网

reg [7:0] reg_data; // 定义8位宽的寄存器

// 算术运算符示例

wire_data = 8'b1010 + 8'b0101; // 1010 + 0101 结果为 1111

// 逻辑运算符示例

reg_data = ~wire_data; // 取反操作

// 位运算符示例

reg_data = wire_data & 8'b1111; // 位与操作

endmodule

```

在上述代码中,我们展示了如何声明不同类型的信号并使用不同的操作符进行操作。此处的逻辑和位操作是基本的硬件描述语言概念,需要仔细理解才能在硬件设计中正确应用。

#### 2.1.2 模块和端口定义

模块是Verilog的基本单元,端口是模块与其他部分通信的接口。模块的定义通常包括输入、输出或双向端口的声明。

```verilog

module module_port_definition(

input wire [3:0] in_data, // 4位输入端口

output reg [3:0] out_data // 4位输出端口

);

// 模块内部逻辑定义

endmodule

```

在上述代码中,定义了一个模块`module_port_definition`,它有两个端口:一个是4位宽的输入端口`in_data`,另一个是输出端口`out_data`。端口的定义是模块化设计的基础,确保了模块的可重用性和可维护性。

### 2.2 测试平台的构建

#### 2.2.1 测试模块和激励生成

测试模块(testbench)是进行Verilog代码验证时没有端口的顶层模块,主要用于产生激励(激励信号)来测试待验证模块的行为。

```verilog

module testbench;

// 测试模块的信号定义

reg [3:0] stimulus;

// 激励生成

initial begin

stimulus = 4'b0000; // 初始化激励

#10; // 延时10时间单位

stimulus = 4'b1111; // 改变激励值

#10; // 延时10时间单位

// 其他激励序列的生成

end

// 测试结束

initial begin

#100; // 总延时100时间单位后结束测试

$finish; // 结束仿真

end

endmodule

```

测试模块通过`initial`块来生成激励序列,用于模拟输入信号随时间变化的场景。这个过程是验证设计是否符合预期的重要步骤。

#### 2.2.2 时钟和复位信号的处理

在数字设计中,时钟(clk)和复位(rst)信号是基本的控制信号,它们在测试平台中需要特殊处理,以模拟真实的工作环境。

```verilog

reg clk = 0;

reg rst = 0;

initial begin

forever #5 clk = ~clk; // 永远循环产生时钟信号,周期为10时间单位

end

initial begin

#20 rst = 1; // 20时间单位时产生复位信号

#5 rst = 0; // 25时间单位后取消复位信号

// 复位结束后产生其他控制信号

end

```

在此代码段中,通过`forever`循环产生周期性的时钟信号,复位信号通过一个`initial`块来控制,这为模块提供了初始化的机制。

#### 2.2.3 测试案例的组织结构

一个测试案例通常由多个测试用例组成,每个测试用例测试模块的一个特定功能或特性。测试案例的组织结构帮助设计者对测试用例进行管理。

```mermaid

graph LR

A[测试案例] --> B[测试用例1]

A --> C[测试用例2]

A --> D[测试用例3]

B --> E[预期结果]

C --> F[预期结果]

D --> G[预期结果]

```

在上述Mermaid流程图中,我们展示了测试案例与测试用例之间的关系,以及每个测试用例针对的预期结果。通过组织良好的测试用例,可以确保验证的全面性和有效性。

### 2.3 验证环境的组件

#### 2.3.1 驱动器(Driver)和监视器(Monitor)

驱动器和监视器是验证环境中两个重要的组件,它们分别负责产生激励和监视信号状态。

```verilog

module driver(

input clk,

input reset,

output reg [3:0]激励信号

);

// 产生激励的逻辑

endmodule

module monitor(

input clk,

input [3:0]监测信号

);

// 监视信号的逻辑

endmodule

```

在实际的验证环境设计中,驱动器和监视器需要与被测试模块通信,模拟真实的硬件交互过程。

#### 2.3.2 评分器(Scoreboard)和事务记录(Transaction Log)

评分器用于比较实际输出和预期输出,验证模块的功能是否正确。事务记录用于记录测试过程中发生的事务,便于后续分析。

```verilog

module scoreboard(

input clk,

input [3:0]期望输出,

input [3:0]实际输出

);

// 比较逻辑和结果记录

endmodule

module transaction_log(

input clk,

input [3:0]事务数据

);

// 事务记录逻辑

endmodule

```

这两个组件是验证环境不可或缺的部分,它们共同确保了验证过程的准确性和可追溯性。

在本章节的深入探讨中,我们了解了Verilog的基本语法,并搭建了一个基础的测试平台。我们还学习了如何组织测试案例,并对验证环境的核心组件有了初步的认识。在接下来的章节中,我们将继续深入学习验证方法论和实践案例,以及高级验证技术和策略。

# 3. 验证方法论和实践案例

## 3.1 功能覆盖率(Functional Coverage)

### 3.1.1 覆盖点(Coverpoints)和交叉覆盖(Crosses)

功能覆盖率是衡量验证充分性的一个重要指标,它衡量测试案例是否已经覆盖了设计中的所有功能点。在Verilog验证过程中,我们通常通过定义覆盖点(coverpoints)来跟踪这些功能点。覆盖点是设计中特定值或值范围的实例,它们代表了设计的关键行为。

```verilog

covergroup cg @(posedge clk);

cp_addr: coverpoint address {

bins low = { [0:15] };

bins high = { [1024:2047] };

}

cp_write: coverpoint write {

bins write_on = {1'b1};

bins write_off = {1'b0};

}

cross_cp_addr_write: cross cp_addr, cp_write;

endgroup

```

在上述代码中,我们定义了两个覆盖点`cp_addr`和`cp_write`,分别关注地址和写信号。然后我们定义了一个交叉覆盖(cross)点,它会同时关注地址和写信号的组合情况。这对于检查特定地址范围内写操作是否按预期执行特别有用。

### 3.1.2 覆盖率的收集和分析

收集覆盖率数据是验证过程的关键步骤。我们可以通过各种仿真工具提供的覆盖率收集功能来实现这一目标。分析这些数据有助于我们了解哪些设计部分已经充分测试,哪些部分还需要额外的关注。

```bash

% vcs -full64 -debug_all -sverilog -timescale=1ns/1ps -top module_top \

-cobertura coverage.xml -assert sva -P vcs.vlog089.rpt module.sv testbench.sv

```

上述命令示例用于在使用VCS仿真工具时,开启覆盖率收集,并生成覆盖率报告。使用这些工具输出的结果,我们可以生成详细的覆盖率报告,这些报告将包含诸如未覆盖的覆盖点和交叉覆盖项等信息。针对这些信息,我们可以编写额外的测试案例以提高覆盖率,直到达到我们的覆盖率目标。

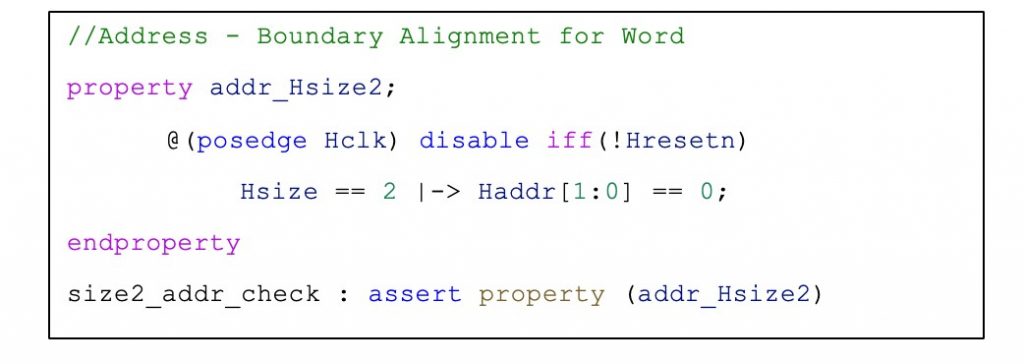

## 3.2 断言(Assertions)和属性(Properties)

### 3.2.1 硬件描述语言断言(HDL Assertions)

硬件描述语言断言(HDL Assertions)是一种在设计中直接嵌入的声明性语句,用于检查电路行为是否符合预期。在Verilog中,我们使用`assert`、`assume`、`cover`和`restrict`来表示不同类型的属性和断言。

```verilog

property p_read_after_write;

@(posedge clk) disable iff (!reset_n)

write |=> ##[1:10] read;

endproperty

assert pr

```

0

0