NAND Flash ECC算法与其他存储技术的融合:开创数据管理新篇章

摘要

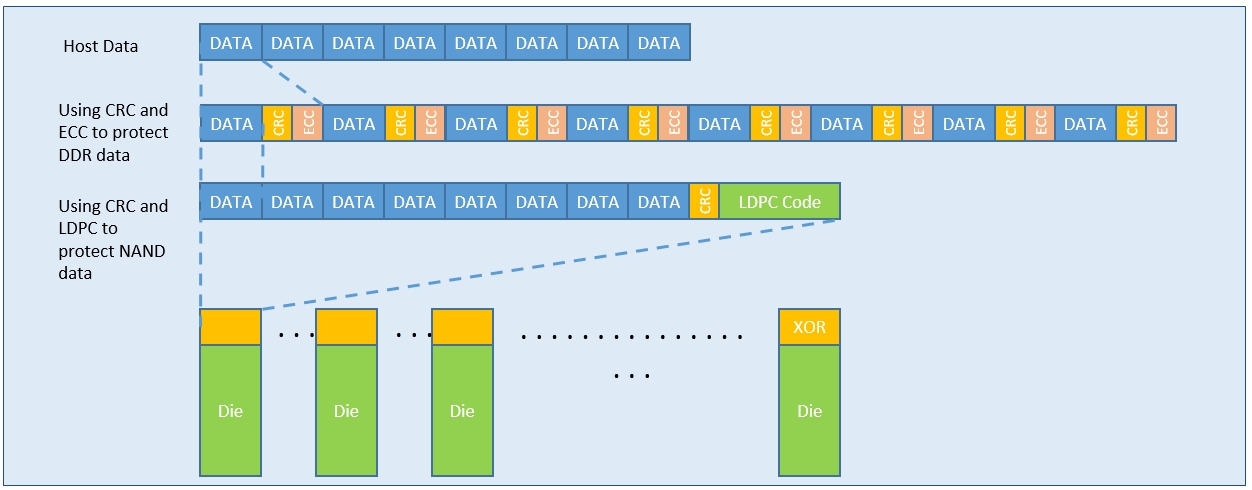

本文概述了NAND Flash存储技术的基础原理及其与ECC算法的结合应用。介绍了ECC算法的基础理论、实现方式,并探讨了其在NAND Flash存储系统中的具体应用案例。进一步分析了NAND Flash与其他存储技术如DRAM/SRAM和3D XPoint/RRAM的融合趋势及其对ECC算法的影响。文中还探讨了融合存储技术的架构设计、性能测试以及在云存储和大数据分析中的应用实例。最后,展望了未来数据管理技术的发展方向,包括新兴理念、数据存储需求变化及技术创新路径。

关键字

NAND Flash;ECC算法;存储技术融合;数据完整性;融合存储系统;数据管理技术

参考资源链接:NAND Flash ECC校验原理详解与实现策略

1. NAND Flash存储技术概述

在现代信息技术中,NAND Flash存储技术以其卓越的性能和应用范围,成为数据存储不可或缺的组成部分。NAND Flash是一种非易失性存储器,它能够在断电后依然保持存储数据的完整性,广泛应用于固态硬盘(SSD)、USB闪存驱动器和其他便携式存储设备中。

1.1 NAND Flash的工作原理

NAND Flash通过一种独特的浮栅晶体管结构来存储数据,这种结构允许每个晶体管存储一个或多个位。在NAND Flash中,数据以块(block)的形式进行读写,每个块包含多个页(page),页是读写操作的基本单位。读操作相对简单,直接访问相应的页即可;而写操作需要先擦除整个块,然后才能将新数据写入。

1.2 NAND Flash的特点与优势

与传统的NOR Flash相比,NAND Flash具有更高的存储密度和更低的生产成本。它的块结构设计使得读取速度快、写入效率高,非常适合存储大容量数据。此外,NAND Flash在擦除数据时的寿命有限,但现代NAND Flash通过各种算法和技术延长了其使用寿命,如垃圾回收和错误更正代码(ECC)。

NAND Flash的出现和普及,推动了数据存储领域的革新,也为未来存储技术的发展奠定了基础。随着技术的进步,NAND Flash正在向着更高的性能、更大的容量以及更长的使用寿命不断进化。

2. ECC算法的基础理论与实践

在现代数字世界中,数据的完整性和准确性至关重要。错误更正码(Error-Correcting Code,ECC)算法是保证数据可靠传输和存储的核心技术之一。这一章将深入探讨ECC算法的基础理论,并通过实践案例分析,展现其在NAND Flash存储技术中的应用。

2.1 ECC算法原理

2.1.1 ECC算法的基本概念

ECC算法是一种先进的错误检测与校正技术,它能够检测和纠正数据传输和存储过程中出现的错误。这一算法在确保信息无损交换方面发挥着关键作用,尤其在NAND Flash存储系统中,由于存储单元的物理特性,数据损坏和错误发生的概率相对较高,ECC算法就显得尤为重要。

2.1.2 ECC算法的数学基础

ECC算法的数学基础主要涉及有限域(也称伽罗华域)的代数结构和编码理论。一个简单的例子是汉明码,它使用奇偶校验位来检测和纠正单比特错误。更复杂的ECC算法,如里德-所罗门码(Reed-Solomon Code)和低密度奇偶校验码(Low-Density Parity-Check Code, LDPC),则基于有限域上的多项式运算和复杂的概率模型。

2.2 ECC算法的实现方式

2.2.1 硬件实现ECC的原理与方法

硬件实现ECC通常依赖于专用的集成电路(ASIC)或现场可编程门阵列(FPGA)。这些硬件模块被设计为能够高效地执行ECC算法中的数学运算。例如,在NAND Flash控制器中,内置的ECC单元可以实时地对写入存储器的数据进行编码,并在读取时执行错误检测与校正。

2.2.2 软件实现ECC的原理与方法

除了硬件实现外,ECC算法也可以通过软件来实现,尤其是在一些对成本敏感或者需要灵活性的应用场合。软件实现通常通过执行特定的算法在CPU上进行数学运算。虽然速度可能不如硬件实现快,但是通过优化算法和并行处理技术,可以提高效率。

2.3 ECC算法在NAND Flash中的应用案例分析

2.3.1 ECC算法在不同NAND Flash结构中的应用

NAND Flash的结构不同,对ECC算法的需求也不同。例如,SLC(Single Level Cell)存储器由于其较高的可靠性和较低的错误率,可能只需要基本的汉明码。而MLC(Multi Level Cell)和TLC(Triple Level Cell)存储器,则需要更加复杂的ECC算法来处理更高的错误率。在此背景下,LDPC和TLC结合的ECC实现方式,在高密度NAND Flash中越来越流行。

2.3.2 ECC算法性能评估与优化

对ECC算法进行性能评估和优化的关键在于找到错误检测和纠正能力、处理速度和资源消耗之间的最佳平衡点。例如,通过采用分层ECC策略,可以根据数据的重要性分配不同的保护级别。此外,通过算法优化和硬件加速,可以进一步提高ECC性能,减少对系统性能的影响。

graph LR

A[NAND Flash控制器] -->|数据传输| B(ECC模块)

B -->|编码| C[存储数据]

C -->|读取操作| D[检测错误]

D -->|发现错误| E[纠正错误]

E --> F[返回纠正数据]

在上述流程图中,可以看到ECC模块在NAND Flash控制器中的工作流程。数据在写入存储之前通过ECC编码,读取时经过错误检测和纠正,最后返回给用户纠正后的数据。

- 表格:不同ECC算法的性能对比

- | ECC算法 | 错误检测能力 | 纠错能力 | 资源消耗 | 处理速度 |

- |-------------|--------------|----------|----------|----------|

- | 汉明码 | 单比特错误 | 单比特 | 低 | 快 |

- | LDPC | 多比特错误 | 多比特