CMOS集成电路设计深度解析:拉扎维模型的精细化探索与应用

发布时间: 2024-12-19 01:38:31 阅读量: 2 订阅数: 4

拉扎维《模拟CMOS集成电路设计》习题答案(手写版)

# 摘要

CMOS集成电路设计是现代微电子领域的核心技术之一。本文从拉扎维模型的理论构建入手,系统性地探讨了该模型在模拟电路、数字电路以及混合信号电路设计中的实践应用。第二章详细介绍了拉扎维模型的数学基础和关键参数,第三章则着重分析了模型在不同电路设计中的具体应用案例,包括晶体管级电路仿真、滤波器和放大器设计、CMOS反相器优化及高速数字电路性能分析等。第四章对拉扎维模型进行了精细化的探索,包括高阶效应的模型拓展、模型参数提取的优化方法,以及新型器件中的模型应用。第五章讨论了模型在集成电路设计中的综合应用,关注仿真与验证流程、设计规则和可靠性分析,以及系统级芯片(SoC)的模型集成。最后,第六章展望了集成电路设计的未来趋势,分析了拉扎维模型面临的挑战,并提出了改进方向,强调了交叉学科在集成电路设计中应用的潜力。

# 关键字

CMOS集成电路;拉扎维模型;小信号分析;阈值电压;高速数字电路;SoC设计

参考资源链接:[模拟CMOS集成电路设计(拉扎维)答案](https://wenku.csdn.net/doc/6401ad00cce7214c316edecf?spm=1055.2635.3001.10343)

# 1. CMOS集成电路设计基础

集成电路(IC)的设计是现代电子技术的基石,而CMOS(互补金属氧化物半导体)技术由于其低功耗和高密度集成的特点,在这一领域占据着重要的地位。本章旨在为读者构建一个坚实的CMOS集成电路设计基础,涵盖从基本的CMOS工艺到电路设计的关键概念。

## 1.1 CMOS技术的演变

CMOS技术自从20世纪60年代被首次提出以来,已发展成为当今集成电路设计的主流技术。早期的CMOS工艺由于制造复杂和成本高而限制了其应用范围。然而,随着工艺技术的进步,特别是微米到纳米尺度的不断缩小,CMOS技术实现了更高速、更低功耗和更小尺寸的集成电路。

## 1.2 CMOS工艺中的关键组件

在CMOS工艺中,n型MOS(NMOS)和p型MOS(PMOS)晶体管是构成数字逻辑门的基本组件。NMOS晶体管在开启状态时具有较低的电阻,但其静态功耗相对较高。相对的,PMOS晶体管具有较低的静态功耗,但开启时的电阻较高。通过将NMOS和PMOS配对使用,可以在逻辑门中实现快速切换和低功耗特性。

## 1.3 CMOS设计中的重要考量

设计CMOS集成电路时,需要特别关注几个关键因素:功耗、速度、面积和可靠性。功耗直接关联到电池寿命和散热要求;速度则决定了电路的运行频率;面积涉及到集成电路的物理尺寸和集成度;可靠性则关系到器件长期运行的稳定性。为了优化这些因素,设计师必须采取精细的工艺调整和电路设计策略。

在后续章节中,我们将深入探讨CMOS技术中这些概念的实践应用和高级理论模型,从而为读者提供一个全面而深入的理解。

# 2. 拉扎维模型的理论构建

## 2.1 模型的数学基础

### 2.1.1 小信号分析方法

小信号分析是理解和建模CMOS集成电路的关键技术之一,因为它能够提供晶体管和电路在运行点附近的动态响应特性。小信号模型基于线性化技术,用以分析电路在直流偏置条件下的交流小信号特性。在数学上,小信号分析涉及对非线性器件或电路方程的线性近似处理,通常使用泰勒级数展开来实现这一点。

在CMOS集成电路中,小信号分析方法可以用来获得MOSFET的跨导(gm)和输出阻抗(r_d)等重要参数。这些参数对于设计稳定且高效的模拟电路至关重要。跨导反映了晶体管在小信号输入下的增益能力,而输出阻抗则表示了晶体管在小信号输出上的负载能力。

#### 数学描述

假设有一个非线性系统,其输出Y由输入X表示,即Y = f(X)。如果系统在X0处有一个工作点,则小信号扰动δX可以表示为:

δX = X - X0

系统的输出变化可以近似表示为:

δY ≈ (df/dX)|_(X=X0) * δX

其中,df/dX是函数f在X0处的导数,是小信号变化对输出Y变化的影响,可以看作是系统的增益。

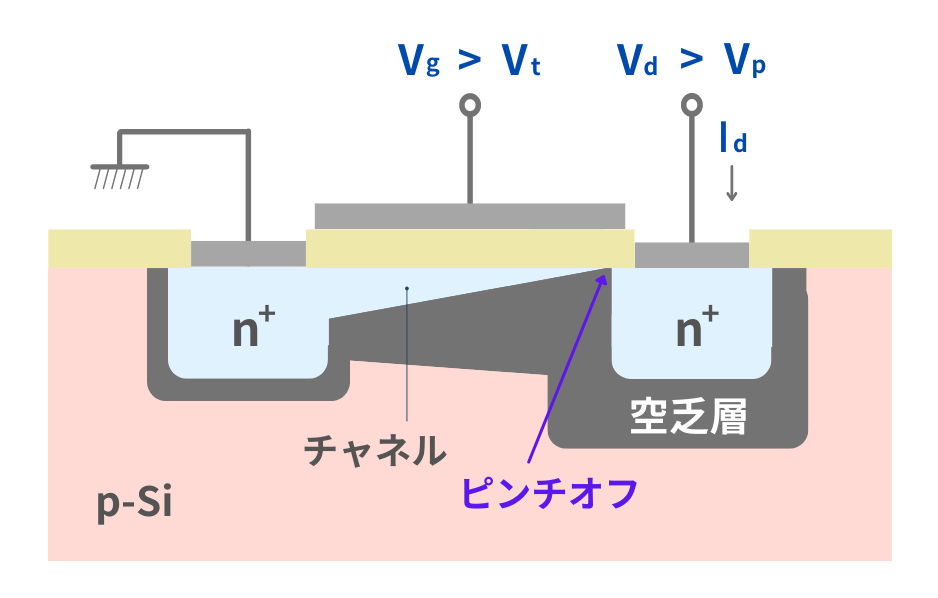

### 2.1.2 二极管和MOSFET的电流-电压特性

MOSFET(金属-氧化物-半导体场效应晶体管)是现代CMOS集成电路中的核心器件。其电流-电压(I-V)特性是理解和建模的基础。MOSFET具有两个主要工作区域:截止区和饱和区。截止区中,源极和漏极间几乎没有电流流动;而在饱和区中,漏极电流随着栅极电压的增加而增加。

#### 二极管模型

二极管是CMOS电路中另一个常见的非线性元件。其I-V特性可以使用肖特基方程来描述:

I = Is * (e^(qV/kT) - 1)

其中,I是电流,Is是反向饱和电流,V是电压,q是电子的电荷量,k是玻尔兹曼常数,T是绝对温度。

#### MOSFET模型

MOSFET的I-V特性更为复杂,但通常可以用以下方程来近似:

- 截止区:Id ≈ 0

- 线性区(非饱和区):Id = μn * Cox * (W/L) * (Vgs - Vth - Vds/2) * Vds

- 饱和区:Id = 1/2 * μn * Cox * (W/L) * (Vgs - Vth)^2

其中,Id是漏极电流,μn是电子迁移率,Cox是单位面积的栅氧电容,W和L分别是晶体管的宽度和长度,Vgs是栅源电压,Vth是阈值电压,Vds是漏源电压。

## 2.2 拉扎维模型的关键参数

### 2.2.1 阈值电压的提取方法

在设计MOSFET时,阈值电压Vth的准确提取至关重要,因为它决定了晶体管的开关特性。阈值电压不是一个固有值,而是会受到工艺偏差、电压和温度的影响。在CMOS设计中,通常使用体效应晶体管或采用专门的测试结构来测量Vth。

#### 提取步骤

1. **准备测试电路**:使用一个或多个晶体管构建一个特定的测试电路。

2. **设定直流条件**:给晶体管施加适当的栅极电压(Vg)和源极电压(Vs),使漏极电流(Id)最小化。

3. **测量I-V曲线**:缓慢增加栅极电压,同时测量漏极电流。记录漏极电流开始显著上升时的栅极电压值,这个电压值即为阈值电压。

在实际的电路设计中,阈值电压的提取可能需要考虑更多因素,比如体效应、亚阈值导电和短沟道效应等。因此,实际操作过程中可能需要使用更为复杂的模型来描述Vth与上述因素的关系。

### 2.2.2 迁移率模型和体效应

迁移率是描述载流子(电子或空穴)在半导体中移动速度的一个物理量。在MOSFET中,电子和空穴的迁移率对电流-电压特性有着显著的影响。体效应指的是晶体管的阈值电压会随着体极电压变化的现象,这主要是由于体极和沟道之间的耗尽层电容耦合。

#### 迁移率模型

在MOSFET中,载流子迁移率会受到电场强度和晶体管尺寸的影响。一个常见的模型表达式为:

μ = μ0 / (1 + θ * (Vgs - Vth))

这里,μ0是低场迁移率,θ是反映高场饱和效应的参数。

#### 体效应模型

体效应可以通过在阈值电压方程中添加一个体效应项来描述,即:

Vth = Vth0 + γ * ( sqrt( |2φF + Vsb| ) - sqrt( |2φF| ) )

其中,Vth0是零体偏置时的阈值电压,γ是体效应系数,φF是费米电位,Vsb是体极到源极的电压。

### 2.2.3 短沟道效应的数学描述

随着CMOS技术的不断进步,器件尺寸不断缩小,短沟道效应(SCE)成为影响MOSFET性能的重要因素。SCE指的是晶体管沟道长度减小导致的一系列非理想特性,包括阈值电压下降、亚阈值斜率变差等。

#### 短沟道效应模型

为了数学上描述短沟道效应,通常会在阈值电压的表达式中增加一项与沟道长度有关的参数。这样,新的阈值电压Vth可以写成:

Vth = Vth0 + γ * ( sqrt( |2φF + Vsb| ) - sqrt( |2φF| ) ) + ΔV

其中,ΔV是与沟道长度相关的项,代表短沟道效应引起的阈值电压变化。

## 2.3 模型在不同工艺节点的应用

### 2.3.1 工艺缩放对模型参数的影响

随着集成电路制造工艺的进步,特征尺寸不断缩小,旧的晶体管模型参数已经不能直接应用于更小的尺寸。因此,模型参数需要根据工艺缩放的规则进行调整。例如,高迁移率会受到更小特征尺寸的影响而下降,这要求模型在新工艺节点上做相应的调整。

#### 缩放规则

- 线性尺寸缩放:所有线性尺寸(如栅长L和栅宽W)按比例缩小。

- 电压缩放:由于电场强度的限制,电源电压也需要降低。

- 电流密度保持不变:为了保持热特性和可靠性,电流密度应保持不变。

### 2.3.2 特定工艺下的模型校准

模型校准是一个确保模型参数能准确反映实际物理器件行为的过程。模型校

0

0