C++内存管理揭秘:结构体内存布局优化技巧

发布时间: 2024-10-22 01:49:12 阅读量: 35 订阅数: 19

C语言结构体与联合体的应用及其内存管理技巧

# 1. C++内存管理基础

在编程中,内存管理是一项基础而至关重要的任务。C++作为一种高性能语言,它赋予了程序员对内存的控制权,也相应地增加了管理内存的复杂性。本章将介绍C++内存管理的基础知识,为后续章节中深入探讨结构体内存布局、内存布局优化技巧以及内存模型等内容打下坚实的基础。

首先,我们需要理解C++中内存管理的几个核心概念,如堆(heap)、栈(stack)、静态内存分配和动态内存分配。栈内存分配由编译器自动管理,速度快但空间有限;堆内存则需要程序员手动分配和释放,更加灵活但也容易出错。

```cpp

int var = 0; // 栈内存分配

int* ptr = new int(10); // 堆内存分配

delete ptr; // 需要程序员手动释放堆内存

```

然后,我们将探讨C++中内存分配的两个主要函数:`new`和`delete`,以及它们的重载形式。掌握这些函数的使用和它们在内存管理中的重要性,对于写出高效且安全的C++代码至关重要。

```cpp

int* arr = new int[10]; // 动态数组分配

delete[] arr; // 使用delete[]来释放动态数组

```

通过本章的学习,读者将对C++的内存管理有一个基本的了解,为进阶学习其他相关章节内容奠定基础。在后续章节中,我们将深入探讨C++内存管理的更多细节,并掌握高级内存优化技巧。

# 2. 结构体的内存布局

## 2.1 内存对齐的概念和影响

### 2.1.1 对齐的原因和规则

在C++中,内存对齐是指数据类型在内存中存储的起始地址必须是其大小的整数倍。这种做法在硬件层面是由处理器的架构所决定的,目的是为了提高访问内存的效率。如果数据没有对齐,处理器访问这些数据时可能需要执行额外的指令或操作,从而导致性能下降。

对齐规则因数据类型的大小以及目标平台的处理器架构不同而有所不同。例如,一个简单的规则是,双字节类型(如`short`)的起始地址应为2的倍数,而四字节类型(如`int`或`float`)的起始地址应为4的倍数。更复杂的结构体或类类型的对齐规则,将考虑其所有成员变量的最大对齐需求。

在不同的平台和编译器上,内存对齐的默认设置可能会有所不同。例如,在x86架构上,默认对齐通常是按照自然边界对齐,而在某些嵌入式系统或ARM架构上,默认对齐可能更为严格。

### 2.1.2 对齐对性能的影响

内存对齐对程序性能的影响主要体现在数据访问的效率上。处理器在读取或写入对齐的数据时速度更快,因为它们可以一次性完成操作,无需拆分成多个周期进行。而不对齐的数据可能会触发异常,处理器需要先进行数据对齐处理,然后再进行读取或写入操作,这就增加了额外的时间开销。

在一些现代处理器上,对齐的优化效果可能没有那么显著,因为它们设计了专门的硬件来处理未对齐的数据访问。然而,良好的内存对齐仍然能带来微小的性能提升,并且在内存有限的嵌入式系统中,对齐可以减少内存的浪费,从而提升程序的可维护性。

## 2.2 结构体内存布局的控制

### 2.2.1 使用pack关键字控制内存对齐

在C++中,可以通过特定的编译器指令来控制结构体的内存对齐。许多编译器都提供了`pack`关键字或类似的机制来实现这一点。`pack`关键字允许开发者指定对齐大小,通常可以设置为1字节,以取消所有默认的对齐规则。

下面是一个使用`pack`关键字来控制结构体内存对齐的示例:

```cpp

#pragma pack(push, 1) // 将对齐设置为1字节

struct alignas(1) UngangedData {

char c;

int i;

};

#pragma pack(pop) // 恢复之前的对齐设置

```

在这个例子中,`#pragma pack(push, 1)`指令告诉编译器将内存对齐设置为1字节,紧接着的结构体`UngangedData`中的所有成员都将被存储在一个字节边界上。最后,`#pragma pack(pop)`恢复了之前的对齐设置。

使用`pack`关键字或类似的指令时要非常小心,因为过度地进行内存压缩可能会引起性能问题,特别是在复杂的数据结构中,可能会导致缓存未命中率上升。

### 2.2.2 对齐属性的实践经验

控制内存对齐是C++内存管理中的一种高级技术。在实际应用中,开发者需要仔细评估是否需要手动对齐内存,因为不当的对齐可能会导致意外的副作用,如未定义行为。

一些经验教训包括:

- 只有在确实需要优化性能或减少内存占用时才使用内存对齐控制。

- 在多平台环境中,应避免使用特定平台的对齐特性,以保持代码的可移植性。

- 在对齐后进行性能测试,确保优化是有效的。

- 使用编译器内置函数或类型属性来控制对齐,而不是使用平台依赖的指令,如`pack`。

- 记录和文档化对齐的代码,确保团队成员理解其影响和限制。

通过合理的实践和严格的测试,开发者可以有效地利用内存对齐来提高程序性能,或者优化特定的数据密集型应用中的内存使用。

# 3. 内存布局优化技巧

内存布局优化是C++性能调优中的一个重要方面,它不仅仅关注内存使用的总量,还涉及数据在内存中的存储方式,以及如何有效地进行内存访问。这种优化策略可以大幅度提高程序的运行效率,特别是在资源受限的环境下,优化内存布局显得尤为重要。

## 3.1 减少内存占用的策略

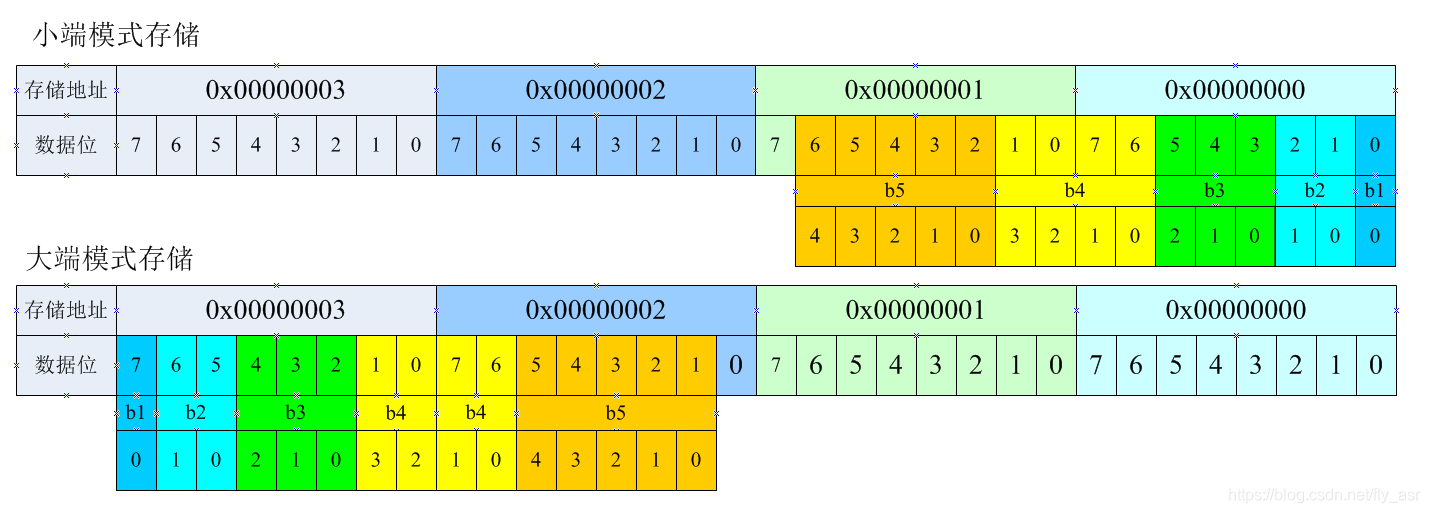

### 3.1.1 使用位域优化空间

位域是一种用较少的内存存储数据的方式,它通过在结构体内部定义位宽小于或等于一个字节的成员变量来实现。位域的使用可以减少内存的使用量,特别是在需要存储大量布尔值或者其他只有少量离散状态的数据时。

```cpp

struct Data {

unsigned int is_valid : 1; // 使用1位存储一个布尔值

unsigned int value : 7; // 使用7位存储一个整数

};

```

在上述代码中,`Data`结构体使用了位域,它总共只需要1个字节的空间,而不是通常的4或8字节。但是,位域的使用有一些限制。位域的声明只能是整型或枚举类型,它们不能是类类型,并且位域变量的访问可能会引入非对齐访问的问题。

### 3.1.2 压缩数据表示

压缩数据表示的技巧包括使用变长编码(如Huffman编码)和静态表(如变种的Unicode编码)来减少数据的存储空间。这种优化方式尤其适用于处理大量文本数据或网络通信。

假设我们有如下的ASCII字符分布:

```text

字符 'e' 出现频率 15%

字符 't' 出现频率 10%

字符 'a' 出现频率 8%

```

我们可以用更少的位来表示出现频率高的字符,从而压缩数据:

```cpp

// 简化的字符频率表

enum class CharCode : unsigned char {

CHAR_E = 0, // 'e' 只需要 1 位

CHAR_T = 1, // 't' 只需要 2 位

CHAR_A = 3, // 'a' 只需要 3 位

// 其他字符...

};

// 实际使用时的编码函数

std::string compress(const std::string& input) {

//...

return compressed_string;

}

```

压缩数据时,需要注意编码和解码的计算开销,以及是否所有场景都适合使用压缩。例如,在高速网络传输中,压缩可以减少带宽的使用,但在数据频繁读写的小型嵌入式系统中,压缩可能会降低性能。

## 3.2 提升内存访问效率的方法

### 3.2.1 利用缓存行对齐优化

现代处理器的缓存系统通常基于缓存行(cache line)的概念,这是内存中的一个固定大小的数据块,通常为64字节。当CPU从内存中读取数据时,它会一次性读取整个缓存行到缓存中。如果频繁访问的数据在内存中是随机分布的,就可能导致缓存行的失效,从而增加了内存访问的延迟。

```cpp

// 一个简单的类,展示如何进行缓存行对齐

#pragma pack(push, 1)

struct __attribute__((aligned(64))) AlignedData {

// ... 一些成员变量

};

#pragma pack(pop)

```

在这个例子中,`AlignedData`使用`__attribute__((aligned(64)))`来确保它在内存中对齐到64字节边界。通过这种方式,我们可以减少缓存行失效的几率,提升访问效率。

### 3.2.2 避免内存碎片和膨胀

在动态内存分配中,频繁的内存申请和释放可能会导致内存碎片的产生。内存碎片不仅占用更多的物理内存,还会增加内存分配和释放时的查找时间。

一个常见的解决策略是使用内存池,内存池是一种预先分配大块内存的技术,它可以将内存分配的开销降低到最小。此外,为了防止内存膨胀,我们应该尽量避免不必要的内存分配,使用对象池来复用对象,减少因频繁分配导致的内存碎片。

```cpp

// 简单的内存池示例

class MemoryPool {

public:

void* allocate(size_t size) {

// 内存分配逻辑

}

void deallocate(void* ptr) {

// 内存释放逻辑

}

private:

std::vector<char> pool; // 内存池

};

```

通过这种方式,内存池可以帮助我们管理内存的使用,减少内存碎片的产生。值得注意的是,内存池的设计要考虑到多线程环境下的线程安全问题,否则可能会导致资源竞争和数据损坏。

以上内容为第三章“内存布局优化技巧”的部分节选,接下来的章节内容会继续围绕内存布局优化展开,介绍更多高级技巧和实战案例。

# 4. 深入理解C++内存模型

C++的内存模型规定了多线程程序中变量访问的规则,以及不同操作之间的排序规则。C++11引入了新的内存模型特性,对于写出高性能的并发代码至关重要。这一章将深入探讨C++11内存模型的新特性,以及内存分配和释放的机制。

## 4.1 C++11中的内存模型新特性

### 4.1.1 原子操作和内存顺序

C++11引入了`std::atomic`类型和一系列的原子操作,让开发者可以编写出无锁的并发程序。原子操作保证了在并发执行时,操作是不可分割的,即在任何时刻都不可能被其它线程观察到操作的中间状态。

此外,C++11还提供了`std::memory_order`枚举,它允许程序员指定操作的内存顺序。这些顺序包括`memory_order_relaxed`、`memory_order_acquire`、`memory_order_release`、`memory_order_acq_rel`和`memory_order_seq_cst`,它们分别用于定义不同的操作顺序约束。

例如,考虑以下代码:

```cpp

std::atomic<int> x, y;

std::atomic<bool> z;

x.store(10, std::memory_order_relaxed);

y.store(20, std::memory_order_relaxed);

z.store(true, std::memory_order_release);

if (z.load(std::memory_order_acquire)) {

assert(x.load(std::memory_order_relaxed) == 10);

assert(y.load(std::memory_order_relaxed) == 20);

}

```

在这段代码中,如果`z.load`返回`true`,那么我们可以确定`x`和`y`已经被某些线程设置过了。由于`z`是用`memory_order_release`存储的,并且`x`和`y`是用`memory_order_relaxed`存储的,我们不能保证`x`和`y`的读取会发生在`z`的读取之前。但是,我们能够保证,如果`z`的读取返回`true`,那么`x`和`y`在之前的某个点已经被设置了。

### 4.1.2 内存模型对性能的影响

内存顺序和原子操作的选择对程序的性能有着直接的影响。使用更严格的内存顺序通常意味着需要更多的同步和CPU资源,而宽松的内存顺序可能会导致数据竞争或者状态不一致。

考虑下面两个不同内存顺序的比较:

```cpp

std::atomic<int> x;

void foo()

{

x.store(1, std::memory_order_release); // 编译器可能有优化空间

}

void bar()

{

int n = x.load(std::memory_order_acquire);

// 根据x的值做一些操作...

}

```

在这个例子中,`store`操作使用了`memory_order_release`,而`load`使用了`memory_order_acquire`。这种组合意味着`bar`函数中的操作会在`x`存储新值之后发生,并且编译器可能无法对`foo`函数中的代码进行某些优化。如果改为`memory_order_relaxed`,则`foo`函数中的代码可能会有更多的优化空间,但同时也增加了程序的复杂性和出错的可能性。

## 4.2 内存分配和释放的深入探讨

### 4.2.1 内存池的原理和应用

内存池是一种预先分配一块大内存块,并在其中创建多个小块供程序使用的技术。内存池可以减少内存分配和释放的次数,有效降低内存碎片化,并提升内存分配速度。

内存池的关键特性包括:

- 预分配大块内存,减少系统调用。

- 内存复用,减少内存浪费。

- 快速分配,提高效率。

下面是一个简单的内存池实现示例:

```cpp

#include <iostream>

#include <vector>

class SimpleMemoryPool {

private:

std::vector<char> buffer; // 存储内存块

size_t object_size; // 单个对象大小

char* next; // 下一个可用内存位置

public:

explicit SimpleMemoryPool(size_t objectSize)

: object_size(objectSize), next(nullptr) {

buffer.reserve(1024 * objectSize); // 预分配一定大小的内存块

next = buffer.data(); // 初始化下一个可用内存位置

}

void* allocate() {

if (next + object_size <= buffer.data() + buffer.size()) {

void* result = next;

next += object_size;

return result;

} else {

return nullptr; // 内存池耗尽

}

}

void deallocate(void* ptr) {

// 在这个简单的实现中,我们不实际回收内存,但可以记录它以便以后复用

}

};

int main() {

SimpleMemoryPool pool(sizeof(int));

int* x = static_cast<int*>(pool.allocate());

*x = 42;

std::cout << "Allocated int: " << *x << std::endl;

pool.deallocate(x);

return 0;

}

```

### 4.2.2 智能指针的内存管理

智能指针是C++11中引入的一个特性,用于自动管理资源的生命周期。最常用的智能指针包括`std::unique_ptr`、`std::shared_ptr`和`std::weak_ptr`。它们的主要优势在于能够自动释放所管理的资源,从而减少内存泄漏的风险。

智能指针的使用减少了手动管理内存的需要,但是开发者需要理解每种智能指针的工作方式和最佳实践。例如:

```cpp

#include <memory>

void use_count_example() {

std::shared_ptr<int> sp1(new int(10)); // 创建一个shared_ptr,计数为1

std::shared_ptr<int> sp2 = sp1; // sp2与sp1共享对象,计数变为2

std::shared_ptr<int> sp3 = sp2; // sp3共享,计数变为3

// sp3析构,计数减1变为2

{

std::shared_ptr<int> sp4 = sp2; // sp4共享,计数变为3

} // sp4析构,计数减1变为2

// sp2析构,计数减1变为1

sp1 = nullptr; // sp1放弃对象所有权,计数减1变为0

// sp3析构,计数减1变为0,由于计数为0,资源被释放

}

```

在上面的代码中,`sp1`、`sp2`和`sp3`共享同一个对象,它们的使用计数分别反映了当前有多少个`shared_ptr`对象管理着该资源。只有当最后一个`shared_ptr`对象被销毁时,资源才会被实际释放。

智能指针的内存管理避免了常规指针操作中常见的错误,例如忘记释放内存或在对象的生命周期内释放了内存。但同时,智能指针也不是万能的,开发者仍需留意循环引用、异常安全等高级内存管理问题。

# 5. 结构体内存优化的实战演练

## 5.1 常见数据结构的内存优化

### 5.1.1 链表和树结构的内存布局

在C++中,链表和树结构是两种常见的数据结构,它们在内存中的布局对于性能有着直接的影响。在深入探讨具体的内存优化策略之前,我们首先需要理解它们的标准内存布局及其潜在问题。

链表是一种线性数据结构,每个节点通常由数据部分和指向下一个节点的指针组成。在内存中,这些节点通常是非连续存储的,因为节点是动态分配的。这就意味着,链表的内存布局是高度依赖于节点分配的,这可能导致频繁的内存分配操作和大量的内存碎片。

```cpp

struct ListNode {

int value;

ListNode* next;

};

```

而在树结构中,节点除了可能包含数据外,还包含指向其他子节点的指针。对于二叉树、B树或其他复杂树结构,节点数量和布局的优化可能会更加复杂。在内存中,树节点布局通常也是非连续的,但它们的访问模式往往更加复杂,这要求我们对内存布局进行仔细的设计,以便快速访问和有效利用缓存。

树节点的一个简单例子如下:

```cpp

struct TreeNode {

int data;

TreeNode* left;

TreeNode* right;

};

```

为了优化这些数据结构的内存使用,开发者可以采取以下几种策略:

- 使用对象池来减少频繁的动态内存分配。

- 利用特定编译器指令或属性实现更紧致的内存对齐。

- 将小的树节点合并为一个大的数组,从而实现更好的缓存利用。

### 5.1.2 堆和栈的内存分配对比

在内存优化中,理解堆(Heap)和栈(Stack)的内存分配是基础。栈上的内存分配速度要远快于堆,因为它的管理由编译器自动完成,而堆内存分配涉及到更复杂的操作系统调用。

栈内存分配具有以下特点:

- 内存分配和回收是自动的,遵循后进先出的原则。

- 栈内存分配速度快,因为它不需要复杂的内存管理机制。

- 栈空间有限,对于大型数据结构或者需要长期存储的数据,栈内存不是最佳选择。

堆内存分配则有如下特点:

- 内存分配和回收需要开发者显式管理,或依赖智能指针等机制。

- 堆内存可以非常大,适用于动态分配的对象。

- 堆内存分配速度相对较慢,因为需要从操作系统层面进行管理。

由于栈和堆的这些差异,在设计数据结构时,应尽量利用栈上的局部变量来存储临时数据,而对于那些需要长期存活或者生命周期不确定的对象,则可以考虑使用堆内存。另外,在实现复杂数据结构如自定义链表和树时,开发者也可以尝试实现自己的内存分配器来优化性能,比如为树的每个节点分配一个固定大小的内存块。

```cpp

void* allocate_node(size_t size) {

void* node = malloc(size); // 从堆上分配内存

return node;

}

void deallocate_node(void* node) {

free(node); // 释放内存

}

```

在实际应用中,对于内存的管理应当考虑到对象的生命周期、大小以及访问模式等因素,选择合适的内存分配策略以达到优化的目的。

## 5.2 编译器优化选项的分析

### 5.2.1 不同编译器选项对性能的影响

C++编译器提供了众多的优化选项,它们可以显著影响最终生成的代码的性能。理解并合理运用这些编译器优化选项,对于内存优化至关重要。

以下是一些常见的编译器优化选项及其影响:

- **-O1, -O2, -O3**: 这些是GCC和Clang编译器提供的优化级别选项。随着优化级别增加,编译器会执行更多的优化策略,包括循环展开、函数内联等,以减少程序的运行时间和提高性能。

- **-Os**: 优化选项专注于减少程序的大小。它会尝试减小代码体积,尽管可能牺牲一些运行速度。

- **-Ofast**: 这是较高级别的优化选项,不仅包括-O3的优化,还可能包括那些可能改变程序数学计算行为的优化。

使用不同的优化级别对内存的影响:

- **-O2** 和 **-O3** 可能会改变对象的内存布局,例如通过调整数据对齐来减少缓存未命中的情况,或是通过函数内联来减少函数调用开销。

- **-Os** 在减小程序大小的同时,可能会改变数据结构的内存对齐,从而影响内存访问的效率。

```bash

g++ -O2 -c your_file.cpp # 使用O2优化级别编译

```

### 5.2.2 优化内存布局的编译器指令

编译器指令可以对内存的布局产生直接的影响,使用得当,可以优化程序性能。例如,`#pragma pack` 指令可以控制结构体成员之间的对齐方式,从而影响内存布局。

```cpp

#pragma pack(push, 1) // 设置对齐为1字节

struct PackedStruct {

char a;

int b;

char c;

};

#pragma pack(pop) // 恢复之前的对齐设置

```

通过这种方式,我们可以减少数据结构的内存占用,但需要注意的是,过度压缩内存布局可能会影响CPU的缓存利用率,因此需要在内存占用和性能之间找到平衡点。

除了`#pragma pack`,许多编译器还支持其他内存优化相关的指令,比如GCC的`__attribute__((aligned(N)))`用于指定对象的对齐方式。合理利用这些编译器指令,可以帮助我们设计出更高效的数据结构,特别是在需要严格控制内存布局的嵌入式系统中。

```cpp

struct alignas(8) AlignedStruct {

int a;

double b;

};

```

在实战中,开发者应该根据实际应用场景和需求选择合适的编译器优化选项和内存布局控制指令,测试各种组合对程序性能的影响,以达到最佳的内存优化效果。

# 6. 未来C++内存管理的发展趋势

随着技术的不断进步和硬件的发展,C++内存管理也在不断地进化。在C++20及未来的版本中,内存管理领域有哪些新的特性和优化方向?本章将带你一览未来C++内存管理的发展趋势,并探讨如何为未来进行内存管理优化的准备工作。

## 6.1 C++20及未来版本的展望

### 6.1.1 新特性的介绍和分析

C++20引入了几个重要的内存管理相关的特性,包括但不限于概念(Concepts)、协程(Coroutines)、范围库(Ranges)等。其中概念是通过模板参数对类型进行更严格的约束,这使得在编译时就能够对类型进行更多的检查,减少运行时错误。协程提供了一种更高级别的并发编程模式,它将允许我们以更简洁和直观的方式处理异步操作,这无疑将对内存使用模式产生影响。

```cpp

// 示例代码:概念(Concepts)的简单使用

template <typename T>

concept Addable = requires(T a, T b) {

a + b; // 要求类型T支持加法操作

};

template <Addable T>

T add(T a, T b) {

return a + b;

}

```

在C++20中,范围库(Ranges)的概念也引入了新的迭代器模式,这可能会改变我们对算法、容器和迭代器的理解。范围库与概念和协程结合,可能带来内存使用的变革。

### 6.1.2 如何为未来做内存管理优化的准备

为了适应C++20及未来版本中可能出现的内存管理变革,开发者需要提前做好准备。首先,学习和理解新特性的基本原理和使用方法是基础。例如,通过学习概念(Concepts)来加强对编译时类型检查的了解,以便编写更安全的代码。其次,关注社区中关于新特性的讨论和最佳实践,这些将有助于我们及时调整和优化代码。最后,通过实践新特性进行小型项目尝试,以实际经验来适应未来的变化。

## 6.2 跨平台内存管理策略

### 6.2.1 不同操作系统下的内存管理差异

不同的操作系统有着不同的内存管理机制和API,例如Windows、Linux和macOS在内存分配、内存映射等方面有着各自的特点。在跨平台应用中,开发者需要对这些差异有所了解,并通过抽象层或者条件编译等方法,实现统一的内存管理接口。这种策略不仅有助于保持代码的一致性,而且能够使应用更好地适应不同平台的特性。

```cpp

// 条件编译示例:不同平台内存分配的抽象

#if defined(_WIN32)

// Windows平台内存分配代码

void* allocate(size_t size) {

return HeapAlloc(GetProcessHeap(), 0, size);

}

#else

// Unix-like平台内存分配代码

void* allocate(size_t size) {

return malloc(size);

}

#endif

```

### 6.2.2 跨平台库设计中的内存管理考量

在设计跨平台库时,内存管理是一个重要的考量因素。为了确保库的高效和稳定,需要充分考虑到不同平台上的内存分配策略、内存对齐规则以及内存访问权限等问题。一个常见的做法是提供一个内存管理器的接口,允许在不同平台上实现具体的内存管理策略。此外,内存泄漏检测工具和内存使用分析工具的选择也需考虑到跨平台的兼容性和功能性。

在未来的C++内存管理中,预计将会出现更多针对特定场景的优化特性和工具。作为开发者,要紧跟技术潮流,不断学习和实践新工具和新方法,以适应未来更高效、更智能的内存管理需求。

0

0