【UVM环境复用与封装】:打造灵活可扩展的验证平台策略

发布时间: 2024-12-15 19:56:23 阅读量: 3 订阅数: 6

uvm-1.1.zip_IC验证_IC验证资料_UVM_uvm 1.1d_uvm平台

参考资源链接:[绿皮书system verilog验证平台编写指南第三版课后习题解答](https://wenku.csdn.net/doc/6459daec95996c03ac26bde5?spm=1055.2635.3001.10343)

# 1. UVM基础知识回顾

## UVM简介

UVM (Universal Verification Methodology) 是一种由SystemVerilog语言实现的面向对象的验证方法学,它提供了一整套用于构建可复用、可扩展的验证环境的机制和规则。UVM的出现极大地简化了复杂设计的验证流程,提高了验证效率。

## UVM的组成

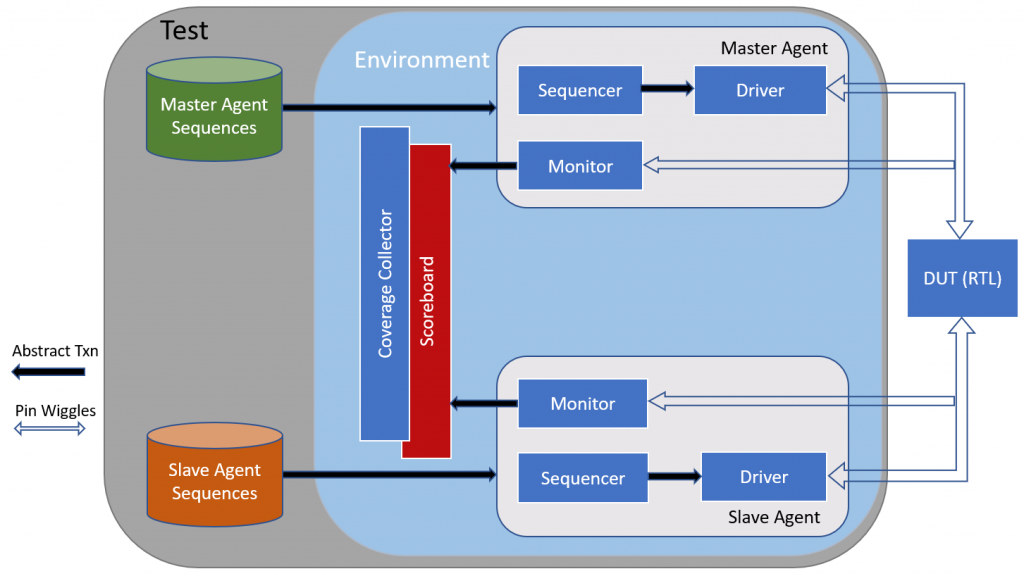

UVM验证环境主要由以下几部分组成:

- **组件(Components)**: 包括uvm_driver, uvm_monitor, uvm_agent等。

- **序列(Sequences)**: 用于产生激励的机制。

- **环境(Environment)**: 将各个组件组合起来形成完整的验证环境。

- **测试(Tests)**: 在不同的测试用例中,驱动环境执行各种操作。

## UVM工作原理

UVM利用事件驱动的方式进行通信,它继承了SystemVerilog的类层次结构。UVM通过一系列的宏定义、配置对象和验证组件,允许验证工程师在不同层次上进行配置和控制,实现了高度的灵活性和可扩展性。例如,使用`uvm_do`宏可以自动产生随机化的序列项,使用`uvm_config_db`可以传递参数给各个组件。

# 2. UVM环境复用的重要性与策略

### 2.1 理解UVM环境复用的需求

UVM环境复用需求的分析对于任何致力于提高验证效率和验证覆盖率的团队来说都是至关重要的。随着项目变得越来越复杂,对于能够快速适应新的设计和验证需求的灵活验证环境的需求变得愈发明显。

#### 2.1.1 验证项目复用的需求分析

在现代芯片设计的背景下,验证项目往往需要复用以节省时间并提升效率。以下是一些关键的需求:

- **时间效率:** 快速启动新的验证项目,不必从零开始。

- **资源优化:** 利用现有资源,减少人力和物理资源的浪费。

- **维护简便:** 提高验证环境的可维护性,便于后期的升级和维护。

- **覆盖一致:** 保证验证环境复用后,覆盖模型的一致性。

- **验证质量:** 避免因重复劳动导致的潜在错误,提高验证质量。

#### 2.1.2 UVM环境复用的优势

UVM环境复用的优势体现在多个方面,具体包括:

- **提高验证效率:** 环境复用可以极大地缩短验证准备时间。

- **促进标准开发:** 通过复用,可以建立和推广一套标准化的验证组件库。

- **增强可维护性:** 设计环境时考虑复用,可使环境更加模块化,易于维护。

- **扩展性强:** 随着项目需求变化,已复用的环境可以轻松扩展。

- **提升覆盖率:** 借助已经经过充分测试的环境,可以快速提高新项目的测试覆盖率。

### 2.2 UVM环境复用的设计原则

有效的UVM环境复用策略需要基于一系列设计原则。这些原则帮助验证工程师确保复用环境能够适用于不同的项目需求。

#### 2.2.1 可重用性设计

可重用性设计是指在设计UVM组件时考虑到未来可能的复用需求,这涉及以下几个方面:

- **定义清晰的接口:** 确保组件接口是明确且容易理解的。

- **模块化:** 构建模块化的组件,使每个部分都能独立工作。

- **灵活性:** 设计时预留适当的接口和参数,以适应不同的应用场景。

#### 2.2.2 抽象与封装的应用

抽象与封装是提高复用性的关键。通过以下方式应用这两个原则:

- **抽象:** 抽象使得用户无需关心内部实现细节,只需要理解其功能。

- **封装:** 封装确保组件的内部状态不被外部直接访问和修改,从而提供稳定的接口。

#### 2.2.3 可配置性的实现

可配置性是复用的重要组成部分,它允许用户通过改变参数来适应不同的测试需求。

- **参数化设计:** 设计时使用参数化代码,提供配置文件来调整组件行为。

- **灵活的配置管理:** 支持多层次的配置选项,包括环境级别的配置。

### 2.3 UVM环境复用的实践案例分析

为了更好地理解UVM环境复用的概念,我们将深入分析几个具体案例。

#### 2.3.1 复用案例一:参数化驱动

参数化驱动允许用户通过修改参数来适应不同的测试需求,从而实现复用。例如,一个驱动组件可能需要根据不同的设计进行调整,通过引入参数来控制其行为。

```mermaid

graph TD;

A[开始参数化驱动设计] --> B[定义驱动行为参数]

B --> C[实现参数化逻辑]

C --> D[提供配置接口]

D --> E[通过配置文件调整参数]

```

```verilog

// 代码块:参数化驱动的Verilog示例

class parameterized_driver extends uvm_driver;

// 参数声明

parameter DATA_WIDTH = 8;

virtual interface my_if my_vif; // 接口

// 构造函数

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

// 驱动数据

virtual task run_phase(uvm_phase phase);

bit [DATA_WIDTH-1:0] data;

forever begin

// 通过配置接口获取数据宽度参数

my_vif.get_data(data);

// 驱动逻辑...

end

endtask

endclass

```

#### 2.3.2 复用案例二:框架级别的复用

框架级别的复用涉及利用可复用的框架来快速搭建测试环境。比如,可以设计一个通用的UVM测试序列,通过不同的配置文件来生成针对特定设计的测试。

```mermaid

graph TD;

A[开始框架级别复用设计] --> B[定义通用测试序列]

B --> C[创建配置管理接口]

C --> D[实现特定设计的配置文件]

D --> E[通过通用框架生成测试]

```

```systemverilog

// 代码块:框架级别的复用的SystemVerilog示例

class my_test extends uvm_test;

`uvm_component_utils(my_test)

my_env my_env_h;

my_sequence my_sequence_h;

// 构造函数

function new(string name = "my_test", uvm_component parent = null);

super.new(name, parent);

endfunction

// 序列配置和启动

virtual task run_phase(uvm_phase phase);

phase.raise_objection(this);

// 创建并配置序列

my_sequence_h = my_sequence::type_id::create("my_sequence_h");

my_sequence_h.start(my_env_h.agent_h.seqr_h);

phase.drop_objection(this);

endtask

endclass

```

通过这些案例,我们可以看到UVM环境复用不仅仅是代码级别的重用,更是设计思路和验证方法上的复用。这些实践案例突出了UVM环境复用的核心优势,同时也展示了如何根据实际项目需求灵活运用

0

0