【eMMC 5.1速度与带宽】:JEDEC文档揭示的传输速率革命

发布时间: 2024-12-14 11:23:48 阅读量: 89 订阅数: 26

emmc5.1 JEDEC官方Spec文档原版带目录

参考资源链接:[官方EMMC5.1规范文档:JESD84-B51详解](https://wenku.csdn.net/doc/7dt0yhbxg8?spm=1055.2635.3001.10343)

# 1. eMMC技术概述

## 1.1 eMMC技术简介

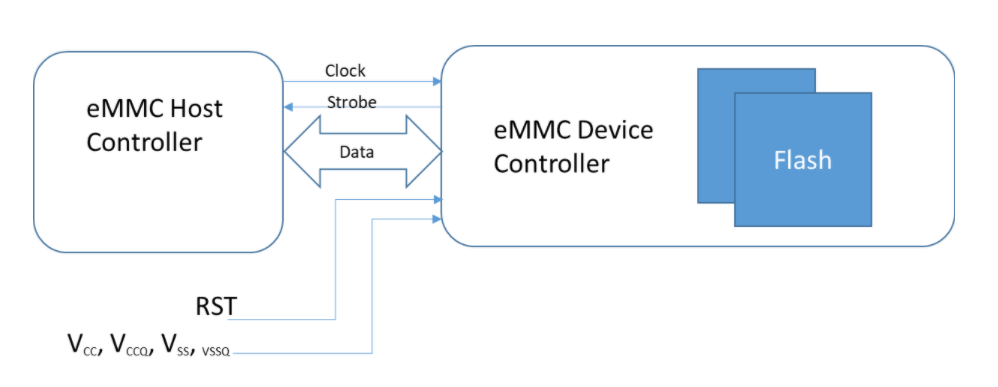

eMMC(嵌入式多媒体卡)是一种广泛应用于移动设备的闪存存储解决方案,它将闪存存储器和闪存控制器集成在一个小型的封装内。相比其他存储技术,eMMC具有尺寸小、性能稳定、易于设计等特点,成为多数智能手机、平板电脑以及便携式电子设备的首选存储介质。

## 1.2 eMMC的发展历程

eMMC技术自2007年推出以来,已经经历了多个版本的迭代,其标准不断更新以适应存储需求的日益增长。目前,市场上主流的eMMC标准为eMMC 5.1,它在速度、可靠性和功耗管理等方面做出了显著的改进。

## 1.3 eMMC与行业标准组织JEDEC

eMMC标准由JEDEC固态技术协会定义,这是一个全球性的半导体行业标准组织,负责制定包括eMMC在内的存储技术规范。通过JEDEC的严格规范与测试,eMMC技术在兼容性、可靠性和性能上均得到了保障。

# 2. eMMC 5.1标准的核心特性

### 2.1 eMMC 5.1的速度提升机制

#### 2.1.1 高速接口HS400的工作原理

eMMC 5.1标准引入了HS400接口,这是一种高速接口,能够显著提升存储设备的读写速度。HS400工作在1.8V信号电平下,支持8位并行数据传输,并且能够以最高200MHz的频率进行数据交换。其工作原理基于DDR(Double Data Rate)技术,即在时钟信号的上升沿和下降沿都进行数据传输。这种双倍数据传输率大大提升了eMMC的性能。

HS400接口的实现依赖于eMMC控制器和嵌入式存储器(NAND Flash)的高效配合。控制器负责管理数据流向,包括缓存管理和错误校正编码(ECC),而NAND Flash则是存储数据的实际介质。HS400在物理层面上通常使用的是8位宽度的并行总线,这允许在每个时钟周期内发送和接收更多的数据。

#### 2.1.2 数据传输速率的理论基础

在评估eMMC 5.1的速度时,我们通常会关注其最大数据传输速率。理论上,一个频率为200MHz的接口,每个时钟周期持续5纳秒。如果使用DDR技术,那么每秒可进行200M次上升沿和200M次下降沿的数据传输,总共达到400M次传输。对于8位宽的数据总线,这意味着每秒可以传输高达3.2G字节的数据(8位 = 1字节,400M次 * 8位 = 3200M字节 = 3.2GB)。

然而,实际应用中,由于各种信号损耗、控制器处理速度和存储器响应时间的限制,实际的最大传输速率通常低于理论值。为了达到尽可能接近理论最大速率,需要对存储器芯片进行优化,比如使用更快的NAND Flash芯片,并通过精心设计的信号完整性优化措施来减少信号干扰,如信号复用、链路训练和自适应均衡等技术。

### 2.2 eMMC 5.1的带宽优化技术

#### 2.2.1 8位并行传输的优势

eMMC 5.1引入的8位并行传输技术,相较于早期版本的4位传输,能够提供更宽的数据带宽,从而实现更快的数据传输速率。8位传输意味着数据通道宽度是4位的两倍,因此在同一时钟频率下,8位通道可以传输的数据量是4位通道的两倍。

为了实现这一优势,eMMC 5.1的硬件设计必须考虑数据的同步和时序控制。如果数据在传输过程中不同步,将导致数据包碰撞和错误,从而降低性能。因此,控制器必须能够在接收到数据时准确地同步它们,并将其正确地组装成完整的信息。

#### 2.2.2 缓存大小与性能的关系

eMMC 5.1的性能也受到缓存大小的影响。缓存作为一种快速的临时存储空间,用来在eMMC和主系统之间进行数据交换。一个更大的缓存可以存储更多的数据,减少访问速度较慢的NAND Flash的次数,从而提高数据访问速率和整体性能。

然而,缓存的大小并不是越大越好,因为在特定的应用场景中,总是存在一个最优缓存大小。如果缓存过大,可能会导致数据的管理成本增加,使得缓存的利用率降低。为了找到最佳的缓存大小,需要综合考虑应用场景、NAND Flash的性能和成本等因素。

### 2.3 eMMC 5.1的信号完整性分析

#### 2.3.1 信号传输的噪声控制

eMMC 5.1设备在进行高速数据传输时,必须确保信号完整性。信号完整性指的是信号在传输过程中保持其质量和完整性的能力。高频率的信号传输容易受到电路板上的电磁干扰(EMI)影响,导致信号失真,最终影响传输速率和数据完整性。

为了控制噪声,需要在设计时采取多种措施,如使用多层PCB板,其中部分层专门用于为信号提供屏蔽保护,使用差分信号传输以减少干扰,以及增加信号端接以减少反射。此外,还可以采用先进的信号调制技术来提高信号的鲁棒性。

#### 2.3.2 信号完整性对性能的影响

信号完整性问题如果不加以妥善处理,会直接影响eMMC设备的性能。例如,信号的失真会导致数据错误,控制器需要通过重发来修正这些错误,这不仅增加了延迟,还可能降低吞吐量。信号完整性差还可能导致信号传输中断,从而造成设备性能的不稳定。

为了确保eMMC设备的高性能,必须进行严格的信号完整性和电磁兼容性(EMC)测试。测试一般包括:信号完整性分析、电磁干扰(EMI)测试、静电放电(ESD)测试等。确保通过这些测试后,eMMC设备在实际应用中才能表现出其设计上的性能优势。

以上所述,第二章内容为eMMC 5.1的核心特性做了深入的分析和解读。接下来,我们将探讨这些核心特性如何在现代设备中得以应用。

# 3. eMMC 5.1标准与实践应用

## 3.1 eMMC 5.1在现代设备中的应用

### 3.1.1 智能手机与平板

eMMC 5.1作为嵌入式存储解决方案的黄金标准,广泛应用于现代智能手机和平板电脑中。随着高清视频和大型应用程序的需求增长,对eMMC存储的要求也越来越高。eMMC 5.1因其高性能、可靠性和小型化设计成为设备制造商的首选。在智能手机中,eMMC 5.1不仅提高了系统的启动速度和数据传输速率,而且有助于设备更快地访问和处理数据,从而提升用户体验。例如,快速的相机启动时间和短的文件保存时间,使得用户能够在几秒钟内记录和分享高质量的照片和视频。

### 3.1.2 可穿戴设备

在可穿戴技术市场中,eMMC 5.1的应用同样展现出其多功能性。小型尺寸和低功耗特性的eMMC 5.1,使它非常适合像智能手表、健康追踪器这样的设备。这些设备需要在有限的空间内存储大量数据,同时对功耗有着严苛的要求。eMMC 5.1不仅优化了这些设备的存储性能,而且通过先进的电源管理功能,延长了电池寿命,这对于频繁使用又难以频繁充电的可穿戴设备来说至关重要。

## 3.2 e

0

0