版图验证DRC_LVS错误分析:Cadence后端实验的必备解决方案

发布时间: 2024-12-15 13:26:57 阅读量: 5 订阅数: 6

Cadence_后端实验系列19_版图验证__Assura

参考资源链接:[Cadence Assura版图验证全面教程:DRC、LVS与RCX详解](https://wenku.csdn.net/doc/zjj4jvqsmz?spm=1055.2635.3001.10343)

# 1. 版图验证的重要性与基本概念

在集成电路设计与制造的过程中,版图验证是一个关键环节,确保设计满足工艺技术要求并最大限度地减少生产中的缺陷。版图验证分为设计规则检查(Design Rule Check, DRC)和布局与原理图对比(Layout Versus Schematic, LVS)两部分。DRC专注于物理设计规则的合规性,而LVS则侧重于确认布局与电路原理图之间的逻辑一致性。版图验证的重要性体现在能够显著提高芯片的良率,减少重复设计和生产成本,缩短产品上市时间。理解这两者的区别和联系对于每一个从事IC设计的工程师来说都是必不可少的,这能够帮助他们更有效地进行工作并避免常见的设计错误。在接下来的章节中,我们将详细探讨DRC和LVS的具体应用、优化技巧以及解决问题的策略。

# 2. DRC验证的深入分析

## 2.1 DRC规则的设定和解释

### 2.1.1 DRC规则的分类和作用

设计规则检查(Design Rule Check, DRC)是集成电路(IC)设计流程中确保芯片在生产前满足制造工艺要求的重要步骤。DRC规则通常分为多个类别,每种类别包含了一系列的规则,涵盖了芯片设计的不同方面。

- **几何规则:** 这类规则关注的是物理布局的几何参数,比如线宽、间距以及孔的尺寸。这些参数是基于生产技术决定的,确保在特定的制造工艺下,元件和导线可以被可靠地生产和加工。

- **电气规则:** 电气规则检查设计中是否存在潜在的电气问题,如短路、开路、桥接和电流密度等。这些规则保证了电路能够在预定的电压和电流下正常工作,不会因电气问题而损坏或失效。

- **天线规则:** 由于在制造过程中,金属线条可能像天线一样收集电荷,导致静电放电(ESD)问题,天线规则旨在减少或防止这种现象。

- **最小化规则:** 这些规则确保布局在减少芯片面积的同时,还能够满足生产要求。它们帮助设计者平衡成本和性能。

DRC规则的作用是双重的,它们既确保了设计满足生产的物理要求,也保证了电路在电气性能上能够正常工作。通过DRC,可以提前发现设计中的潜在问题,避免昂贵的返工和生产延误。

### 2.1.2 DRC规则在实际设计中的应用

DRC规则的应用是集成电路设计流程中的一个核心环节。在设计过程中,工程师使用电子设计自动化(EDA)工具将设计意图转化为图形数据。在任何设计阶段,特别是详细设计阶段,都会进行DRC。

- **初始设计阶段:** 设计师首先使用EDA工具创建IC布局。此时,DRC规则被用来确保布局设计满足初步的设计要求。

- **设计迭代过程:** 设计不断修改和优化。每次修改后,都会重新运行DRC来验证更改是否引入了新的错误。

- **设计完成前:** 在设计接近完成阶段,会进行一系列的检查,确保没有任何DRC错误未被修复。这通常是一个严格和彻底的验证过程。

在实际应用中,DRC规则可以帮助工程师识别和解决许多设计中可能遇到的问题,比如过小的间距可能会导致制造过程中导线断裂,而过大的孔可能会在制造过程中造成不一致性。因此,DRC规则的应用对于保障设计质量和制造的成功至关重要。

## 2.2 DRC错误的识别和分类

### 2.2.1 常见的DRC错误类型

DRC错误是由违反DRC规则导致的,它们在IC设计中是不可避免的。下面是一些常见的DRC错误类型:

- **间距错误(Spacing Violations):** 指的是两个相邻的物体之间的距离小于工艺要求的最小距离。

- **宽度错误(Width Violations):** 当电路中的线条宽度低于制造工艺的最小宽度要求时发生。

- **重叠错误(Overlap Violations):** 当两个不同的层或元素,在同一区域重叠,没有保持适当的隔离空间时发生。

- **打孔错误(Via Violations):** 比如孔的尺寸不符合要求,或者孔与周围的导线和通孔之间的间距不符合规则。

- **密度错误(Density Violations):** 当设计中某区域的金属密度超出了工艺容许的最大或最小密度。

每个错误类型都有其特定的影响和潜在后果。例如,间距错误可能会引起制造过程中导线的短路;宽度错误可能导致电流传输效率降低或信号完整性问题;重叠错误可能会导致电气短路或不规则的电路行为。了解这些错误的成因和识别方法对于解决它们至关重要。

### 2.2.2 DRC错误的分析方法

分析DRC错误是解决它们的第一步。分析工作通常包含以下几个步骤:

1. **错误报告:** DRC工具会生成一个错误报告,其中列出了所有的DRC违规项。这个报告通常包含错误类型、位置、错误描述以及可能的解决建议。

2. **视觉检查:** 设计师将使用EDA工具查看图形界面中的错误位置,以直观地了解错误的上下文环境。

3. **逻辑分析:** 分析违规项在设计中的作用以及它们是如何影响电路的功能和制造的。

4. **根因查找:** 试图确定导致错误的根本原因,如设计疏忽、布局约束、工具限制或者不正确的设计规则。

5. **错误隔离和修复:** 将DRC错误限定在局部,避免修复措施影响到设计的其他部分。

通过这一系列的分析步骤,工程师可以系统地定位和解决DRC错误,确保设计的可靠性并提高生产成功率。

## 2.3 DRC验证工具的使用和技巧

### 2.3.1 Cadence工具的操作流程

Cadence是一套广泛用于IC设计的EDA工具。下面是一些使用Cadence进行DRC操作的常用步骤:

1. **加载设计:** 首先需要在Cadence Virtuoso布局编辑器中加载你的设计文件。

2. **设置规则集:** 指定一个设计规则文件(DRC deck),这个文件包含了制造工艺特定的规则。

3. **运行DRC:** 在布局编辑器中,找到并选择DRC工具。然后运行检查,并等待结果输出。

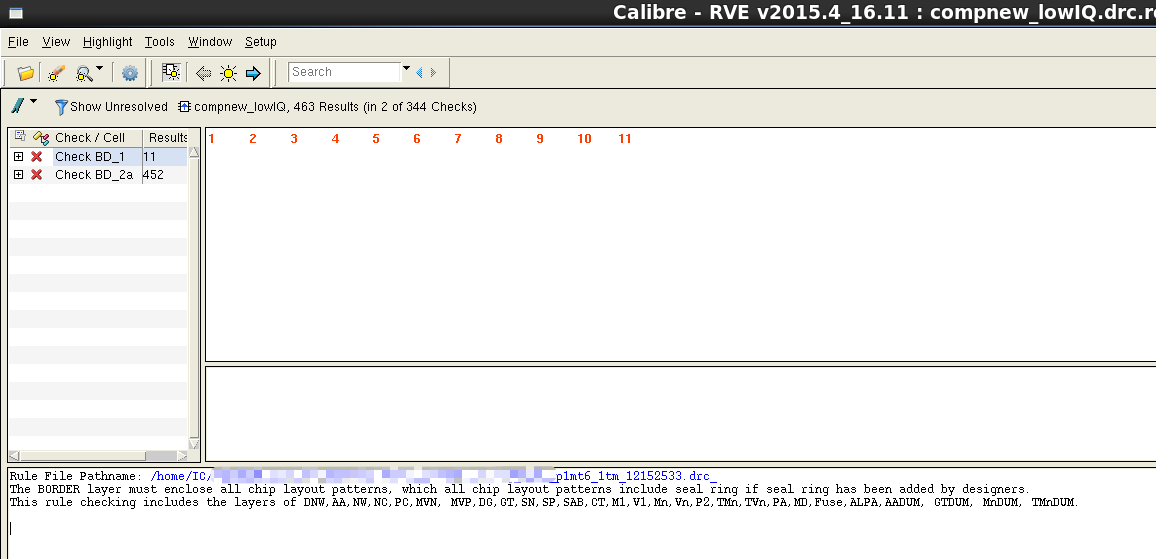

4. **查看和分析错误报告:** 一旦DRC完成,你会收到一个错误列表。使用Cadence提供的工具来查看错误的具体位置和类型。

5. **错误修复:** 根据错误报告,使用编辑工具对设计进行修改,消除DRC违规。

6. **复查和确认:** 修复错误后,需要重新运行DR

0

0