【硬件安全策略强化】:依据PCIe 5.40a数据手册打造无忧安全环境

发布时间: 2024-12-16 06:24:01 阅读量: 26 订阅数: 23

DWC PCIe databook(EP) Version 5.40a

参考资源链接:[2019 Synopsys PCIe Endpoint Databook v5.40a:设计指南与版权须知](https://wenku.csdn.net/doc/3rfmuard3w?spm=1055.2635.3001.10343)

# 1. PCIe标准与硬件安全概述

PCIe,即PCI Express,是一种广泛应用于计算机和通讯硬件设备中的高速串行计算机扩展总线标准。它用于连接主板与各种设备,提供高速数据传输路径,是当前硬件设备中不可或缺的组成部分。

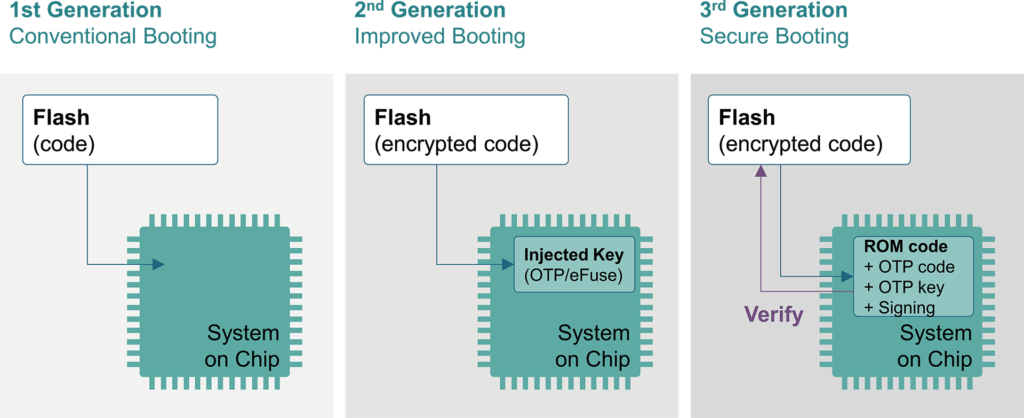

随着技术进步和网络安全威胁的演变,PCIe标准也开始集成一系列安全特性来保护系统免受攻击。例如,利用加密技术保护数据传输,实现身份验证机制来防止未授权设备接入等。硬件安全成为PCIe设计和开发中一个日益重要的课题。

了解PCIe硬件安全不仅是系统管理员的职责,同样对于IT安全分析师、硬件开发者以及维护网络基础设施的工程师来说都是至关重要的。本文将深入探讨PCIe硬件安全的各个方面,提供实用的知识和技巧,以帮助读者更好地理解和应用PCIe标准,确保硬件安全。

在接下来的章节中,我们将详细地了解PCIe的历史和架构,然后深入探讨PCIe 5.40a数据手册中的安全特性和机制,并且介绍PCIe硬件安全的实践操作。此外,我们还将探索强化硬件安全策略的方法,并通过案例分析展望未来硬件安全技术的发展趋势。

# 2. 理解PCIe 5.40a数据手册

## 2.1 PCIe的基本概念和架构

### 2.1.1 PCIe的演化历程

PCI Express(PCIe)作为一种高速串行计算机扩展总线标准,自2002年首次推出以来,已经经历了多次迭代和改进。PCIe 1.0提供了一个单向传输速率为2.5 GT/s的通道,带宽为250 MB/s。随后,PCIe 2.0将这一速率翻倍至5 GT/s,带宽也增加到500 MB/s。PCIe 3.0再次将速率提高到8 GT/s,并将通道的单向带宽提升至1 GB/s。

在2017年推出的PCIe 4.0中,带宽再次翻倍,达到了2 GB/s。最新版的PCIe 5.0标准,已经将带宽提升至4 GB/s。每个新版本的PCIe都是向后兼容的,意味着新的硬件可以在旧的PCIe插槽上运行,但速度会受限于旧的协议版本。

PCIe的演进不仅仅是速率的提高,还包括了对数据传输效率的改进、电源管理的优化以及更强大的错误检测和纠正机制。这些改进使得PCIe成为连接CPU、内存、存储和外围设备的重要技术,广泛应用于个人电脑、服务器、网络设备、图形卡等。

### 2.1.2 PCIe架构的核心组件

PCIe架构的主要组件包括根复合体(Root Complex)、交换器(Switch)、端点设备(Endpoint)和PCIe桥接器(Bridge)。根复合体是PCIe总线的起点,通常集成在CPU或南桥芯片中,负责发起事务和管理PCIe拓扑。交换器用于扩展总线,提供更多的PCIe插槽,以连接更多的端点设备。端点设备是PCIe总线上的终端,如网卡、硬盘控制器或USB控制器等。PCIe桥接器用于连接不同类型的总线,比如连接到传统的PCI总线。

PCIe架构采用了一种分层的模型,其中事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer)是三个主要层次。事务层负责构建和解析事务层包(TLP),处理内存、I/O和配置事务。数据链路层负责确保TLP在相邻对等层间可靠地传输。物理层负责在物理介质上编码和解码数据流,管理信号和时钟,并提供链路训练和初始化服务。

## 2.2 PCIe 5.40a数据手册深入解析

### 2.2.1 数据手册的结构和内容概览

PCIe 5.40a数据手册是一份详尽的技术文献,它为设计者和开发者提供了深入理解PCIe 5.0协议规范所需的所有信息。该数据手册分为多个部分,每个部分都详细介绍了PCIe架构中的特定方面。数据手册的结构通常按照功能和层次划分,涵盖了从物理层到事务层的每个层级的技术细节。

数据手册通常从对PCIe标准的概述和术语定义开始,接着介绍PCIe架构的细节,包括如何连接设备、处理事务和确保数据传输的可靠性。还包括关于电源管理、错误处理、热插拔等高级特性的详细讨论。在安全特性方面,手册会介绍诸如防篡改、加密传输等保护机制。

每一节或子章节都会以一系列规范和要求的形式出现,定义了硬件制造商和软件开发者在设计和实现PCIe设备时必须遵循的标准。为了方便开发者,数据手册还提供了大量的示例和图表,以帮助理解复杂的概念和技术细节。

### 2.2.2 关键安全特性的介绍

PCIe 5.40a标准在安全性方面包含了多项创新特性。其中,物理层的物理安全特性包括了针对电缆、连接器和插槽的保护措施,以防止物理篡改。在数据链路层,数据链路层保护(DLLP)为数据传输提供了完整性校验和防止数据篡改的机制。事务层则包含了一系列的安全事务类型,如请求和响应事务,它们用于实现更高级别的安全措施。

安全性方面,数据手册详细介绍了如何在数据传输过程中使用端到端的加密机制来保护数据。例如,通过加密数据包的内容,即使数据被截获,也无法被解读。此外,还包括了验证和授权机制,确保只有授权的设备和软件可以访问总线上的资源。

数据手册还讨论了与虚拟化相关的安全特性,例如虚拟通道的隔离和资源访问控制,这有助于提供更细粒度的安全性控制。这些特性对于在数据中心和云计算环境中运行的PCIe设备至关重要,可以确保不同的虚拟机不会互相干扰,提升了系统的整体安全性。

## 2.3 PCIe安全机制的工作原理

### 2.3.1 硬件层面的安全措施

在硬件层面上,PCIe设备实施了多层次的安全措施来保护数据和系统资源。首先,物理层的安全措施包括了对PCIe插槽和电缆的保护,它们通过机械锁定机制来防止非法插拔,确保设备的物理安全性。此外,物理层还可以检测非法篡改行为,并发出安全警告。

数据链路层通过一个称为链路完整性协议(Link Integrity Protocol)的机制来确保链路在通信期间的稳定性。链路完整性协议能够检测和响应链路故障,帮助防止数据在不稳

0

0