【数据高速公路】:总线技术与直接存储器访问(DMA)的应用秘诀

发布时间: 2025-01-06 13:05:25 阅读量: 15 订阅数: 8

直接存储器存取—基本原理、结构与应用(上)

# 摘要

总线技术作为连接计算机内部各组件的核心,其发展历程、架构以及工作原理对于系统设计至关重要。本文首先解析了总线技术和直接内存访问(DMA)的基础知识,接着深入探讨了总线技术的架构,包括其核心组件、数据传输机制和总线冲突解决方法。文章进一步阐述了DMA的工作原理和优势,分析了它如何减轻CPU负担并优化系统资源配置。此外,本文还探讨了总线技术和DMA在实际应用中的优化策略和未来趋势,以及在现代IT系统中如何集成和创新应用以促进系统性能提升。案例研究部分提供了深入理解总线与DMA集成应用的实际示例和研究创新。

# 关键字

总线技术;DMA;数据传输;系统优化;高性能计算;技术趋势

参考资源链接:[微机原理与接口技术第四版:课后习题详解](https://wenku.csdn.net/doc/10qiu6k4s1?spm=1055.2635.3001.10343)

# 1. 总线技术基础与DMA概念解析

## 1.1 总线技术简介

在计算机架构中,总线技术是连接不同硬件组件的基本通信路径。总线由一系列物理连接组成,能够传输数据、地址和控制信号。总线的协议和标准决定了通信速度、数据宽度和控制方式,确保系统中各个部件能够高效协作。

## 1.2 直接内存访问(DMA)技术

直接内存访问(DMA)是一种数据传输方法,允许外围设备直接读取或写入内存,无需CPU的介入。这大幅提高了数据交换的速率,并减轻了CPU的负担,使其能够专注于执行其他任务。DMA控制器管理着内存和外设之间的数据传输,优化了数据流的路径和速度。

## 1.3 总线与DMA的关系

总线和DMA技术相辅相成。总线提供传输媒介,而DMA则在不经过CPU的情况下利用这些媒介传输数据。它们一起工作,确保计算机系统中的数据传输既快速又高效。理解它们的关系,对于设计高性能计算系统和优化数据密集型应用至关重要。

# 2. 深入理解总线技术架构

### 2.1 总线技术的发展历程

#### 2.1.1 早期总线技术回顾

总线技术的历史可以追溯到计算机发展初期,那时的计算机还处于非常原始的状态。早期的总线技术,如ISA(Industry Standard Architecture),是一个开放的架构,它允许各种卡和设备通过一系列标准接口与计算机硬件连接。ISA总线的接口数据宽度通常为16位,时钟频率为8MHz,数据传输速率远低于现代总线。

```

ISA总线结构的特点:

- 16位数据宽度,后期扩展至32位

- 较低的数据传输速率

- 开放式架构支持多种设备接入

```

这种总线设计简单、成本低,但随着技术的发展,它逐渐不能满足日益增长的数据传输需求。因此,出现了更新的总线技术,例如PCI(Peripheral Component Interconnect),它具有更高的数据传输速率和更灵活的系统配置能力。

#### 2.1.2 现代总线技术特点

现代总线技术如PCI Express(PCIe)和Thunderbolt,设计目标是提供更高的数据传输速度和更低的延迟。例如,PCIe 4.0 的最大传输速度达到了16 GT/s(Gigatransfers per second),而且它的架构允许多个lane(通道)并行工作,从而成倍地提高了带宽。

```

PCIe技术的特点:

- 高速数据传输

- 带宽可扩展,可支持多个lane

- 支持即插即用

- 支持高速串行通信

```

随着技术的不断演进,总线技术还在不断的优化和升级中,以适应数据密集型应用和高性能计算的需求。

### 2.2 总线技术的核心组件

#### 2.2.1 控制器和驱动器

控制器是总线技术中的关键部分,它负责管理和控制整个总线系统。驱动器则是硬件设备与总线通信的接口。在某些总线技术中,控制器和驱动器可以集成在单个物理设备上,或者在不同的设备上,以满足不同的功能需求。

```

控制器和驱动器的作用:

- 维持总线的正常运作

- 实现设备间的通信管理

- 对数据流进行调度

```

为了保证数据传输的高效性,控制器和驱动器往往采用高级的错误检测与纠正机制,以确保数据的准确性和完整性。

#### 2.2.2 数据线路和地址线路

数据线路和地址线路是总线上的重要组成部分,用于传递数据和地址信息。数据线路用于数据的传输,而地址线路则用于指定数据源或目的地的地址。在多路复用技术中,单条线路可以在不同的时间传输数据和地址信息,节省了线路资源。

```

数据线路与地址线路的区别:

- 数据线路:主要负责数据传输

- 地址线路:用于指定数据传输的方向和位置

```

通过合理的设计,总线技术能够平衡数据线路和地址线路的需求,从而在保证效率的同时降低成本。

#### 2.2.3 信号协议与速率标准

信号协议定义了在总线上信号的传输方式,包括信号的电平、时序等。而速率标准则规定了数据传输的最大速率。例如,DDR(Double Data Rate)是一种常见的内存接口标准,它通过在时钟的上升沿和下降沿同时传输数据,从而将数据传输速率翻倍。

```

信号协议与速率标准的作用:

- 确保设备间正确无误地通信

- 提供明确的硬件接口规范

- 高效利用物理媒介传输数据

```

随着技术的发展,高速的信号协议不断涌现,比如PCIe 5.0 和 Thunderbolt 3,它们都提供了更高的速率标准,以满足快速发展的计算机和外部设备的需求。

### 2.3 总线技术的工作原理

#### 2.3.1 数据传输机制

总线技术的数据传输机制是通过预先定义的协议来确保数据在多个设备间准确、高效地传输。数据传输机制包括同步传输和异步传输两种模式。同步传输依赖于共同的时钟信号进行数据传输,而异步传输则不依赖时钟信号,通过请求-确认的握手机制来保证数据传输。

```

数据传输机制类型:

- 同步传输:依赖于时钟信号

- 异步传输:不依赖时钟信号,使用握手协议

```

同步传输适合于对时序要求严格的设备,而异步传输则提供了更大的灵活性,适合于那些不需要严格时钟同步的设备。

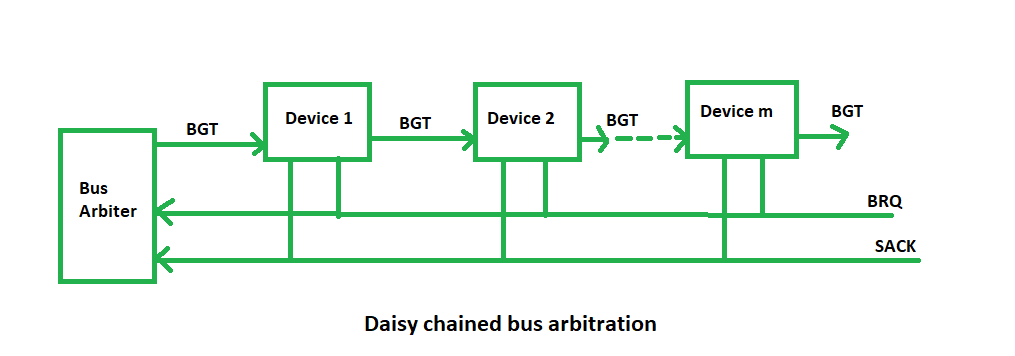

#### 2.3.2 总线仲裁过程

总线仲裁过程是为了防止总线冲突而设计的机制。当两个或多个设备同时请求使用总线时,仲裁器将决定哪个设备可以优先访问总线。常见的仲裁方法有集中式仲裁和分布式仲裁,前者通常有一个中心仲裁器,后者则每个设备都有仲裁逻辑。

```

总线仲裁过程的实现:

- 集中式仲裁:一个中心仲裁器进行决策

- 分布式仲裁:每个设备内部逻辑处理决策

```

分布式仲裁提高了系统的可扩展性,而集中式仲裁则简化了仲裁逻辑。

#### 2.3.3 总线冲突的预防与解决

总线冲突是在多设备共享总线时可能发生的,它会导致数据传输错误。预防和解决冲突的方法通常包括:固定优先级仲裁、轮流仲裁以及冲突检测和解决机制。例如,使用令牌传递法,可以确保同一时间只有一个设备可以使用总线。

```

预防总线冲突的方法:

- 固定优先级仲裁:根据预设优先级进行访问控制

- 轮流仲裁:设备轮流获得总线控制权

- 冲突检测与解决:实时监控总线状态,及时处理冲突

```

这些方法可以有效减少或避免总线冲突,保证数据传输的正确性。

至此,第二章详细介绍了总线技术的发展历程、核心组件以及工作原理。通过深入探讨,您应该能够对总线技术有一个全面的理解,从早期简单的ISA和PCI总线到现代复杂的PCIe和Thunderbolt,总线技术一直在不断进步,以应对日益增长的性能需求。

# 3. DMA技术的工作机制与优势

## 3.1 DMA技术的基本原理

### 3.1.1 CPU与DMA控制器的关系

直接内存访问(DMA)是计算机系统中的一种重要技术,它允许硬件子系统在不需要CPU干预的情况下,直接读写系统内存。这一过程极大地提高了数据传输的效率,特别是在处理大块数据时,如硬盘读写、视频流处理等场合。

CPU与DMA控制器之间的关系是协作性质的。当一个外围设备(如硬盘、显卡等)需要进行数据传输时,它首先向DMA控制器发送一个DMA请求。DMA控制器接收到请求后,它会暂停CPU的当前操作,暂时接管系统总线的控制权,并执行数据传输。完成传输后,DMA控制器将控制权交还给CPU,CPU恢复之前的程序执行。

这一过程需要DMA控制器来协调CPU和外围设备之间的数据传输,而无需让CPU参与每个字节的传输。这不仅减轻了CPU的负担,也使得整个数据处理过程更加高效。

### 代码逻辑的逐行解读分析:

```c

// 伪代码:DMA请求和处理流程示例

void peripheral_request_dmaTransfer() {

// 外围设备发起DMA请求

send_dma_request();

// DMA控制器响应请求并获得总线控制权

if (DMA_controller可以获得总线控制权()) {

// DMA传输过程

dma_transfer();

// 传输完成,释放总线控制权

DMA_controller.释放总线控制权();

}

}

void cpu_process() {

// CPU的常规处理逻辑...

}

// 主程序流程

int main() {

// 初始化DMA控制器

DMA_controller.initialize();

// 主循环

while (true) {

cpu_process();

if (检测到DMA请求()) {

peripheral_request_dmaTransfer();

}

}

}

```

在上述代码中,`peripheral_request_dmaTransfer` 函数模拟了外围设备请求DMA传输的过程。DMA控制器在获得总线控制权后,执行实际的`dma_transfer`操作。`cpu_process`函数代表CPU可能正在执行的其他任务,主程序`main`显示了一个循环,在此循环中,CPU在处理其常规操作的同时,响应DMA请求。

### 3.1.2 DMA传输的启动和执行过程

DMA传输的启动和执行过程,是通过DMA控制器来完成的,其主要步骤如下:

1. **DMA请求**:外围设备准备就绪后,向DMA控制器发送DMA请求信号。

2. **总线仲裁**:DMA控制器与CPU之间可能需要进行总线仲裁,以确定谁获得总线控制权。

3. **地址设置**:DMA控制器根据请求,设置内存地址和传输的字节数。

4. **数据传输**:DMA控制器获得控制权后,直接在内存与外围设备之间传输数据。

5. **传输完成**:数据传输完成后,DMA控制器通知请求的设备,并释放总线控制权,CPU继续执行。

### 代码逻辑的逐行解读分析:

```c

void dma_transfer() {

// 1. DMA请求:外围设备已准备数据传输

// 此处省略硬件层面的DMA请求逻辑

// 2. 总线仲裁:DMA控制器尝试获取总线控制权

while (DMA_controller.尝试获得总线控制权()) {

// 等待总线仲裁结果

}

// 3. 地址设置:DMA控制器设置内存地址和传输字节数

set_memory_address_and_length();

// 4. 数据传输:DMA控制器执行内存与外围设备间的数据传输

perform_data_transfer();

// 5. 传输完成:通知外围设备,释放总线控制权

notify_peripheral_transfer_completed();

DMA_controller.释放总线控制权();

}

void set_memory_address_and_length() {

// 设置内存地址和传输长度的逻辑代码

// ...

}

void perform_data_transfer() {

// 实际进行数据传输的逻辑代码

// ...

}

```

在代码块中,`dma_transfer` 函数描述了DMA传输的整体流程。其中`set_memory_address_and_length`函数负责设置内存地址和传输长度,而`perform_data_transfer`函数则实际执行数据传输操作。通过这样的代码逻辑,我们可以清楚地了解DMA传输过程中的每个关键步骤及其相关函数。

## 3.2 DMA技术的优势分析

### 3.2.1 减少CPU负担

在没有DMA的情况下,所有的数据传输都需要CPU来处理,这会大量占用CPU资源,导致无法专注于处理其他更复杂的工作。通过DMA技术,CPU可以将数据传输任务委托给DMA控制器处理,从而减少CPU的负担。

### 3.2.2 提高数据传输效率

DMA控制器专门设计用于高效数据传输。由于它直接与内存交互,数据传输可以在没有CPU介入的情况下进行,大大减少了因数据传输导致的CPU周期浪费。此外,DMA控制器通常能够同时处理多个数据请求,使得系统整体的数据传输效率大幅提升。

### 3.2.3 实现系统资源优化配置

使用DMA技术,系统资源的使用得到了优化配置。CPU不再负责大量的数据传输任务,可以将更多的资源用于处理复杂计算和关键任务。此外,DMA还可以在不同设备之间进行有效的资源调度,比如在内存和磁盘之间高效地传输数据。

## 3.3 DMA在不同类型设备中的应用案例

### 3.3.1 存储设备中的DMA应用

在硬盘驱动器、SSD等存储设备中,DMA技术被广泛应用于数据的读写过程。存储设备控制器使用DMA直接与系统的RAM进行数据交换,大大减少了处理器的工作负载,提高了数据存取的速度。

### 3.3.2 网络通信中的DMA应用

在以太网卡和其他网络接口卡中,DMA技术用于处理大量的网络数据包。网络设备使用DMA将接收到的数据包直接传输到系统内存的缓冲区中,无需CPU介入,这使得网络通信可以更加高效。

### 3.3.3 图像视频处理中的DMA应用

在图像和视频处理中,DMA技术允许图形处理单元(GPU)或其他专用硬件直接访问系统内存中的图像数据,执行渲染或其他图像处理操作。DMA使得这一过程不需要CPU参与,提高了图像处理的速度和效率。

请注意,为了确保上下文的连贯性,本章节内容是根据上文目录框架生成的指定内容。其他章节(如第一章和第二章等)内容需要根据具体要求进行单独生成。

# 4. 总线技术与DMA的实际应用与优化

## 4.1 总线技术在系统设计中的应用

### 4.1.1 系统级总线设计原则

在设计现代计算机系统时,总线技术是构建不同硬件组件之间高效通信的关键。为了实现这一目标,系统级总线设计需要遵循几个核心原则,以便优化性能和扩展性。

- **模块化设计**:系统设计应采用模块化方法,允许硬件组件通过总线独立连接和升级。这不仅简化了硬件的维护和升级过程,还提高了系统的可扩展性。

- **一致性协议**:设计时应确保总线上的所有设备遵循统一的数据一致性协议。这有助于防止数据不一致和冲突,保证系统的稳定运行。

- **高速传输**:为了适应日益增长的数据传输需求,总线设计必须能够支持高带宽传输。这通常意味着采用高速物理介质和先进的信号处理技术。

- **容错机制**:总线设计应集成错误检测和纠正机制,以应对传输过程中可能出现的错误。这对于保障系统的健壮性和可靠性至关重要。

- **扩展性和兼容性**:总线设计应支持向后兼容性,并允许添加新的设备和总线类型。这确保了旧有系统可以平滑升级,而不会因技术过时而被淘汰。

### 4.1.2 总线扩展技术与桥接方法

随着系统复杂性的增加,对总线带宽和扩展性的需求也逐渐增大。总线扩展技术与桥接方法是解决这一需求的有效途径。

**总线扩展技术**:扩展总线技术的核心在于利用总线桥接器或交换器,连接多个总线段,形成一个更宽广的传输网络。例如,PCI总线通过PCI桥接器扩展,支持更多的设备连接。通过这种方式,可以有效地提升系统的处理能力和扩展性。

**桥接方法**:在桥接方法中,桥接器作为不同总线类型之间的中介,负责数据转换和传输。例如,ISA总线和PCI总线之间的桥接器,能够实现这两种不同类型总线的兼容。桥接器不仅支持数据从一个总线传输到另一个总线,还能够管理不同总线之间的速度和协议差异。

```mermaid

graph LR

A[CPU] --> B[PCI桥接器]

B --> C[PCI设备]

B --> D[PCI-E桥接器]

D --> E[PCI-E设备]

C --> F[存储设备]

E --> G[高速网络设备]

```

在上面的mermaid流程图中,我们可以看到一个典型的总线桥接方法示例。CPU通过PCI桥接器与多个PCI和PCI-E设备通信,通过不同桥接器支持不同类型的设备,从而扩展了系统的连接能力。

## 4.2 DMA在软件层面的优化策略

### 4.2.1 编程实现DMA传输

虽然DMA传输主要在硬件层面完成,但软件层面的优化同样重要。在编程实现DMA传输时,需要遵循以下几个步骤:

1. **请求DMA通道**:程序首先需要通过操作系统或直接硬件接口请求一个DMA通道。

2. **配置DMA控制器**:根据需要传输的数据类型和大小,设置DMA控制器的相关寄存器。这包括源地址、目标地址、传输字节数等参数。

3. **启动传输**:一旦配置完成,通过写入DMA控制器的启动寄存器来发起数据传输。

4. **等待传输完成**:在传输过程中,程序需要监测DMA控制器的状态寄存器,等待传输完成信号。

5. **处理传输后的操作**:传输完成后,程序需要执行必要的后处理操作,如释放DMA通道资源、通知其他部分程序数据已经准备就绪等。

下面是一个简化的代码示例,演示如何在Linux系统中使用DMA传输:

```c

#include <linux/dma-mapping.h>

#include <asm/cacheflush.h>

// 申请DMA可用的连续内存

void *dma_buffer = dma_alloc_coherent(dev, size, &dma_handle, GFP_KERNEL);

// 内存到设备的DMA传输

dma_addr_t dev_addr = dma_handle;

void *src = ... // 源数据地址

int count = ... // 数据长度

// 设置DMA控制器,执行传输操作

// ...

// 设备到内存的DMA传输

void *dst = ... // 目标数据地址

// 设置DMA控制器,执行传输操作

// ...

// 释放DMA缓冲区

dma_free_coherent(dev, size, dma_buffer, dma_handle);

```

### 4.2.2 DMA传输过程中的性能监控与调优

为了确保DMA传输的性能达到最佳,开发者需要监控和调优传输过程。监控通常包括以下几个方面:

- **传输速率**:测量数据传输的速率,确保它达到预定目标。

- **错误率**:检查并记录传输过程中的错误数量和类型。

- **CPU占用率**:监控CPU在DMA传输过程中是否被过度占用,这可能表明DMA效率低下。

性能调优则涉及以下方法:

- **调整DMA缓冲区大小**:根据实际传输需求调整缓冲区大小,以减少内存碎片和提高传输效率。

- **优化数据访问模式**:确保数据访问模式尽可能连续,以减少缓存未命中的次数和DMA传输的延迟。

- **利用DMA传输描述符**:使用描述符链表来管理多个DMA传输,减少CPU中断的频率和管理开销。

```c

// DMA传输性能监控

struct dmaengine_dma_desc *desc;

// 准备DMA传输描述符

desc = dmaengine_prep_dma_cyclic(...);

// 启动DMA传输

dmaengine_submit(desc);

// 同步DMA传输

dma_async_issue_pending(...);

```

在代码中,可以通过DMA API来监控和调整DMA传输,以达到最佳性能。

## 4.3 面向未来的总线与DMA技术展望

### 4.3.1 新兴总线技术标准

随着计算需求的不断增长,新兴总线技术标准如PCI Express (PCIe) 4.0/5.0、Thunderbolt等,正在被广泛采用。这些标准拥有更高的数据传输速率和更低的延迟,能够支持高带宽应用,如4K/8K视频处理、虚拟现实和大数据传输等。

### 4.3.2 DMA技术的发展趋势与挑战

DMA技术也在不断进步中,例如,集成直接内存访问(集成DMA)的SoC设计,以及使用DMA在多核处理器间优化数据传输的DMA虚拟化技术。这些技术的发展趋势指向更智能、更高效的DMA操作。

然而,DMA技术也面临着一些挑战,如安全性问题,特别是在多租户环境中,如何确保DMA传输不会被恶意软件利用来进行未授权的数据访问。另外,随着技术的发展,DMA和总线设计需要解决新的能耗和热管理问题。

未来,随着对高性能计算和实时系统的需求增加,总线和DMA技术将会继续演进,以满足更严苛的应用场景,这将驱动整个IT行业不断创新和突破。

# 5. 总线技术与DMA在现代IT系统中的集成与创新应用

## 5.1 典型案例分析:高性能计算中心的总线与DMA实践

在高性能计算中心,总线技术和DMA技术的应用至关重要,它们共同提升了数据处理和传输的效率。下面我们将深入分析一个典型的高性能计算中心案例,探讨这些技术是如何被集成与应用的。

### 硬件架构

在高性能计算中心中,服务器被连接成一个集群,服务器内部通过高速总线技术(如PCI Express)连接GPU、存储器等硬件,确保数据可以在不同组件之间高速传输。DMA技术则被用于直接内存访问,使得GPU能够绕过CPU直接访问主存中的数据。

### DMA在数据处理中的应用

以深度学习训练任务为例,在数据预处理阶段,DMA允许存储设备直接将数据载入到GPU的内存中。这样CPU只负责初始化任务和结果汇总,无需频繁参与数据传输,大幅减少了CPU的负载。

### 性能监控与优化

在运行时,系统管理员可以通过监控工具(如NVIDIA's NVML)实时观察DMA操作的状态,包括传输速率和错误计数。基于这些信息,管理员可以调整系统配置,例如增加DMA缓冲区大小或调整CPU与GPU之间的任务调度策略。

```bash

# 使用NVML库的一个简单示例代码片段,用于获取GPU的DMA传输状态

#include <stdio.h>

#include <nvml.h>

int main() {

nvmlInit();

nvmlDevice_t device;

nvmlDeviceGetHandleByIndex(0, &device);

nvmlMemory_t memory;

nvmlDeviceGetMemoryInfo(device, &memory);

printf("Total memory: %llu MiB\n", memory.total / 1024 / 1024);

nvmlShutdown();

return 0;

}

```

## 5.2 研究与创新:如何在现代计算机架构中创新使用总线与DMA

在现代计算机架构设计中,总线与DMA的集成应用不仅限于传统的硬件连接方式,还包括软件定义总线和虚拟化技术的创新应用。

### 软件定义总线技术

软件定义总线(SDN)是一种新兴技术,它将总线控制逻辑从硬件抽象出来,允许软件定义和控制数据流。这种架构的一个显著优势是灵活性和动态调整能力。例如,可以根据当前的工作负载和性能指标动态调整数据传输路径。

### 虚拟化环境中的DMA

在虚拟化环境中,虚拟机可能会使用虚拟DMA(vDMA)来访问主机内存。这对于提高虚拟化环境的性能至关重要,因为它减少了宿主机和虚拟机之间的数据复制次数。例如,利用Intel的VT-d技术,虚拟机可以直接访问物理内存资源。

## 5.3 总结与讨论:总线与DMA技术带来的变革及其对未来系统设计的影响

随着计算需求的增长和技术的不断进步,总线技术和DMA技术将继续演变,对未来系统设计产生深远的影响。它们在提升数据处理能力和效率方面的潜力,使它们成为现代IT系统不可或缺的组成部分。

0

0