从理论到实践:74LS90在时钟信号生成中的应用详解

发布时间: 2025-01-04 08:25:18 阅读量: 7 订阅数: 14

基于OpenCV的人脸识别小程序.zip

# 摘要

数字逻辑和时钟信号的生成是现代电子系统设计的核心部分。本文详细介绍了74LS90计数器芯片的功能、特性和应用场景。通过探讨时钟信号的基础知识及其稳定性要求,分析了74LS90在时钟信号生成中的工作原理和理论计算方法。本文还展示了74LS90在实际电路设计中的应用,包括时钟分频器的设计以及与其他数字IC的整合。案例分析章节重点讨论了时钟信号生成在微控制器和数字通信系统中的应用。最后,文章探讨了时钟信号生成的高级技巧,如稳定性增强和抗干扰设计,以及74LS90的现代替代品和未来发展。

# 关键字

数字逻辑;时钟信号;74LS90计数器;时钟信号生成;分频器设计;微控制器接口

参考资源链接:[74LS90的功能表.doc](https://wenku.csdn.net/doc/6465c4e65928463033d05a78?spm=1055.2635.3001.10343)

# 1. 数字逻辑和时钟信号的基础知识

在数字电子学中,时钟信号扮演着至关重要的角色,它是确保数字系统同步运行的脉动心跳。时钟信号是一种周期性的方波,用于控制数字电路中操作的顺序性和时间间隔。本章我们将深入探讨数字逻辑的基本概念和时钟信号的基础知识,为后续章节中对74LS90计数器芯片的详细介绍和应用分析打下坚实的基础。

## 1.1 数字逻辑简介

数字逻辑主要关注的是使用“0”和“1”的二进制系统进行信息表示和处理。数字逻辑设计中的逻辑门是构建复杂数字系统的基本构件,包括与门、或门、非门等,它们能执行基本的逻辑运算。这些基本逻辑门电路可通过组合,构成诸如译码器、多路选择器、触发器和计数器等复杂电路。

## 1.2 时钟信号的角色

时钟信号在数字电路中起到了至关重要的时序控制作用。它保证了数据在正确的时间被读取或写入,确保了整个系统的稳定性和可靠性。从微处理器到通讯设备,时钟信号都是不可或缺的,它规定了数据传输和处理的速率以及同步性。

理解了数字逻辑的基础和时钟信号的重要性后,我们将继续探索74LS90计数器芯片,它在数字电路设计中具有广泛应用。通过本章的学习,你将为掌握后续章节中74LS90的应用和设计打下坚实的基础。

# 2. 74LS90计数器芯片概述

### 2.1 74LS90芯片的功能和特性

#### 2.1.1 内部结构和逻辑功能

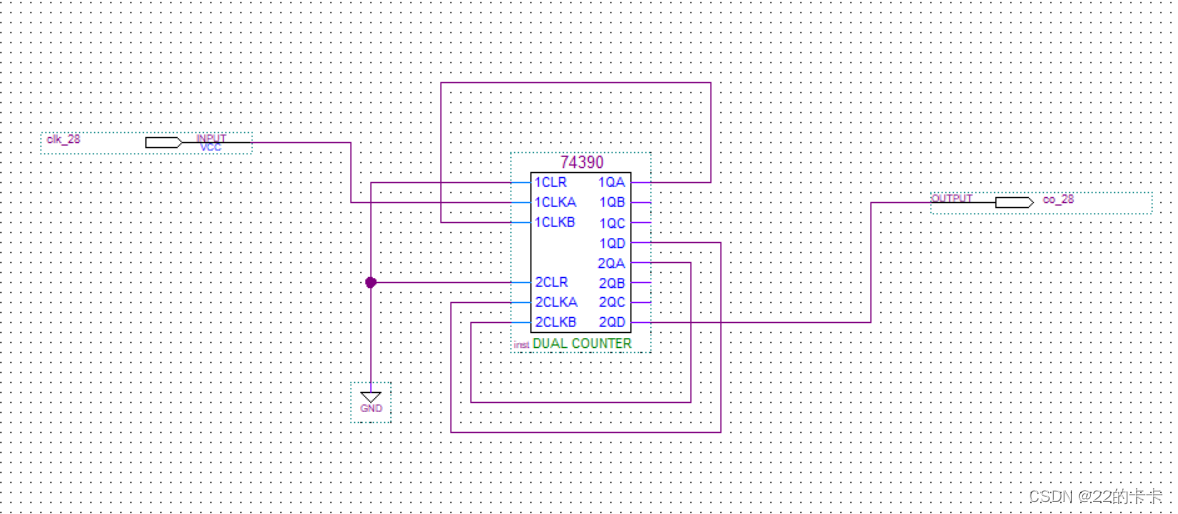

74LS90是一款广泛应用于数字逻辑设计中的双十进制计数器芯片。该芯片内部包含两个独立的可重置的计数器。每个计数器都是一个可逆计数器,它可以通过外部控制信号来实现增加或减少的操作。具体而言,每一个计数器都有四个输入端和四个输出端,分别负责计数信号的输入、控制信号的输入以及计数结果的输出。

在内部结构上,74LS90使用了四个触发器,采用J-K触发器的逻辑来实现其计数功能。该芯片是十进制计数器,但它也支持二进制计数模式,使得其应用场景非常广泛。

#### 2.1.2 工作模式和时序参数

74LS90工作模式包括了同步清零、同步预置、异步清零以及正常的计数模式。芯片可以通过特定的引脚状态选择不同的工作模式,如R0(1)和R0(2)引脚同时接地为同步清零模式,而R1(1)引脚接地则为异步清零模式。

时序参数是设计和使用74LS90时必须考虑的因素之一。这些参数包括计数器的设置时间、保持时间和脉冲宽度。例如,数据设置时间Ts和数据保持时间Th,分别定义了数据在计数器进行计数前必须稳定的时间以及在计数后保持稳定的时间。这些参数共同决定了74LS90在各种复杂电路中的可靠性和稳定性。

### 2.2 74LS90与其他数字IC的关系

#### 2.2.1 与555定时器的配合使用

为了生成精确的时钟信号或脉冲波形,555定时器常与74LS90计数器芯片配合使用。555定时器可以产生稳定的脉冲信号,而74LS90计数器则可以通过该脉冲信号进行计数,实现分频和计数功能。

在实际应用中,首先需要设置555定时器的工作模式,例如可以将555设置为单稳态模式,产生特定宽度的脉冲信号。然后,将此脉冲信号输入到74LS90的计数输入端。通过适当配置74LS90的控制端,可以实现对输入脉冲信号的计数,并通过输出端得到分频后的时钟信号。两者结合,不仅可以实现基础的计数和分频任务,还可以构造出更为复杂的时序控制电路。

#### 2.2.2 与74系列逻辑门的连接方式

74LS90在与74系列逻辑门连接时,需要考虑逻辑电平的匹配和信号的传递。由于74系列逻辑门通常工作在5V的TTL电平,而74LS90也符合TTL电平标准,因此两者可以直接连接。

连接的方式包括但不限于将74LS90的输出端连接到74系列逻辑门的输入端。例如,74LS90的进位输出端可以连接到74系列逻辑门的一个输入端,而逻辑门的输出端又可以作为74LS90的计数控制信号输入。通过这种方式可以实现较为复杂的逻辑操作和更高级的计数器功能。

### 2.3 74LS90的应用领域和场景

#### 2.3.1 时钟信号生成

74LS90常被用来作为时钟信号的生成器件。时钟信号是数字电路中的心脏,负责同步和协调各种数字组件的操作。由于74LS90可以精确地进行计数和分频,因此非常适合用于产生稳定和精确的时钟信号。

在生成时钟信号的过程中,我们需要为74LS90提供一个合适的时钟源信号,然后通过适当的连接和配置,使其按照所需的频率和相位进行计数。74LS90的输出端连接到其它数字电路的时钟输入端,从而使得整个系统能够按照预期的时序运行。

#### 2.3.2 分频器和计数器设计

在数字系统设计中,分频器和计数器是不可或缺的组件。74LS90可以用作分频器和计数器,它能够将输入信号分频,或是对事件进行计数。

分频器的应用包括减少数字电路的主时钟频率,以适应某些电路模块的操作频率要求。例如,如果某个电路模块只需要1MHz的时钟信号,而主时钟提供的是8MHz的时钟信号,这时可以使用74LS90作为分频器,将8MHz的时钟信号分频为1MHz。

作为计数器时,74LS90可以用来对事件的发生次数进行计数。比如,在数字仪表中,74LS90能够统计输入脉冲的数量,进而显示相应的数值。在这些应用中,74LS90的可配置特性和灵活性使其成为了设计者常用的选择之一。

# 3. 时钟信号生成的理论分析

在数字系统中,时钟信号的稳定性和准确性直接影响整个系统的性能。本章将深入探讨时钟信号的基本概念、74LS90芯片在时钟信号生成中的原理以及如何进行时钟信号的理论计算和设计。

## 3.1 时钟信号的基本概念

### 3.1.1 时钟频率和周期的理解

时钟频率是指单位时间内时钟信号周期性变化的次数,通常以赫兹(Hz)为单位。时钟周期是时钟频率的倒数,表示时钟信号完成一个周期性变化所需的时

0

0