【电路故障诊断大师】:D触发器故障的深层原因与应对策略

发布时间: 2025-01-10 08:58:20 阅读量: 1 订阅数: 6

# 摘要

D触发器作为数字电路中的基本存储元件,其稳定性和可靠性对整个系统的性能至关重要。本文首先介绍了D触发器的工作原理及其在电路设计中的重要性。随后,探讨了D触发器可能发生的故障类型及诊断方法,包括电压测试、时序分析和逻辑分析,并评估了高级诊断工具和新技术的应用。通过案例分析,详细讨论了不同环境下D触发器故障的实际例子,并提出了具体的预防和应对策略。最后,展望了D触发器技术的未来发展方向,特别是在故障诊断和集成电路设计领域的最新趋势。

# 关键字

D触发器;故障诊断;设计原理;电路测试;预防策略;故障模拟

参考资源链接:[边沿D触发器详解:电路结构与工作原理](https://wenku.csdn.net/doc/2uhk8ov0ee?spm=1055.2635.3001.10343)

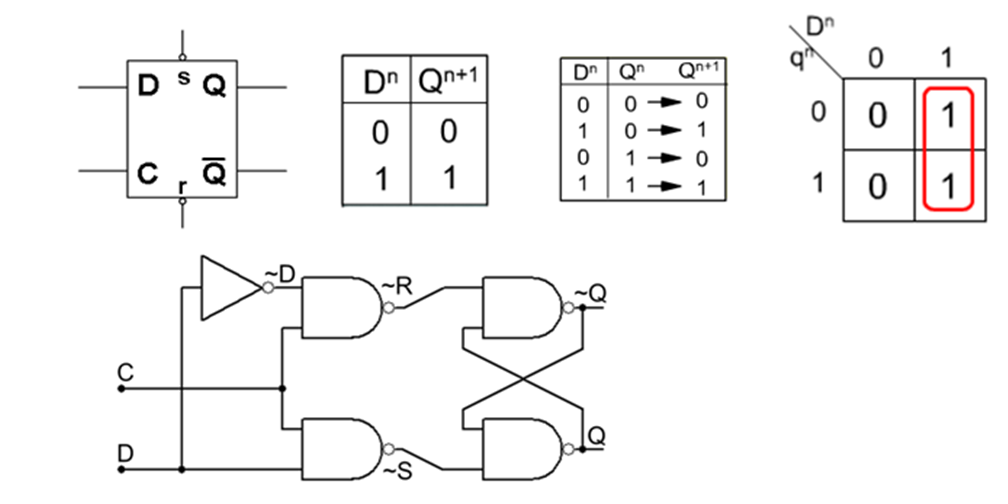

# 1. D触发器的工作原理与重要性

数字电路中,D触发器(D Flip-Flop)是一种广泛使用的时序逻辑电路组件,它在数据存储和时序控制方面发挥着关键作用。D触发器的核心功能是在时钟信号的控制下,捕获并存储输入数据D的状态,并在下一个时钟周期输出该状态。

## 1.1 基本工作原理

D触发器的工作依赖于两个主要信号:数据输入D和时钟脉冲CLK。当CLK的边沿到来(通常为上升沿或下降沿)时,D输入端的逻辑电平会被复制到Q输出端,并持续到下一个时钟脉冲到来。这一过程保证了数据在特定时刻的一致性和稳定性。

## 1.2 重要性与应用

D触发器之所以在数字系统中占有重要位置,是因为它能够有效地同步数据流,防止由于不同步造成的数据冲突和逻辑错误。在设计高速处理器、存储器接口、计数器和移位寄存器等数字电路时,D触发器是不可或缺的基础元件。

通过深入理解D触发器的工作原理,工程师可以更好地构建稳定可靠的数字系统,确保电路在预定的时序下正确地处理和传递数据。

# 2. D触发器故障的分类与诊断

### 2.1 D触发器故障的基本类型

#### 2.1.1 逻辑故障:0变为1,1变为0

逻辑故障发生在D触发器的逻辑电平发生了错误的变化,即本应输出0的时刻输出了1,或者本应输出1的时刻输出了0。这可能是由内部电路故障、外部噪声干扰、电源波动或错误的信号电平造成的。逻辑故障会导致整个数字电路的运行出现错误,比如存储的数据不正确,计数器计数错误等。

**代码块示例:**

```verilog

module logic_fault_example(

input wire clk,

input wire reset_n,

input wire d,

output reg q

);

always @(posedge clk or negedge reset_n) begin

if (!reset_n)

q <= 0;

else

q <= d; // 正常情况下应该是 q <= d;

end

endmodule

```

**参数说明:**

- `clk`:时钟信号输入。

- `reset_n`:低电平有效的复位信号。

- `d`:数据输入。

- `q`:触发器的输出。

**逻辑分析:**

在上述代码中,如果由于某种原因导致`d`信号在某个时钟周期错误地被置为相反电平,比如预期为低电平却变成高电平,那么就会在输出`q`上引起逻辑故障。为避免逻辑故障,需确保在设计、生产和使用阶段都有相应的错误检测机制。

#### 2.1.2 时序故障:时钟边沿不触发或延迟

时序故障通常是指D触发器无法在预期的时钟边沿正常触发,或者触发存在延迟,导致输出信号与输入信号之间的时间差不符合设计要求。这可能是由于时钟信号在传输路径上出现了延迟、损耗,或D触发器本身存在缺陷。

**代码块示例:**

```verilog

module timing_fault_example(

input wire clk,

input wire d,

output reg q

);

reg internal_clk;

always @(posedge clk) begin

internal_clk <= #5 d; // 模拟时钟延迟,正常情况下应直接赋值。

q <= internal_clk;

end

endmodule

```

**参数说明:**

- `clk`:时钟信号输入。

- `d`:数据输入。

- `q`:触发器的输出。

- `#5`:在`internal_clk`的赋值操作中加入5个时间单位的延迟。

**逻辑分析:**

在这个例子中,通过在赋值操作中加入延迟,模拟了时钟信号的延迟到达,这会引起`q`的输出滞后于预期,产生时序故障。在实际应用中,需要严格控制时钟信号的传输延迟,并对时钟信号的质量进行监控,避免时序故障。

#### 2.1.3 电源故障:供电不足或不稳定

电源故障涉及D触发器的电源电压不稳定或不符合规定值。不稳定的电源电压会影响器件的逻辑电平判断和性能表现,可能导致输出不稳定、逻辑错误甚至器件损坏。

**代码块示例:**

```verilog

module power_fault_example(

input wire clk,

input wire d,

output reg q

);

initial begin

$monitor("Time=%0t, q=%b", $time, q);

end

always @(posedge clk) begin

// 模拟电源电压波动影响

if (Vcc > 3.5 || Vcc < 3.0) begin

q <= 1'bx; // 电压异常,输出不确定值

end else begin

q <= d;

end

end

endmodule

```

**参数说明:**

- `$monitor`:模拟电源电压波动时,动态监视输出信号的变化。

- `Vcc`:假设代表电源电压,通常应保持在3.0V至3.5V之间。

- `1'bx`:表示输出不确定值,代表电源故障导致的逻辑错误。

**逻辑分析:**

当模拟电源电压`Vcc`超出正常工作范围时,输出`q`的值不再稳定。在真实电路中,电源故障可能会更隐蔽,因为电源变化可能不总是那么剧烈。要避免这类故障,需在设计时使用电源监控电路,制造时确保电源稳定,使用时监测电源电压变化。

### 2.2 D触发器故障的诊断方法

#### 2.2.1 电压测试:测量工作电压是否在规范范围内

电压测试是诊断D触发器故障时最为基本的方法,目的是确保D触发器的工作电压在规定的范围之内。超出规定范围的电压可能会导致器件损坏或逻辑错误。

**电压测试流程:**

1. **准备设备**:使用万用表或专用电源测试设备。

2. **测量电压**:在设备加电状态下,测量D触发器的供电电压。

3. **对比规格**:将测量值与D触发器的数据手册中规定的电压范围进行对比。

4. **分析结果**:如果测量值超出规定范围,则可能需要检查电源部分的设计和实现。

#### 2.2.2 时序分析:检查时钟信号的准确性和稳定

0

0