【Cortex-M4安全特性分析】:保护你的代码和数据的黄金法则

发布时间: 2024-12-26 13:45:31 阅读量: 6 订阅数: 10

# 摘要

本文全面介绍了Cortex-M4处理器的安全特性及其应用。从处理器概述出发,深入探讨了Cortex-M4的安全架构基础,包括安全性的定义、内存保护机制和加密技术。进一步地,文章详细阐述了Cortex-M4安全特性的实践应用,如安全启动、代码保护、数据安全与传输,以及进阶开发中的定制化安全功能和故障注入防护。最后,针对安全特性的测试与验证,以及未来趋势的探索,包括新兴安全技术和性能与安全平衡的探讨,本文提供了系统性的分析和见解。

# 关键字

Cortex-M4处理器;安全架构;内存保护机制;加密技术;安全测试;漏洞分析;性能平衡

参考资源链接:[ARM cortex-M4参考手册](https://wenku.csdn.net/doc/6412b779be7fbd1778d4a6cc?spm=1055.2635.3001.10343)

# 1. Cortex-M4处理器概述

Cortex-M4处理器是ARM公司推出的一款32位RISC处理器,它结合了高性能和低功耗特性,专为实时应用而设计。由于其出色的性能以及丰富的外设接口,Cortex-M4已成为嵌入式系统领域的热门选择。本章将详细介绍Cortex-M4的架构特点、性能指标以及与前代产品的对比,为后续章节中深入探讨其安全特性和应用打下基础。下面,我们将首先探究Cortex-M4的核心组件,再逐步深入到其安全性的各个方面。

# 2. Cortex-M4的安全架构基础

## 2.1 安全架构理论基础

### 2.1.1 安全性的定义与重要性

安全性的定义是一个广泛而复杂的概念,涉及保护信息免受未授权的访问、使用、披露、破坏、修改或破坏。在信息技术领域,它通常被理解为一系列策略和技术,这些策略和技术确保系统、网络和数据的完整性和机密性。安全性是IT行业中最为核心和关键的要素之一。

从宏观的角度看,安全性对于维持业务连续性、保护用户隐私、确保国家安全和经济稳定至关重要。随着互联网的普及和数字化进程的加快,信息安全问题也日益凸显,由此产生了大量对于安全性的需求和挑战。

### 2.1.2 Cortex-M4的安全特性概览

Cortex-M4处理器作为ARM公司的一款中端微控制器,集成了多种安全功能,以确保嵌入式系统的安全性和可靠性。M4内核采用了ARM v7E-M架构,并增加了数字信号处理(DSP)指令集,以及单精度浮点单元(FPU)以支持复杂的控制应用。

M4的安全特性包括但不限于:

- **TrustZone技术:** 这是一种系统级的硬件隔离技术,能够在芯片层面上创建安全和非安全的执行环境,从而隔离关键的安全操作。

- **加密引擎:** 为数据的加密和解密提供了专用的硬件支持,支持AES、DES、3DES、SHA-1和SHA-256等算法。

- **内存保护单元(MPU):** 该单元提供了灵活的内存访问控制,有助于实现内存隔离和访问权限的管理。

- **安全调试和跟踪功能:** 支持调试过程中的安全访问,确保调试时的安全性。

## 2.2 内存保护机制

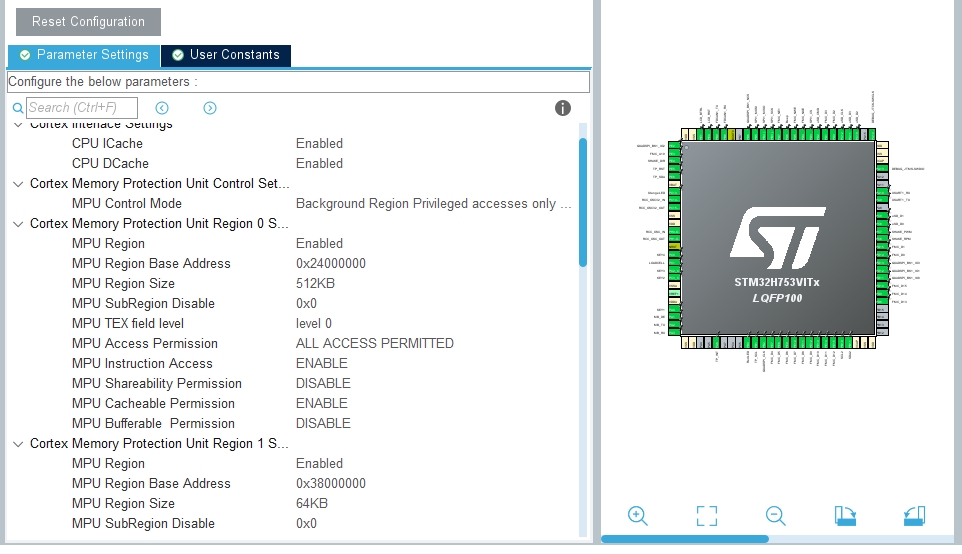

### 2.2.1 内存访问控制(MPU)

内存保护单元(MPU)是Cortex-M4处理器中用于加强内存访问安全的核心机制。其作用是根据系统软件所配置的规则,对内存访问请求进行检查和控制,以防止未授权访问。

MPU允许多个内存区域被定义,并为每个区域设置访问权限。通过这种方式,软件可以限制处理器访问某些内存区域,从而提高系统的安全性。MPU可以在运行时动态更改内存区域的属性,使得软件可以更加灵活地调整内存访问策略。

### 2.2.2 内存保护单元(MPU)的工作原理

MPU工作原理是基于一组内存区域的定义,每个定义都包含一个起始地址、一个大小、以及一组访问权限设置。这些定义被存储在一组特定的寄存器中,称为MPU区域寄存器。处理器在执行内存访问操作时,会通过MPU检查该操作是否符合当前激活的MPU区域定义。

如果一个内存访问请求违反了MPU定义的规则,处理器将触发一个故障,这通常会导致一个异常。异常处理程序可以被用来处理违反访问的情况,比如记录日志、恢复系统状态或者终止违规进程。

为了说明MPU的工作原理,以下是一个简化的例子:

```c

MPU_Region_InitTypeDef MPU_Region;

// 配置MPU区域的起始地址和大小

MPU_Region.Enable = MPU_REGION_ENABLE;

MPU_Region.BaseAddress = 0x20000000;

MPU_Region.Size = MPU_REGION_SIZE_1MB;

MPU_Region.AccessPermission = MPU_REGION_FULL_ACCESS;

MPU_Region.IsBufferable = MPU_ACCESS_NOT_BUFFERABLE;

MPU_Region.IsCacheable = MPU_ACCESS_NOT_CACHEABLE;

MPU_Region.IsShareable = MPU_ACCESS_SHAREABLE;

MPU_Region.Number = MPU_REGION_NUMBER0;

MPU_Region.SubRegionDisable = 0x00;

// 使能MPU并更新区域设置

MPU->RNR = MPU_Region.Number;

MPU->RBAR = MPU_Region.BaseAddress;

MPU->RASR = MPU_Region.Enable | MPU_Region.Size | MPU_Region.AccessPermission |

MPU_Region.IsBufferable | MPU_Region.IsCacheable | MPU_Region.IsShareable |

MPU_Region.SubRegionDisable;

```

通过上述代码,软件开发者可以定义内存访问规则,以保护内存区域不被非法访问。例如,在配置时,开发者可以明确指定某个区域只能被CPU核心访问,而不能通过DMA(直接内存访问)进行访问。

## 2.3 加密与密钥管理

### 2.3.1 加密算法的基本概念

加密是一种将信息转换成不可读形式的技术,以便只有拥有正确密钥的用户才能将其转换回原始信息。加密算法是实现加密的核心,常见的分类包括对称加密、非对称加密和哈希函数。

对称加密算法使用相同的密钥进行数据的加密和解密,其优势在于速度快,效率高,适用于大量数据的处理,但密钥的分发和管理是其主要缺点。

非对称加密(也称为公钥加密)使用一对密钥,一个是公钥,另一个是私钥。公钥可用于加密数据,但只有相应的私钥才能解密。它解决了对称加密中密钥分发的问题,但效率相对较低。

哈希函数(如SHA系列)提供了一种单向加密方式,它们可以将任意长度的输入数据转换成固定长度的输出,这种输出被称为哈希值或摘要。哈希函数在数据完整性验证和数字签名中非常有用。

### 2.3.2 Cortex-M4中的加密引擎与密钥使用

Cortex-M4处理器中的加密引擎是一种硬件加速器,它支持多种加密算法,包括但不限于AES、DES、3DES和SHA。这个硬件加密引擎大大提高了加密操作的效率,减轻了CPU的负担,并确保了加密操作的高性能。

加密引擎通常与TrustZone技术结合使用,这意味着在安全区域内,加密引擎可以用来处理敏感数据,而不会泄露给可能被攻击的非安全区域。此外,加密密钥在硬件中得到保护,不会通过系统总线或内存进行传输,从而减少了密钥被截获的风险。

在使用加密引擎时,密钥管理是一个关键问题。密钥必须被安全地生成、存储和销毁。在Cortex-M4中,可以利用安全的存储设备来保护密钥,或者使用专用的安全固件来管理密钥的生命周期。

下面是一个使用Cortex-M4加密引擎进行AES加密的基本代码示例:

```c

// AES加密配置结构体

AESCrypto_CfgTypeDef AESCfg;

// AES加密输入缓冲区

uint8_t Input[AES_BLOCK_SIZE];

// AES加密输出缓冲区

uint8_t Output[AES_BLOCK_SIZE];

// 加密密钥

uint8_t AESKey[AES_KEY_128BIT_SIZE] = {0};

// 加载加密密钥

AES_SetKey(AESKey);

// 初始化AES加密配置

AESCfg.Algorithm = AES_ALGORITHM_AES_ECB;

AESCfg.KeySize = AES_KEY_128BIT_SIZE;

AESCfg.DataType = AES_DATA_TYPE_128BIT;

AESCfg.pKey = AESKey;

// 设置AES配置

AES_Config(&AESCfg);

// 加密操作

AES_

```

0

0