FPGA原理图设计功耗优化:降低能耗的实战技巧

发布时间: 2025-01-09 12:16:03 阅读量: 12 订阅数: 13

STM32单片机FPGA毕设电路原理论文报告电子竞赛开发板的设计

# 摘要

随着数字电路设计的复杂性增加,FPGA(现场可编程门阵列)的应用越来越广泛,其功耗问题也日益成为设计者关注的焦点。本文首先介绍了FPGA原理图设计中功耗的基础知识,随后探讨了FPGA功耗的分类以及降低功耗的理论基础,涵盖了静态与动态功耗分析、时钟树设计、信号完整性和温度等影响因素。在实践方面,本文详细分析了时钟管理、资源优化、电源设计等方面对功耗控制的重要性,并提出了一系列优化策略。此外,文章还介绍了功耗仿真与测试的技术和方法,以及通过案例分析的方式,总结了成功降低FPGA功耗的实战技巧。通过本文的研究,旨在为FPGA设计者提供有效降低功耗的思路和方法,推动高性能、低功耗FPGA设计的发展。

# 关键字

FPGA;功耗优化;静态功耗;动态功耗;时钟树设计;仿真与测试

参考资源链接:[FPGA原理图设计入门指南:3-8译码器实例与QuartusII操作详解](https://wenku.csdn.net/doc/6not1au20s?spm=1055.2635.3001.10343)

# 1. FPGA原理图设计功耗基础

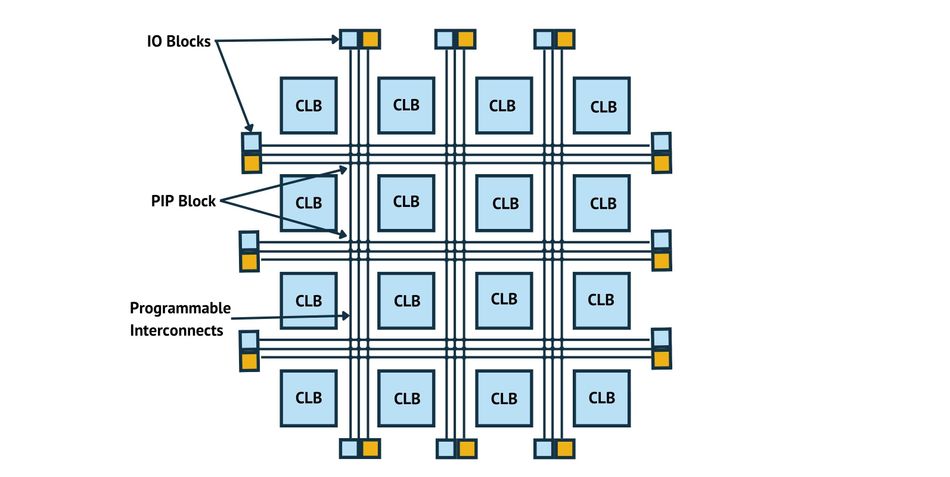

在现代数字系统设计中,FPGA(现场可编程门阵列)由于其灵活可重配置性和高性能,已成为实现复杂逻辑功能的关键组件。然而,随着电路复杂度的增加,FPGA的设计者需要对功耗进行严格控制,以避免过热、延长设备寿命、降低冷却成本,并提高系统的可靠性。

## 1.1 FPGA功耗的重要性

功耗管理是FPGA设计中的核心环节之一,因为在很多应用场景中,如手持设备、航空电子和高频交易等领域,系统的功耗限制对性能的发挥具有决定性的影响。FPGA设计需要在满足性能和功能需求的同时,控制功耗,以达到最佳的能效比。

## 1.2 FPGA功耗的来源

FPGA的功耗主要来自以下几个方面:

- 静态功耗:由晶体管漏电流引起,不依赖于开关活动,随着工艺尺寸的缩小而增加。

- 动态功耗:源于晶体管开关操作时产生的电荷和放电过程,与开关频率和信号变化率相关。

- 短路功耗:晶体管在从导通状态到截止状态切换时,会在电源和地之间形成短暂的短路路径,产生额外功耗。

- I/O功耗:由于FPGA通常具有大量的输入输出引脚,这些引脚上的电容充放电也会对功耗产生影响。

掌握这些基础知识,是进行FPGA功耗分析和优化的前提。后续章节将深入探讨如何在FPGA设计中降低功耗,从理论到实践,为设计师提供一系列有效策略和技巧。

# 2. FPGA功耗构成与优化理论

### 2.1 FPGA功耗的分类

#### 2.1.1 静态功耗分析

静态功耗(也称为漏电流功耗)是由于晶体管本身的物理特性造成的功耗。它是指在没有开关动作的情况下,晶体管仍然会有少量的电流泄漏,导致功耗。在现代FPGA设计中,静态功耗逐渐成为不可忽视的一部分,尤其是在大规模集成时,大量的晶体管工作在亚阈值状态,使得静态功耗占比增大。

静态功耗主要由晶体管的阈值电压和晶体管尺寸决定,阈值电压越低,静态功耗通常越大。而在晶体管尺寸方面,尺寸较大的晶体管静态功耗会更高。此外,温度也是静态功耗的一个影响因素,温度升高会导致漏电流增加,从而增加静态功耗。

为了降低静态功耗,设计者可以采用高阈值电压的晶体管,或者增加晶体管的开启电压。同时,设计中也应考虑降低工作温度,尽管这可能需要额外的散热措施。

#### 2.1.2 动态功耗分析

动态功耗是在FPGA工作时由于晶体管开关动作而产生的功耗。当晶体管从开启状态变为关闭状态,或者相反,会有电流流动,这会导致能量消耗。动态功耗主要与以下几个因素有关:

- 开关频率:晶体管开关动作的频率越高,动态功耗越大。

- 负载电容:晶体管开关时需要充放电的负载电容越大,动态功耗越高。

- 供电电压:供电电压越高,动态功耗越大。

为了降低动态功耗,可以采用降低工作频率、减少负载电容、优化逻辑设计(例如逻辑优化、减少信号反转)以及使用电源管理技术(比如动态电压调整)等策略。

### 2.2 降低FPGA功耗的理论基础

#### 2.2.1 时钟树设计的功耗影响

在FPGA设计中,时钟信号通常需要分配到整个芯片上,由此形成了一个复杂的时钟网络,称为时钟树。时钟树设计对于整个FPGA的功耗有着显著的影响。如果时钟树设计不当,会导致大量的动态功耗,这是因为时钟信号的频繁切换会引起大量的负载电容充放电。

为了降低时钟树设计带来的功耗,可以采取如下措施:

- 使用时钟门控技术,仅在需要时才激活时钟信号。

- 优化时钟树结构,减少时钟缓冲器的数量和大小。

- 调整时钟频率和时钟树的分层,以减少负载电容。

#### 2.2.2 信号完整性和功耗关系

信号完整性是指信号传输过程中保持其形状和大小不变的能力。在FPGA设计中,信号完整性问题可能导致额外的功耗,因为为了纠正信号完整性问题,可能会引入多余的缓冲器和重新驱动电路,从而增加功耗。

设计者可以通过以下方式提升信号完整性,同时减少功耗:

- 优化布线和布局,避免长距离信号传输和信号反射。

- 使用去耦电容来减少电源噪声。

- 使用信号终端匹配技术,减少信号振铃和反射。

#### 2.2.3 温度对功耗的影响

温度是影响FPGA功耗的重要因素之一。温度升高会增加晶体管的漏电流,从而导致静态功耗的增加。此外,动态功耗也会随着温度的升高而

0

0