【编码艺术】:用7段显示译码器实现数字的高效编码

发布时间: 2025-01-04 13:14:42 阅读量: 8 订阅数: 15

# 摘要

本文深入探讨了7段显示译码器的设计基础、编码理论、实现实践、应用拓展以及项目案例分析。首先介绍了7段显示译码器的基本概念和数字系统中的编码基础,然后详细讨论了译码器的逻辑设计、优化译码过程以及硬件与软件的实现方法。接着,本文分析了译码器在多功能数字显示系统中的应用,以及在自动化和信息处理领域的其他应用。最后,通过多个项目案例展示了7段显示译码器的设计和实施过程,总结了项目成功的关键要素,并对未来的技术发展趋势进行了预测。

# 关键字

7段显示译码器;数字编码理论;译码逻辑;硬件实现;软件编程;应用拓展;项目案例分析

参考资源链接:[使用VHDL设计7段数码显示译码器](https://wenku.csdn.net/doc/83fzroa8b8?spm=1055.2635.3001.10343)

# 1. 7段显示译码器基础

## 1.1 译码器简介

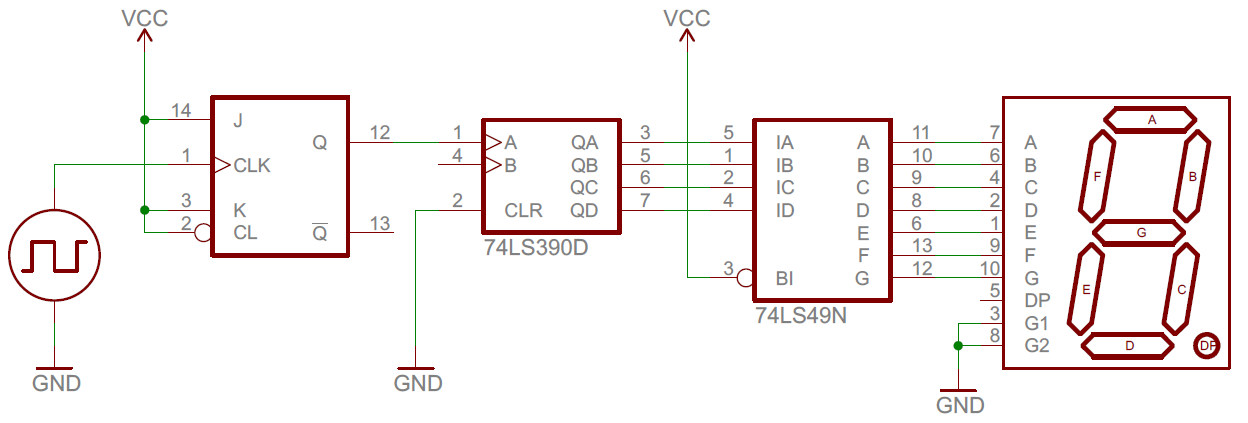

译码器是数字电路中一种重要的组合逻辑设备,它能够将输入的二进制代码转换为相应的输出信号,以驱动显示器或其他设备。在7段显示译码器中,主要任务是将4位二进制数译码为7段显示器上的显示信号。

## 1.2 7段显示器工作原理

7段显示器由7个LED段组成,分别用字母a到g表示。通过控制这七个段的亮灭,可展示0到9的数字以及部分字母。每一个数字对应一组特定的LED段亮起,实现这种对应关系的便是7段显示译码器。

## 1.3 译码器的功能

7段显示译码器的功能是接收二进制输入并将其转换为对应的7段LED显示。例如,二进制的“0111”(即十进制的“7”)会使得a、b、c三个LED段点亮。因此,译码器的核心是实现一个输入到输出的映射关系。

要实现这一功能,译码器将用到逻辑门电路来决定哪些LED应该点亮。接下来的章节,我们会更详细地探讨数字显示编码理论和译码器的设计与实现。

# 2. 数字显示编码理论

数字显示编码理论是构建7段显示译码器的基石。为了深入了解这一主题,本章将首先探讨数字系统与编码基础,接着分析译码器的逻辑设计,最后讨论如何优化译码过程。我们将从理论到实践逐一深入探讨,以确保读者能够透彻理解并应用相关概念。

## 2.1 数字系统与编码基础

### 2.1.1 二进制编码与七段显示器

在数字系统中,二进制编码是最基本的数据表示形式。每一段七段显示器通过独立控制的LED来表示一个二进制数位。这些显示器通常由7个LED灯组成,它们可以被独立点亮或熄灭以显示数字0至9。

以下是常见的七段显示器编码:

| 数字 | a | b | c | d | e | f | g |

|------|---|---|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| ... | ... | ... | ... | ... | ... | ... | ... |

| 9 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

### 2.1.2 常见数字编码方法

除了二进制编码,七段显示器也可以使用其他编码方式,比如BCD(二进制编码的十进制)编码。BCD编码将十进制数的每一位分别编码为四位二进制数,这样可以直接映射到七段显示器上。

例如,十进制的“5”可以表示为BCD码“0101”,每个位直接控制一个段的亮灭:

| 数字 | BCD编码 | a | b | c | d | e | f | g |

|------|---------|---|---|---|---|---|---|---|

| 5 | 0101 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

## 2.2 译码器的逻辑设计

### 2.2.1 逻辑门的作用与组合

译码器的基本工作原理是将输入的二进制数转换为七段显示器上的图形表示。这通常是通过逻辑门电路来实现的。基本的逻辑门包括AND、OR和NOT门。

为了控制七段显示器的每一个LED,我们需要一个译码器逻辑电路,该电路能够基于输入的二进制数(比如BCD码)输出一个对应的高电平或低电平信号到对应的段。

### 2.2.2 译码逻辑与真值表的构建

一个典型的BCD到七段显示器的译码逻辑需要一个真值表,它详细列出了输入的BCD值和七段显示器应该显示的输出:

```plaintext

BCD码 | 显示结果 (a-g)

0000 | 1111110

0001 | 0110000

1001 | 1111001

```

在实际设计中,根据真值表,我们可以构建相应的逻辑电路。比如,当输入BCD为“0000”(十进制的0)时,我们需要点亮除“g”以外的所有段,这可以通过组合不同的逻辑门来实现。

## 2.3 优化译码过程

### 2.3.1 译码器效率的理论分析

效率是译码器设计中的一个关键因素。理论上,一个译码器的效率可以通过它对输入信号的响应时间、功耗和使用的逻辑门数量来衡量。更高效的译码器意味着更少的逻辑门,更快的处理速度和更低的能耗。

### 2.3.2 硬件优化与电路简化技术

为了提高译码器的效率,可以采用硬件优化和电路简化技术。例如,我们可以使用多路复用技术来减少必要的引脚数量,或者通过引入卡诺图简化逻辑表达式来减少所需的逻辑门数量。

以下是简化的逻辑表达式示例:

```plaintext

a = NOT(B) AND NOT(C) AND NOT(D)

b = A AND NOT(B) AND NOT(C) AND D

```

在实际应用中,这将被转换成一系列的逻辑门电路。

我们将继续深入探讨下一章节:3.1 译码器硬件实现。

# 3. 7段显示译码器设计实践

## 3.1 译码器硬件实现

### 3.1.1 基础电子元件选择与布局

在7段显示译码器的设计中,选择合适的电子元件至关重要。基础元件包

0

0