【LabVIEW与Vivado的完美结合】:XILINX 7代XADC软件配置秘籍

发布时间: 2024-12-15 01:34:30 阅读量: 10 订阅数: 13

LabVIEW软件工程动手课程:版本管理与单元测试

参考资源链接:[Xilinx 7系列FPGA XADC模块详解与应用](https://wenku.csdn.net/doc/6412b46ebe7fbd1778d3f91e?spm=1055.2635.3001.10343)

# 1. LabVIEW与Vivado概述

## 1.1 LabVIEW与Vivado简介

LabVIEW和Vivado是美国国家仪器(National Instruments,简称NI)推出的软件和硬件工具,它们是现代电子设计自动化(EDA)的典型代表。LabVIEW是一种图形化编程语言,以其直观的编程环境和强大的数据可视化功能著称,广泛应用于测试、测量和控制领域。Vivado是Xilinx公司开发的一款强大的FPGA设计套件,提供了从设计输入、综合、实现到设备编程的全流程解决方案。

## 1.2 两者集成的必要性与优势

将LabVIEW与Vivado结合使用,可以让工程师轻松设计出高效、可靠的系统原型。LabVIEW提供了一个直观的环境来处理复杂的数据采集、处理和控制任务,而Vivado则确保了这些任务能在FPGA上得到高性能的实现。通过这种集成,工程师能够利用LabVIEW进行快速原型设计,并利用Vivado的强大FPGA开发能力将设计优化和部署到硬件上。此外,这种集成环境还支持高级应用,比如自定义硬件加速、实时信号处理和复杂算法实现,从而缩短产品开发周期,提高最终产品的性能和可靠性。

## 1.3 应用场景及案例概览

LabVIEW和Vivado的集成在各种自动化测试、工业控制、医疗设备和通信系统中有广泛的应用。例如,在需要高速数据采集和实时处理的场合,通过LabVIEW设计控制界面和数据处理流程,同时利用Vivado生成高度优化的硬件逻辑,可以构建出性能卓越且响应迅速的系统。下一章,我们将详细探讨XADC硬件的基础知识和配置,它是实现上述应用的关键技术之一。

# 2. XADC硬件基础与配置

### 2.1 XADC硬件架构详解

#### 2.1.1 XADC的工作原理

Xilinx公司的XADC(Xilinx Analog-to-Digital Converter)模块是集成在某些FPGA内部的双通道模拟数字转换器,它专为处理模拟信号的数字化而设计。XADC模块主要用于FPGA内部环境的监控,如温度、电压等关键参数的实时监测。利用XADC模块,开发者可以实施一些如电源管理、过热保护等功能。

XADC的工作原理是通过其内部的模拟前端对信号进行采样和转换。这个前端包括了17个专用的模拟输入通道,其中两个通道专为内部温度传感器和VCCINT电压监控而设计。XADC可以进行高速和高精度的采样,并且支持连续或单次采样模式。在转换过程中,XADC使用了逐次逼近寄存器(SAR)转换技术,该技术为一种常见的高精度ADC实现方法。

#### 2.1.2 XADC的关键特性

XADC的关键特性包括:

- **双通道操作**:支持同时或交替采样两个模拟输入通道。

- **温度和电压监测**:内置传感器可实时监测芯片温度和核心电压,保证FPGA的稳定运行。

- **12位分辨率**:提供足够的精确度,以满足大多数监控需求。

- **独立的模拟和数字地**:在模拟与数字电路之间提供更好的隔离,减小数字噪声对模拟信号的影响。

- **连续或单次转换模式**:可以根据应用需求选择最适合的采样方式。

### 2.2 硬件接口与引脚配置

#### 2.2.1 引脚分配策略

在进行XADC的硬件设计时,合理分配引脚是十分关键的。首先,应充分理解FPGA的引脚布局,并考虑电源、地、以及高速信号布线对XADC性能的影响。通常,XADC的模拟输入引脚应当尽量远离可能产生干扰的数字信号引脚,并且应当选择靠近FPGA内部XADC模块的引脚。

在进行引脚分配时,还需要考虑FPGA封装的限制,例如不同的引脚可能只能支持模拟信号或数字信号。使用专门的引脚规划工具(如Vivado中的Pin Planner)可以帮助自动分配引脚,并确保引脚布局符合设计要求。

#### 2.2.2 硬件连接和调试技巧

XADC模块的硬件连接不仅包括引脚分配,还包括外围元件的连接,如电阻、电容和电感等。这些元件在提高XADC性能和稳定性方面起着关键作用。为了获得最佳性能,应该确保所有模拟信号路径尽可能短且尽可能远离高速数字信号。

在硬件调试阶段,使用示波器和信号源可以检测模拟输入信号的质量和频率响应。如果需要调试模拟信号的完整性,可以通过串行接口(SPI)读取XADC的状态寄存器,以监控转换结果和内部温度。

### 2.3 软件配置前的准备工作

#### 2.3.1 Vivado环境搭建

在进行XADC配置之前,首先需要在计算机上安装并配置好Xilinx Vivado设计套件。Vivado是Xilinx提供的用于设计FPGA的集成设计环境,集成了逻辑设计、IP集成、仿真、实现以及硬件调试等功能。

在软件配置前,重要的是检查硬件兼容性,确认所使用的Vivado版本支持目标FPGA设备。还需要下载并安装正确的设备特定的包,以确保所有必需的IP和设备模型均可用。

#### 2.3.2 硬件支持与兼容性检查

在使用XADC之前,必须确保硬件环境与XADC的配置要求相符。兼容性检查可以确保FPGA引脚配置与XADC的信号要求不冲突,并确保所有必需的电源电压和参考电压都已正确设置。

以下为一个简单的Vivado环境搭建的示例:

```tcl

# Vivado TCL命令行环境配置

vivado -mode batch -source setup.tcl

# setup.tcl内容示例

# 配置项目路径、设备族和目标FPGA

set project_path [get_property directory [current_project]]

create_project my_project $project_path/my_project -part [lindex [get_parts] 0] -ip

```

上述代码块展示了如何使用TCL脚本在Vivado中配置一个新项目,并指定了项目路径、选择目标FPGA设备族。这些操作都是配置XADC前的必要步骤。

# 3. LabVIEW与Vivado的集成流程

## 3.1 创建Vivado项目与IP核生成

### 3.1.1 初始项目设置

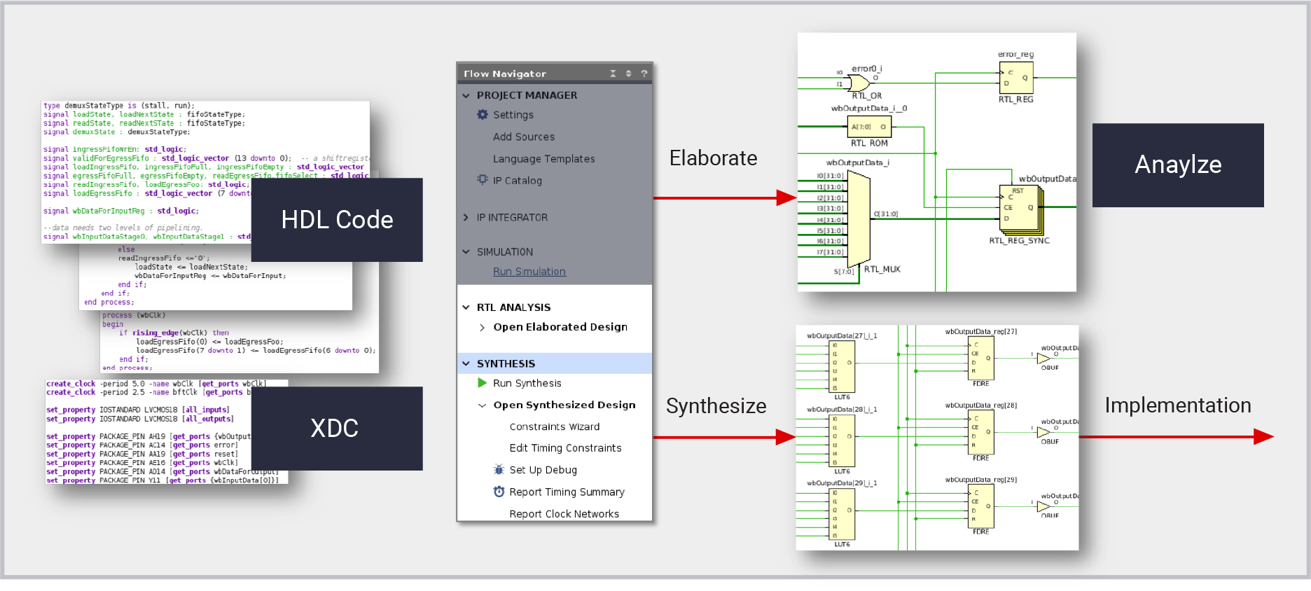

在开始创建Vivado项目之前,需要对FPGA开发板进行基础配置。这通常包括选择正确的硬件描述语言(HDL),设置时钟源,以及决定使用哪些外部接口。对于与LabVIEW集成的项目,还需关注是否已经安装了LabVIEW FPGA模块和Vivado的相关插件。

Vivado项目的创建步骤如下:

1. 打开Vivado软件并选择“Create New Project”。

2. 在“Project Type”页面中选择“RTL Project”,并勾选“Do not spec

0

0