【VIVADO与HLS完美融合】:加速FPGA开发的HLS工具链整合方案

发布时间: 2024-12-28 17:08:30 阅读量: 8 订阅数: 9

# 摘要

本文详细介绍了VIVADO与高层次综合(HLS)工具的综合应用及其必要性。首先,概述了VIVADO环境和HLS设计流程,重点阐述了HLS在VIVADO环境中的集成以及优化技术。随后,深入探讨了VIVADO与HLS之间的协同工作原理和数据交互机制,提供了多个应用实例,涵盖算法实现到FPGA的全流程。本文还分享了进阶应用技巧,包括HLS代码的优化策略和高级特性应用,并通过实际案例展示了性能提升的实践。最后,展望了VIVADO与HLS的未来发展趋势,讨论了在人工智能领域的机会以及所面临的挑战。

# 关键字

VIVADO;HLS设计流程;协同工作原理;性能提升实践;算法实现;FPGA设计;未来发展趋势

参考资源链接:[VIVADO 2021.2 安装教程及验证指南](https://wenku.csdn.net/doc/6i7g38yf7k?spm=1055.2635.3001.10343)

# 1. VIVADO与HLS的概述及必要性

随着FPGA技术的快速发展,硬件描述语言(HDL)的编写对于复杂的算法和大型系统设计来说,变得更加困难。为了解决这一挑战,赛灵思推出了Vivado设计套件,它通过集成高层次综合(HLS)技术,将C/C++语言的编程范式带入到硬件设计流程中。Vivado HLS通过高级抽象层简化了设计过程,使得软件开发者也能参与到FPGA设计中来,从而加快了从概念到硬件实现的迭代速度。

Vivado HLS不仅提高了设计效率,还降低了开发难度,对于需要快速部署和迭代算法的场景尤其有价值。它的必要性体现在以下几个方面:

- **缩短上市时间**:HLS允许快速原型设计和迭代,有助于产品快速上市。

- **提升设计灵活性**:通过C/C++模型,工程师可以更灵活地修改和优化设计。

- **减少硬件知识要求**:HLS降低了对硬件专业知识的依赖,使更多软件工程师能够参与到FPGA项目中来。

接下来的章节将详细介绍Vivado环境下的HLS设计流程,以及如何在实际应用中优化和提升设计性能。

# 2. VIVADO环境下的HLS设计流程

## 2.1 VIVADO环境简介

### 2.1.1 VIVADO的安装与配置

Xilinx VIVADO设计套件是一个先进的综合平台,用于设计可编程逻辑设备,特别是基于7系列及更新的FPGA和Zynq SoC。安装VIVADO之前,用户必须确保他们的计算机满足最低系统要求。这些要求包括足够的RAM(至少16GB推荐)、足够的硬盘空间以及支持的OS版本(例如Windows 10, Ubuntu 16.04 LTS等)。安装过程通常涉及下载安装文件、运行安装程序和配置许可证。

安装步骤包括:

1. 从Xilinx官方网站下载VIVADO安装包。

2. 运行安装向导,接受许可协议。

3. 选择安装组件,例如HLS、逻辑模拟器等。

4. 等待安装完成,并根据提示重启计算机。

5. 配置许可证,可通过网络许可证服务器或使用本地许可证文件。

配置许可证时,用户可以选择使用Xilinx提供的网络许可证服务器,或是使用本地许可证文件进行离线操作。对于没有网络连接或需要在内网环境下工作的用户,离线配置是更为常见的选择。

### 2.1.2 VIVADO界面布局和功能模块

安装完成并重启后,用户将能够启动VIVADO设计套件,并将看到如下的用户界面布局。界面主要分为几大区域:项目树、设计源窗口、控制台窗口、项目概览和设备资源概览等。

1. **项目树(Project Navigator)** - 位于界面左侧,列出了当前打开项目的文件和设置,便于用户进行项目管理和导航。

2. **设计源窗口** - 展示项目的各个源文件,如HDL文件、约束文件等。

3. **控制台窗口(Tcl Console)** - 显示VIVADO执行的Tcl命令的输出,Tcl是一种强大的脚本语言,用于自动化和控制VIVADO的各种操作。

4. **项目概览(Project Summary)** - 提供关于项目关键信息的概述,如逻辑、资源使用情况等。

5. **设备资源概览** - 显示选定FPGA的资源情况,帮助设计师进行资源规划和管理。

VIVADO还包含多种设计工具,例如IP Catalog提供各种IP核供用户集成到设计中;VIVADO Logic Analyzer工具支持逻辑信号的捕获和分析等。

## 2.2 HLS在VIVADO中的集成

### 2.2.1 HLS工具的安装和设置

VIVADO HLS是集成在VIVADO设计套件中的一个模块,它提供了将C/C++代码转换成HDL代码的工具和环境。因此,HLS的安装和设置通常在VIVADO安装过程中同时进行。

安装HLS的步骤大致如下:

1. 在选择安装组件的界面,勾选对应的HLS选项。

2. 继续按照安装向导完成安装。

3. 安装完成后,启动VIVADO并打开一个新项目或导入一个现有项目。

在VIVADO中使用HLS之前,需要进行一些设置:

1. 打开项目设置对话框,通常在"Project"菜单下。

2. 在"Project Settings"对话框中,找到并设置HLS相关的编译器和链接器选项。

### 2.2.2 HLS与VIVADO的数据流接口

在VIVADO环境下,HLS允许用户将C/C++代码转化为硬件描述语言(HDL),并且在VIVADO环境中进行进一步的仿真、综合和布局布线。HLS与VIVADO之间的数据流接口是通过Tcl脚本和项目文件来实现的。

VIVADO支持Tcl命令,Tcl是一种脚本语言,被广泛用于自动化设计流程。在HLS和VIVADO之间进行数据交换时,Tcl命令可以用于:

- 控制HLS工具从VIVADO项目中导出仿真模型。

- 在VIVADO中引用HLS生成的HDL代码。

- 启动和监控HLS流程。

在VIVADO项目中,可以通过点击"Tools" -> "Run Tcl Console"来打开Tcl控制台。之后,使用Tcl命令例如`hls::import`可以将HLS生成的HDL模块导入VIVADO项目中。

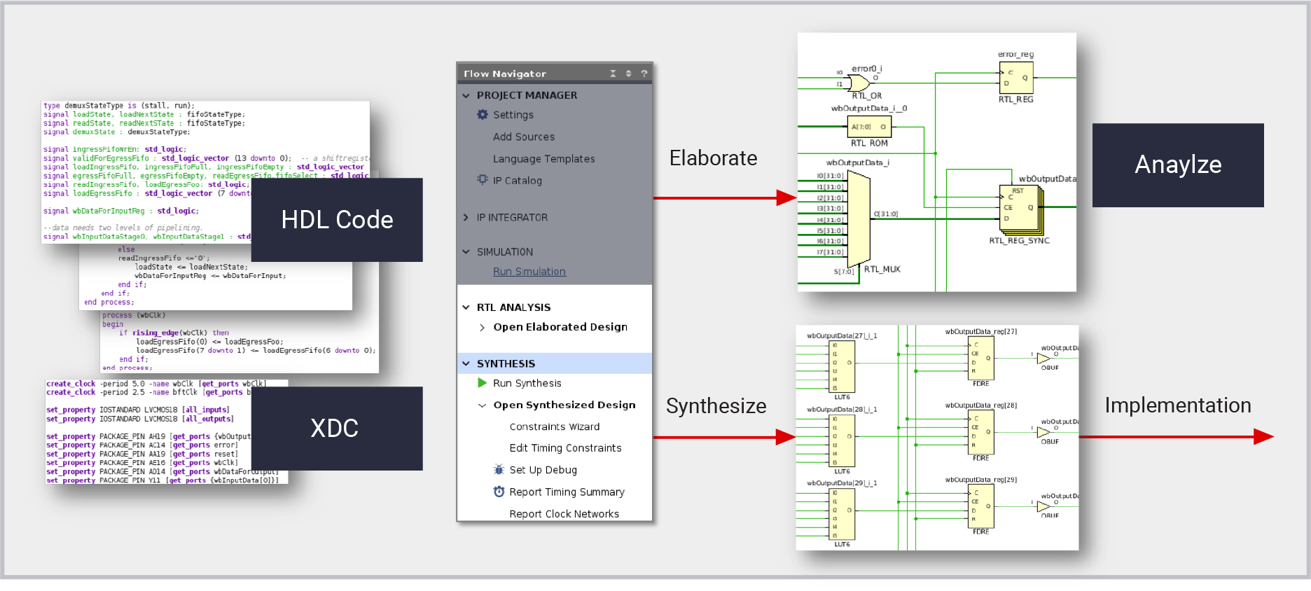

## 2.3 HLS设计流程详解

### 2.3.1 C/C++代码到硬件的转换过程

C/C++到硬件的转换是HLS的核心功能。整个转换过程大致可以划分为以下几个步骤:

1. **编写C/C++代码**:首先,设计者需要编写满足算法需求的C/C++源代码。

2. **添加HLS指令**:使用HLS指令对源代码进行注释,以指导综合过程,比如指定循环展开、管道化等。

3. **编译源代码**:使用Vivado HLS编译器将源代码编译成HLS对象。

4. **仿真测试**:在HLS环境中运行C仿真,验证算法的正确性。

5. **综合和优化**:综合过程将C代码转换为硬件描述,并进行时序优化和资源优化。

6. **生成HDL代码**:综合完成后,生成VHDL或Verilog HDL代码。

7. **仿真验证**:使用生成的HDL代码在Vivado环境中进行仿真验证。

这个过程的每个步骤都是可配置的。开发者可以根据具体的设计需求和资源限制,对HLS编译器的行为进行调整。这包括调整时钟周期、资源共享策略,以及内存访问方式等。

### 2.3.2 HLS流程中的优化技术

为了达到设计目标,HLS流程中通常需要进行多种优化技术来改善性能、减少资源消耗或降低功耗。一些常见的优化技术包括:

- **循环优化**:通过循环展开、循环融合、循环划分等技术来减少循环开销。

- **数据流优化**:通过流水线、缓冲器插入、数据重排等技术来提升数据吞吐量。

- **存储优化**:通过优化存储结构和访问模式来减少存储资源的使用。

- **时序优化**:通过调整模块划分、时钟域划分等技术来满足时序要求。

优化往往是一个迭代的过程,可能需要多次迭代综合和仿真来找到最佳的优化参数。在进行优化时,必须注意保持设计功能的正确性,这需要仔细地进行功能仿真和时序分析。

在VIVADO中,可以通过Tcl命令或图形界面设置优化策略。例如,`hls::set_directive_loop_pipeline`用于设置循环的流水线优化,而`hls::set_directive_pipeline`用于设置模块的流水线优化。

```tcl

# 示例:设置流水线优化指令

hls::set_directive_pipeline -unroll 4 my_hls_function

```

代码块展示了如何使用Tcl命令设置函数my_hls_function的流水线,并展开循环至4次迭代。这有助于提高数据吞吐量,特别是在存在大量重复计算的场合。

# 3. VIVADO与HLS的协同工作原理

## 3.1 HLS与VIVADO的数据交互机制

在FPGA开发流程中,HLS(高层次综合)和VIVADO是两个紧密协作的环节。它们之间的高效数据交互机制是确保设计流程顺畅的关键。HLS与VIVADO之间的交互主要发生在设计规范的传递和综合以及优化信息的反馈这两个阶段。

### 3.1.1 设计规范的传递

在HLS工具

0

0