STM32F407时钟管理与性能优化:7个技巧助你提升效率

发布时间: 2024-12-04 11:26:40 阅读量: 38 订阅数: 46

STM32F407实现FreeRTOS内存管理【支持STM32F40X系列单片机】

参考资源链接:[STM32F407中文手册(完全版) 高清完整.pdf](https://wenku.csdn.net/doc/6401aba5cce7214c316e8fc8?spm=1055.2635.3001.10343)

# 1. STM32F407时钟系统概述

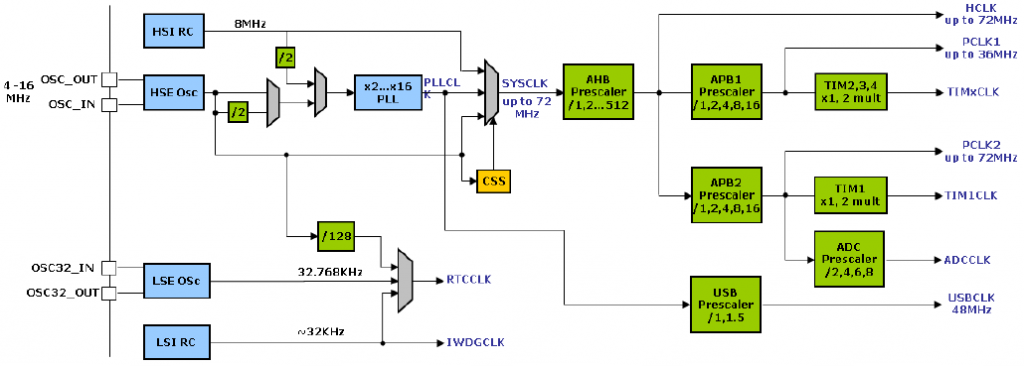

## 系统架构简介

STM32F407微控制器拥有灵活且强大的时钟系统,它为各种外设提供时钟源。该系统包括内部高速时钟(HSI)、外部高速时钟(HSE)、相位锁定环(PLL)以及时钟安全系统(CSS)。理解这些组件的工作原理和它们如何配置对于开发高性能嵌入式应用程序至关重要。

## 时钟系统的重要性

在任何基于微控制器的系统中,时钟系统扮演着心脏的角色,负责为CPU和外设提供准确的时序。通过有效地配置STM32F407的时钟系统,开发者能够优化设备的性能和功耗,保证应用运行的可靠性和稳定性。

## 本章目标

本章节将为读者提供STM32F407时钟系统的基础知识,为后续章节中探讨高级配置和性能优化打下坚实基础。我们将从时钟源的基本概念开始,逐步深入到时钟树的配置以及CSS的作用,使读者能够全面掌握时钟系统的核心功能。

# 2. 时钟配置技巧

## 2.1 时钟源选择与配置

### 2.1.1 内部时钟源(HSI)配置

STM32F407的内部高速时钟源(HSI)是出厂预置的8MHz RC振荡器。HSI被默认作为系统时钟源,当外部时钟源(HSE)或锁相环(PLL)出现问题时,HSI能够保证设备的正常运行。

在配置HSI时,首先需要确保HSI时钟源是使能状态。在代码层面,这通常通过以下代码段完成:

```c

RCC->CR |= RCC_CR_HSION; // 设置HSI使能

while ((RCC->CR & RCC_CR_HSIRDY) == 0) {} // 等待HSI就绪

```

在进行HSI配置时,`RCC_CR_HSION`是一个按位操作指令,用于设置HSI使能位。紧接着的一行代码是一个空循环,它的作用是等待HSI振荡器稳定运行,此时`RCC_CR_HSIRDY`标志位会被硬件置位。配置完成后,HSI即可作为系统时钟源,或者作为PLL的输入源。

### 2.1.2 外部时钟源(HSE)配置

外部时钟源(HSE)可以是一个外部的晶振或外部的时钟信号。使用HSE的好处是它通常能提供比内部RC振荡器更加准确和稳定的时钟频率。

配置HSE时,需要先将HSE振荡器使能,然后等待其稳定:

```c

RCC->CR |= RCC_CR_HSEON; // 设置HSE使能

while ((RCC->CR & RCC_CR_HSERDY) == 0) {} // 等待HSE就绪

```

当使用HSE时,可以根据需要选择一个适当的时钟频率。若使用外部晶振,该晶振的频率应该在4MHz到25MHz之间。一旦HSE就绪,就可以选择它作为PLL的输入源或直接用作系统时钟。

## 2.2 PLL和时钟树优化

### 2.2.1 PLL参数设置与调整

PLL(相位锁定环)是用于倍频HSI或HSE的时钟源,以达到更高的系统时钟频率。STM32F407的PLL可以提供很灵活的时钟设置。

配置PLL时,需要设置以下参数:

- PLL的输入时钟源频率(由HSI或HSE提供)。

- PLL的乘数因子(M)。

- PLL的分频因子(N)。

- 主要分频因子(P、Q、R)。

这些参数可以通过`RCC_PLLCFGR`寄存器来配置。例如,若想将PLL的输出时钟设置为168MHz,可以如下操作:

```c

RCC->PLLCFGR = RCC_PLLCFGR_PLLSRC_HSE // 设置PLL源为HSE

| (25 << RCC_PLLCFGR_PLLM_Pos) // M = 25

| (336 << RCC_PLLCFGR_PLLN_Pos) // N = 336

| (7 << RCC_PLLCFGR_PLLP_Pos) // P = 7

| (RCC_PLLCFGR_PLLQ_2); // Q = 2

RCC->CR |= RCC_CR_PLLON; // 设置PLL使能

while ((RCC->CR & RCC_CR_PLLRDY) == 0) {} // 等待PLL就绪

```

通过以上设置,我们设定了PLL的输入源为HSE,M为25,N为336,P为7,Q为2。当`RCC_CR_PLLRDY`位被硬件置位时,表示PLL已经稳定并且可以作为系统时钟源。

### 2.2.2 时钟树的配置与性能考量

时钟树的配置对系统的整体性能和功耗都有显著影响。STM32F407的时钟树提供了多样化的时钟分支和分频选项,可以优化不同外设的时钟供给。

合理配置时钟树应遵循以下原则:

- 尽可能使用低的时钟频率满足外设需求,以降低功耗。

- 根据外设的工作频率要求,选择合适的时钟源。

- 若对实时性有高要求,应优先考虑使用PLL。

配置时钟树时,还应注意以下方面:

- **时钟同步**:对于需要与其它外设同步工作的模块,确保它们共享相同的时钟源。

- **时钟切换**:在需要时钟源切换时,应确保旧时钟源完全关闭后,再切换到新的时钟源。

- **时钟管理器**:使用STM32F407的时钟管理器(如PWR和RCC)来管理时钟的开启、关闭和切换。

在实际应用中,通过对时钟树的精细配置,可以得到一个高效、低功耗的系统时钟架构。

```mermaid

graph TD

A[启动] --> B[HSI使能]

B --> C{HSE使能}

C -->|是| D[PLL配置]

C -->|否| E[HSE配置]

D --> F[时钟树配置]

E --> F

F --> G[系统时钟选择]

```

图表展示了从启动到系统时钟选择的过程,通过条件选择不同路径,展示时钟的配置流程。

## 2.3 时钟安全系统(CSS)

### 2.3.1 CSS工作原理及配置

时钟安全系统(Clock Security System, CSS)是一种监视外部晶振(HSE)是否稳定的机制。当CSS检测到外部晶振频率异常时,它会自动切换到内部高速时钟(HSI),保证系统正常运行。

CSS的配置相对简单。通常只需要在系统启动时使能CSS功能:

```c

RCC->CR |= RCC_CR_CSSON; // 使能时钟安全系统

```

一旦HSE时钟出现故障,CSS将自动切换至HSI,并在`RCC->CR`寄存器的CSS位中反映状态变化,软件可以查询此位来得知是否发生了切换。

### 2.3.2 CSS在异常情况下的时钟切换

在CSS检测到外部晶振(HSE)故障时,系统会立即切换到内部高速时钟(HSI),并设置相应的状态标志位。在切换后,系统软件应该检查CSS标志位来确认切换原因,并进行相应的处理。

```c

if (RCC->

```

0

0