案例分析:Cadence Allegro板边设计问题的快速诊断与解决

发布时间: 2024-12-15 14:48:35 阅读量: 2 订阅数: 4

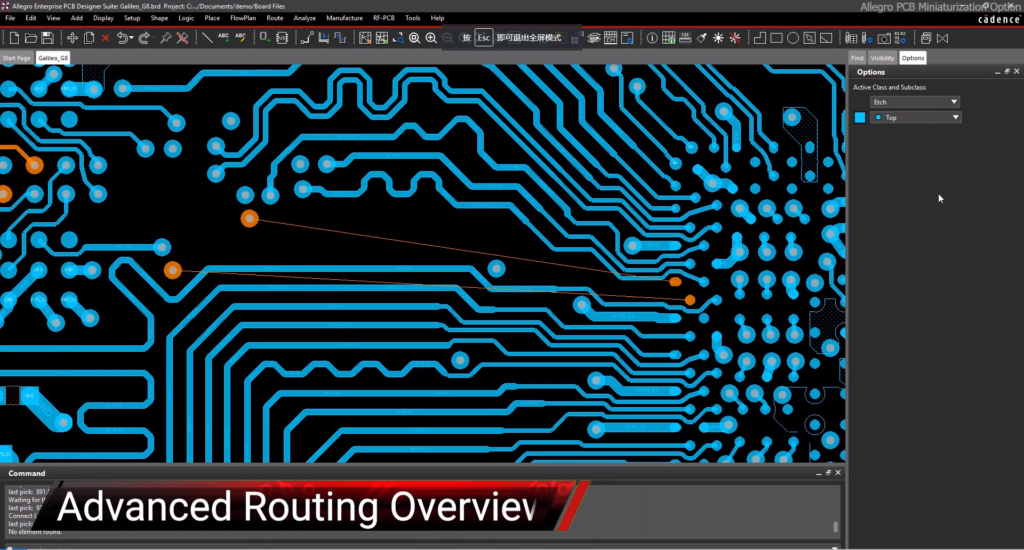

Allegro系列PCB设计工具具体操作方法

参考资源链接:[cadence allegro里如何绘制板边outline](https://wenku.csdn.net/doc/6412b621be7fbd1778d459e4?spm=1055.2635.3001.10343)

# 1. Cadence Allegro板边设计概述

电子工程师和PCB设计师们在使用Cadence Allegro进行板边设计时,通常面临着多方面的挑战。本章将为您概述Cadence Allegro在板边设计中的基本应用,帮助您从整体上把握其在设计过程中的重要性以及如何在实际工作中应用。

## 1.1 Cadence Allegro简介

Cadence Allegro是一款广泛应用于复杂电子系统设计的软件,特别是在印刷电路板(PCB)设计方面,它提供了一系列功能强大且精确的设计工具。在板边设计中,其关键作用体现在布局布线、信号完整性分析和制造数据生成等方面。

## 1.2 板边设计的作用与挑战

板边设计是PCB设计的重要组成部分,它涉及将各种电子元件放置在电路板的外围,以便于组装和维护。设计师需要在确保电路性能的同时,考虑到制造的可行性以及后续的热管理问题。

## 1.3 Cadence Allegro在板边设计中的应用

利用Cadence Allegro进行板边设计,设计师可以进行电路的布局布线,利用DRC(设计规则检查)来确保设计满足各种制造业标准和电气要求。在设计过程中,还可以运用信号完整性(SI)和电源完整性(PI)分析工具来验证电路设计的性能。

Cadence Allegro不仅仅是一个设计工具,它的智能化特性还可以帮助设计师在设计阶段快速发现并解决潜在问题,从而提高设计质量并缩短产品的上市时间。本章内容旨在为读者提供一个关于Cadence Allegro在板边设计中应用的概览,为后续深入探讨具体的板边设计问题打下基础。

# 2. 板边设计问题的理论分析

## 2.1 问题识别与类型分类

在深入分析之前,理解板边设计中可能遇到的问题及其分类是至关重要的。这有助于设计者在面对复杂的设计挑战时,能够迅速定位问题的根源。

### 2.1.1 电气特性相关问题

电气特性相关的问题通常源于设计的不当,可能对电路板的性能产生负面影响。这些问题包括但不限于:

- **阻抗不匹配**:阻抗的不一致性会导致信号反射和传输线上的信号强度不一,从而降低信号质量。

- **串扰**:相邻线路之间电场或磁场的相互作用,可能会导致信号间的干扰。

- **电源噪声**:电源线上出现的高频噪声,可能会影响电源完整性,导致电路性能下降。

### 2.1.2 制造工艺相关问题

制造工艺的问题通常是在生产过程中由于不恰当的设计或制造缺陷而引起的。这些问题可能包括:

- **层压对齐不良**:多层板的层压过程中由于对齐不良可能会导致短路或者开路。

- **钻孔和铣削误差**:孔位精度、过孔和轮廓的不精确铣削可能会影响组装的精度和可靠性。

- **焊盘设计不当**:不当设计的焊盘可能会导致焊接不良,影响最终产品的可靠性。

### 2.1.3 热管理与散热问题

随着电子设备的性能不断提升,热管理变得越来越重要。散热问题通常包括:

- **热膨胀系数不匹配**:材料间的热膨胀系数不匹配可能会在温度变化时导致裂纹或断线。

- **散热不足**:设计中没有合理布局散热器或者热导管,可能会导致组件工作温度过高,影响其性能和寿命。

## 2.2 设计规则检查(DRC)的重要性

设计规则检查(Design Rule Check, DRC)是确保板边设计符合制造和功能要求的关键步骤。

### 2.2.1 设计规则的定义与遵循

DRC的目的是确保板边设计符合一系列事先定义的设计规则,这些规则包括最小线宽、间距、钻孔尺寸等。设计者必须遵循这些规则以避免制造和操作中的问题。

### 2.2.2 DRC失败的常见原因及后果

DRC失败的常见原因有以下几点:

- **设计错误**:如错误的焊盘尺寸或不正确的组件放置。

- **规则配置不当**:DRC规则配置不当可能导致设计表面上通过但实际上包含潜在问题。

如果DRC失败未被识别和修正,可能会导致以下后果:

- **重工成本增加**:在制造后才识别出的设计问题可能需要重工,增加成本。

- **产品上市时间延迟**:设计问题的修正可能造成产品上市时间的延误。

## 2.3 信号完整性和电源完整性分析

板边设计中,信号完整性和电源完整性是影响电路性能的两个关键因素。

### 2.3.1 信号完整性问题的影响

信号完整性问题会影响电路的性能和可靠性,具体表现在:

- **信号时序问题**:信号传输时的延迟可能导致时序错乱,影响系统的同步性。

- **信号质量下降**:信号反射、串扰等问题会导致信号质量下降,影响数据传输的准确性。

### 2.3.2 电源完整性分析方法与实践

电源完整性分析的目的是确保电源网络可以提供稳定、干净的电源,避免电源噪声和过冲/下冲问题。分析和实践通常包括:

- **电源层和地层设计**:合理的电源层和地层设计可以改善电源完整性。

- **去耦电容布局**:在IC引脚附近布局去耦电容,可以减少电源噪声,提高电源的稳定性。

在分析过程中,通过一系列的仿真和测试可以验证设计的电源完整性,从而确保电路板在实际工作中的性能符合预期。

以上章节详细阐述了板边设计中问题识别与类型分类的重要性,并且深入探讨了设计规则检查(DRC)的关键作用及其失败的后果。最后,我们分析了信号完整性和电源完整性分析的方法和实践。通过对这些理论知识的了解,设计师可以更好地为实际的设计工作做好准备,为后面的诊断工具与方法章节打下坚实的基础。

# 3. 板边设计问题的诊断工具与方法

## 3.1 使用Cadence Allegro内置工具

### 3.1.1 ERC与LVS工具的介绍

在板边设计流程中,电气规则检查(Electrical Rule Check, ERC)与布局与原理图对比(Layout Versus Schematic, LVS)是两个至关重要的内置工具。ERC专注于验证设计中的电气连接是否符合设计规则,而LVS则主要用于比较电路板的物理布局和其对应的电路原理图,以确保两者的同步一致性。

ERC工具能够检查诸如开路、短路以及悬空节点等问题,这对于保证电路板的电气性能至关重要。同时,它还能识别违反设计规范的电气连接,如电压和电流限制、信号完整性问题等。

LVS工具是电路设计的后端检查,它的基本检查流程包括:元件匹配、网络连接一致性和布局拓扑结构的一致性检查。在板边设计中,LVS能够确保布局设计的每个物理连接在原理图中有相对应的表示,反之亦然。

### 3.1.2 交互式问题诊断流程

ERC与LVS工具不单是自动化的检查程序,它们还提供了交互式的问题诊断功能。当工具报告错误或警告时,设计师可以通过工具提供的界面直接定位到问题发生的位置。以下是一个典型的诊断流程:

1. **错误分析**:系统分析工具报告的错误列表,并尝试理解错误的上下文。

0

0