STM32F407多核系统协同:数据手册中的MPU支持实战解读

发布时间: 2024-12-16 02:41:01 阅读量: 3 订阅数: 6

STM32F407固件库-加速度陀螺仪—MPU6050.zip

参考资源链接:[STM32F407 Cortex-M4 MCU 数据手册:高性能、低功耗特性](https://wenku.csdn.net/doc/64604c48543f8444888dcfb2?spm=1055.2635.3001.10343)

# 1. STM32F407多核系统概述

STM32F407作为STMicroelectronics(意法半导体)推出的一款高性能的ARM Cortex-M4内核微控制器,其多核系统特性使其在处理速度和任务管理方面有着显著优势。本章我们将探索STM32F407多核系统的核心概念,以及它如何在复杂的工业和消费电子应用中提升性能和可靠性。

STM32F407的多核架构允许同时执行多个任务,这在处理音频、视频、传感器数据和无线通信等实时任务时显得尤为重要。这一架构支持高效的任务管理和内存隔离,确保了系统运行的稳定性与安全性。此外,我们还将介绍多核系统在编程和系统集成中的一些基本概念,为后续章节中对MPU的深入讨论打下坚实的基础。

# 2. MPU和内存管理基础

## 2.1 MPU的作用与优势

### 2.1.1 MPU在多核系统中的角色

在多核系统中,存储器保护单元(MPU)扮演着至关重要的角色。它负责管理不同处理器核心的内存访问权限,确保数据的一致性和系统资源的隔离。每个核心可以拥有自己的内存区域,这些区域可以被MPU单独保护,防止其他核心的非法访问,这对于维护系统的稳定性和数据的安全性是至关重要的。

MPU通过设置内存访问权限来实现这一目标,比如它可以指定某个内存区域只能被特定的核心读取或写入,而其他核心则被禁止访问。在多核系统中,当多个核心同时访问共享资源时,MPU能够确保数据的一致性不会因并发访问而被破坏。

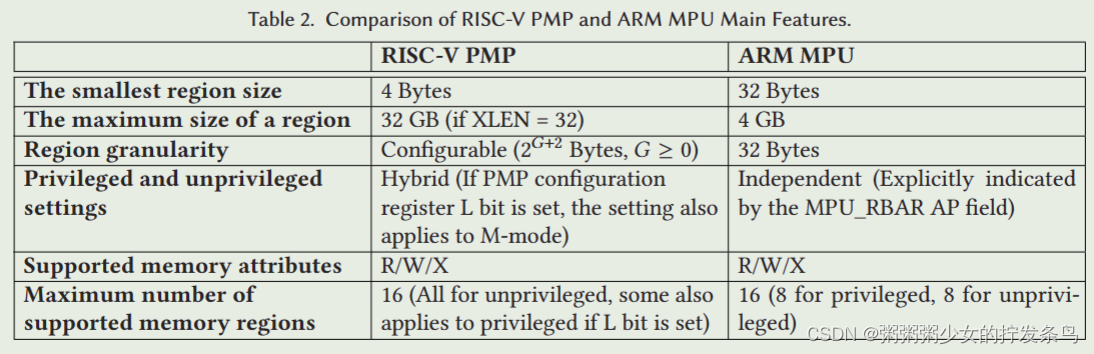

### 2.1.2 MPU相对于其他内存保护技术的提升

MPU相较于传统的内存管理单元(MMU)提供了更为灵活和高效的内存保护。MPU不涉及虚拟内存管理,它只对物理地址空间进行操作,这使得它在实时系统和资源受限的环境中表现出色。它的配置通常比MMU简单,能够快速地启用和配置,这对于需要快速响应和高效率执行的任务尤为重要。

MPU还提供了细粒度的内存访问控制,允许开发者定义小到512字节的内存区域,而MMU通常是基于页(通常是4KB或更大)进行操作。这种细粒度控制使得MPU非常适合用于嵌入式和专用系统,其中资源的精细分配至关重要。

## 2.2 内存管理的基本概念

### 2.2.1 内存访问权限控制

内存访问权限控制是内存管理中的基础,它定义了哪些处理器核心或者进程可以访问某个内存区域,并且能定义它们的访问类型,如只读、只写或读写权限。在多核系统中,对内存访问权限的精确控制能够有效避免非法访问和潜在的数据冲突。

为了实现内存访问权限控制,系统设计者通常会在硬件层面实现一些机制,比如MPU。通过设置MPU的寄存器,可以定义不同内存区域的访问权限。例如,某个内存区域可以设置为只供核心A读取,核心B则只能写入该区域,而核心C则完全无法访问该区域。这样的配置在系统初始化时完成,并在运行时监控访问请求,确保所有访问请求都符合设置的权限。

### 2.2.2 缓存和一致性管理

缓存是现代计算机系统中常见的组件,它提供了一种加快数据访问速度的方法。通过在处理器核心和主存之间存储常用数据的副本,缓存减少了访问主存的次数,从而提升了系统的性能。然而,缓存的使用也带来了数据一致性的挑战,特别是在多核系统中。

在多核系统中,每个核心可能都有自己的缓存,这就造成了数据副本可能存在于多个缓存中。为了解决这一问题,现代处理器采用了一系列的技术,包括缓存一致性协议(如MESI协议),它们确保了所有核心看到的内存数据是一致的。MPU在这一过程中起到了辅助作用,它可以根据缓存策略来设置内存区域的访问权限,指导处理器如何处理缓存一致性问题。

## 2.3 STM32F407中的MPU实现

### 2.3.1 MPU的寄存器结构和配置

STM32F407微控制器中集成了MPU,其设计允许对内存访问权限进行细致的控制。MPU由一系列的寄存器组成,其中包括主寄存器MPU_TYPE,区域寄存器MPU_RBAR和区域属性和大小寄存器MPU_RASR。通过这些寄存器的配置,系统设计者可以定义多达8个内存区域,每个区域可以独立地设置访问权限和大小。

配置MPU时,开发者首先需要确定哪些内存区域需要保护以及它们的访问权限。然后,根据MPU_RBAR寄存器中的区域基础地址和MPU_RASR寄存器中的区域大小字段来设置内存区域的起始地址和大小。最后,通过设置MPU_RASR寄存器中的访问权限位,来定义对该内存区域的访问策略。

### 2.3.2 MPU与ARM Cortex-M4的集成

ARM Cortex-M4是STM32F407微控制器的核心,它与MPU的集成提供了强大的内存保护和管理能力。Cortex-M4为MPU提供了丰富的支持,包括多个可编程的内存区域、可配置的访问权限和专门的异常处理机制。

在集成时,MPU配置与Cortex-M4的执行模式相关联。例如,可以设置某个内存区域仅在特权模式下可访问,而用户模式则无法访问。这种配置能够保护操作系统和关键数据,防止应用程序错误访问或修改。另外,当发生MPU违规访问时,Cortex-M4能够产生一个异常,将控制权转移给相应的异常处理程序,从而允许系统开发者对违规行为进行处理。

在接下来的章节中,我们将更深入地探讨如何在STM32F407上进行MPU的配置与编程实践,通过实际的代码示例和逻辑分析来展示如何利用MPU提升多核系统的性能和安全性。

# 3. MPU的配置与编程实践

随着多核系统的不断发展,内存保护单元(MPU)的配置与编程实践变得越来越重要。本章将详细介绍如何在STM32F407这样的多核系统上,通过软件编程来实现和优化MPU的功能。

## 3.1 MPU的初始化和基本配置

### 3.1.1 启用MPU的步骤和注意事项

在任何尝试配置MPU之前,首先需要确保MPU已被正确初始化。通常,这涉及到在系统的启动代码中进行几步操作。以下是一些关键步骤和注意事项:

1. **确保系统时钟配置支持MPU:**在STM32F407中,MPU依赖于特定的系统时钟配置。必须确保CPU核心的时钟配置既满足运行频率的要求,也支持MPU的工作频率。

2. **MPU使能:**在Cortex-M4处理器中,MPU的启用通过编程SCB_SHPR3寄存器来实现。将该寄存器的MPUENA字段设置为1即可启用MPU。

3. **寄存器预设:**在启用MPU之前,推荐对MPU的各个区域寄存器进行预设,以便在启用后MPU可以立即根据预设的规则来控制内存访问。

4. **错误处理机制准备:**在启用MPU之前,还应确保已经配置好了相应的异常处理机制,以便能够妥善处理内存访问违规。

### 3.1.2 配置内存区域和访问权限

配置MPU的内存区域及相应的访问权限,是利用MPU保护内存安全的关键步骤。STM32F407中每个MPU区域由一组寄存器定义:

```c

typedef struct {

uint32_t rbar; // Region Base Address Register

uint32_t rasr; // Region Attribute and Size Register

// 可能还有其他相关寄存器

} MPU_

```

0

0