【Aurora 64B_66B IP核实战手册】:构建高效的FPGA数据链路

发布时间: 2024-12-21 23:43:32 阅读量: 5 订阅数: 6

aurora 64B/66B ip 核设置与例程代码详解

# 摘要

本文旨在全面介绍Aurora协议在高性能数据链路中的应用,首先概述了Aurora协议的基础知识,然后深入探讨了FPGA(现场可编程门阵列)在实现Aurora协议中的关键作用,包括其硬件架构、数据传输机制及电源和热设计。接着,文章详细阐述了Aurora IP核的集成、配置、测试与验证过程,并提供了软件接口开发和实际应用案例的深入分析。最后,本文探讨了Aurora数据链路的优化和调试技巧,包括信号完整性、调试技巧、性能调优与故障排除,旨在提供一系列实用的技术指南,帮助工程师高效地部署和优化基于Aurora协议的数据链路。

# 关键字

Aurora协议;FPGA;数据链路;IP核集成;软件驱动;信号完整性

参考资源链接:[Aurora 64B/66B IP核设置与代码详解:速率配置与例程指南](https://wenku.csdn.net/doc/6412b549be7fbd1778d429be?spm=1055.2635.3001.10343)

# 1. Aurora协议概述

## 1.1 Aurora协议简介

Aurora协议是一种串行数据链路通信协议,主要用于FPGA(现场可编程门阵列)和ASIC(应用特定集成电路)之间的高速数据传输。它是Xilinx公司开发的一种专有协议,广泛应用于高性能计算、实时数据传输和存储系统等领域。

## 1.2 Aurora协议的优势

Aurora协议之所以得到广泛应用,主要得益于其高效的通信能力和灵活的配置选项。协议支持高达100Gbps的传输速率,同时保持较低的延迟和较高的可靠性,是构建高性能数据链路的理想选择。

## 1.3 Aurora协议的应用场景

在数据中心、云计算、网络通信、雷达和声纳系统以及医疗成像设备中,Aurora协议都能发挥其强大的数据传输能力。其协议的灵活性和可扩展性,使得它能够适应各种复杂的工作环境,满足不同的业务需求。

以上是对Aurora协议的概述,为您描绘了这一协议在现代IT和高科技行业中扮演的核心角色。第二章将深入探讨FPGA硬件的基础知识,为理解Aurora协议在硬件层面的工作提供必要的技术背景。

# 2. FPGA硬件基础知识

## 2.1 FPGA的基本概念和架构

### 2.1.1 FPGA的定义及其工作原理

FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种可以通过编程实现特定逻辑功能的半导体器件。FPGA能够实现硬件电路的可重配置性,允许工程师根据应用需求对其进行编程,以实现定制的数字逻辑功能。其核心在于现场可编程的灵活性,与传统ASIC(应用特定集成电路)相比,FPGA在设计周期、成本和功耗方面具有显著优势。

FPGA的基本工作原理依赖于可编程逻辑单元(Logic Cells)以及它们之间的互连资源。用户通过设计输入(如VHDL或Verilog代码)来配置逻辑单元和互连网络,FPGA将这些配置加载到静态存储器(SRAM)中。因此,FPGA的配置在断电后会丢失,每次上电都需要重新配置。

**代码块示例**:

```verilog

module basic_fpga_function(

input clk,

input reset,

input [3:0] in_data,

output reg [3:0] out_data

);

always @(posedge clk or posedge reset) begin

if (reset)

out_data <= 0;

else

out_data <= in_data; // Simple passthrough logic

end

endmodule

```

### 2.1.2 FPGA的硬件资源和设计层次

FPGA的硬件资源包括逻辑单元、存储器块、DSP模块、I/O模块等。这些资源在FPGA中被组织成多层次的设计结构,从底层的可编程逻辑单元到高层的设计抽象,如IP核(Intellectual Property Core)的集成。高层次的抽象使得设计复杂性得以降低,并允许工程师在更高的层次上复用设计模块。

设计层次通常分为寄存器传输级(RTL)、门级、开关级等。RTL设计是最常被使用的抽象级别,它描述了数据在寄存器间的流动和处理逻辑。设计者在RTL层面上用硬件描述语言(HDL)编写代码,然后使用综合工具将RTL代码转换成门级网表,最终映射到实际的FPGA硬件资源上。

**表格示例**:

| 设计层次 | 描述 | 设计抽象 | 设计复杂性 |

|----------|------|-----------|-------------|

| RTL | 寄存器传输级 | 中级 | 中等 |

| 门级 | 基于逻辑门的描述 | 低级 | 较高 |

| 开关级 | 基于晶体管的描述 | 低级 | 较高 |

## 2.2 FPGA的数据传输机制

### 2.2.1 并行数据传输与串行数据传输

FPGA支持多种数据传输方式,其中最为常见的是并行数据传输和串行数据传输。

并行数据传输指的是同时在多个数据线上传输数据,这种方式在FPGA内部和芯片间的低速通信中非常有效。然而,随着数据传输速率的提升,由于信号线间干扰和时钟偏差问题,高速并行通信逐渐变得不可靠。

串行数据传输则是在单一数据线上顺序传输数据位,利用高速串行接口(如Aurora协议)可实现高速远距离数据通信。串行传输具有更低的电磁干扰,同时能有效减少线路数量,更适合高速和长距离数据传输。

### 2.2.2 数据同步与流量控制策略

为了确保数据的准确传输,FPGA设计中必须考虑数据同步和流量控制。数据同步指的是保证不同系统或模块间数据的时钟同步,常使用的协议如LVDS(Low Voltage Differential Signaling)。

流量控制则确保在数据通信过程中,发送方不会溢出接收方的缓冲区。常见的流量控制协议有FIFO(First-In-First-Out)缓冲区管理,以及更高级的协议如Aurora协议中的流控机制。

**mermaid流程图示例**:

```mermaid

graph LR

A[开始] --> B[初始化FIFO]

B --> C[写入数据到FIFO]

C --> D{FIFO满?}

D -- 否 --> E[发送数据]

D -- 是 --> F[等待直到FIFO非满]

E --> G{数据传输完成?}

F --> G

G -- 否 --> C

G -- 是 --> H[结束]

```

## 2.3 FPGA的电源管理和热设计

### 2.3.1 电源设计的基本原则

FPGA的电源设计需要考虑多个方面,首先必须确保供电电压满足FPGA核心电压的要求,并且能够提供足够的电流来驱动FPGA在最高性能模式下的工作。此外,电源设计还应考虑减少噪声和提供稳定的电源。通常情况下,FPGA供应商会提供电源设计指南,包含推荐的电源布线、去耦电容配置、以及电源管理模块的设计要求。

### 2.3.2 热管理的方法和实践

随着FPGA的集成度不断提高,热管理也变得尤为重要。热管理的目标是将FPGA产生的热量高效地传递到散热器上,并通过散热器将热量传递到周围环境中去。常用的方法包括使用散热片、风扇、热管和液冷系统。在设计初期就需要根据FPGA的功耗和预期的工作环境来选择合适的散热解决方案。

**代码块示例**:

```c

// 伪代码展示FPGA散热器选择算法

int selectCooler(int powerConsumption, float ambientTemp) {

if (powerConsumption < 100) {

return COOLER_TYPE_LITTLE;

} else if (powerConsumption < 500) {

return COOLER_TYPE_MEDIUM;

} else {

if (ambientTemp > 35) {

return COOLER_TYPE_HEAVY;

} else {

return COOLER_TYPE_AVERAGE;

}

}

}

```

以上章节内容为FPGA硬件基础知识的深入介绍,分别阐述了FPGA的基本概念、数据传输机制、电源管理和热设计。希望这些内容能够帮助读者更深入地理解FPGA的工作原理和设计考虑。在后续章节中,我们将继续探索Aurora协议在FPGA中的应用以及如何实现IP核集成和优化。

# 3. Aurora IP核集成与配置

## 3.1 Aurora IP核的介绍与选择

### 3.1.1 IP核的功能和性能特点

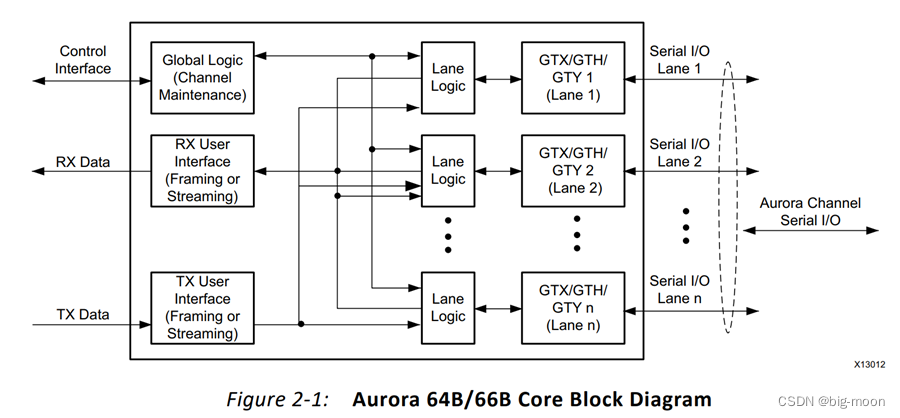

Aurora IP核是一种专用的串行通信协议,主要用于FPGA内部或FPGA与外部设备之间的高速数据传输。它基于差分信号进行通信,通过专用的协议引擎来保证数据的完整性与可靠性。与传统的并行通信相比,Aurora IP核在高速串行通信方面有着明显优势,如减少布线数量,提高通信速度,降低功耗等。

Aurora IP核支持高速数据链路的建立,能够满足高带宽和低延迟的数据传输需求。同时,它提供了一系列的配置选项,方便用户根据具体应用需求调整其性能参数,例如支持的速率、通道数量以及数据流控制策略等。该IP核还具备错误检测和纠正机制,能够提升系统在恶劣环境下的稳定性和可靠性。

### 3.1.2 根据需求选择合适的Aurora IP核

选择合适的Aurora IP核,首先要明确应用环境和性能需求。例如,对于需要极高带宽和低延迟的应用,可能需要选择支持更高速率的IP核版本。同时,应考虑FPGA设备的硬件资源,包括可用的专用IO资源和逻辑资源,以确保所选的IP核能够适配目标硬件平台。

其次,还需要考虑数据传输的特性和协议要求。不同的应用可能需要不同数量的数据通道,以及不同的流量控制策略。如果设计中需要支持特定的协议接口,也需要确保所选的Aurora IP核能够提供这样的支持。最后,电源管理、热设计等因素也需要在选择IP核时考虑,以确保最终的系统设计既高效又稳定。

## 3.2 Aurora IP核的实例化与配置

### 3.2.1 如何在FPGA项目中实例化Aurora IP核

实例化Aurora IP核的第一步是在FPGA的开发环境中创建一个新项目,并引入Aurora IP核的组件。在Xilinx的Vivado设计套件中,可以通过IP Catalog来查找并添加Aurora核。完成添加后,将自动生成IP核的实例化模板,包含了必要的端口和参数设置。

在项目中实例化Aurora IP核时,需要根据设计要求选择合适的协议版本和通道配置。通常情况下,设计者需要指定工作频率、通道数量、波特率、链路层数据宽度等参数。配置好这些参数后,可以使用综合工具生成相应的硬件描述语言代码(如Verilog或VHDL),将其集成到设计的顶层模块中。

### 3.2.2 配置参数详解与优化策略

Aurora IP核提供了丰富的配置参数,这些参数允许设计者对协议的各个方面进行精细调整。以下是一些常见的配置参数和它们的优化策略:

- **工作频率**:这是影响数据传输速率和系统性能的关键因素。根据FPGA设备和通信链路的能力选择合适的工作频率,可以确保最佳性能。

- **通道数量**:通常,更多的通道意味着更高的并行性和更高的带宽。但是,每增加一个通道,也需要考虑更多的硬件资源和设计复杂性。

- **波特率**:波特率决定了每个通道可以达到的数据传输速率。在保证信号质量的前提下,应尽量提高波特率以获取更高的带宽。

- **链路层数据宽度**:增加链路层的数据宽度可以提升数据吞吐量。但是,更大的数据宽度也需要更多的资源,可能会降低系统资源利用率。

对于每个参数的配置,设计者都需要根据具体的应用场景和硬件条件进行权衡。优化策略通常包括仿真验证、硬件测试和性能分析,通过不断迭代来找到最佳配置。

## 3.3 Aurora IP核的性能测试与验证

### 3.3.1 测试环境的搭建

为了验证Aurora IP核的性能,首先需要搭建一个测试环境。搭建测试环境包括准备所需的硬件设备和软件工具。硬件设备通常包括FPGA开发板、高速连接线缆和相关的接口设备。软件工具则包括FPGA设计和综合工具(例如Xilinx Vivado)以及协议分析工具。

测试环境的搭建步骤如下:

1. 配置FPGA开发板,确保其硬件资源满足Aurora IP核的需求。

2. 将设计好的FPGA项目烧录到开发板上,实现Aurora IP核的实例化。

3. 连接高速线缆,建立物理通信链路。

4. 使用协议分析工具监控和分析Aurora链路的状态和数据传输情况。

测试环境的搭建是性能验证的基础,需要保证所有的硬件和软件配置正确无误,以避免在性能测试过程中出现错误。

### 3.3.2 性能测试的指标和方法

性能测试的主要指标包括:

- **传输速率**:单位时间内成功传输的数据量,通常以Gbps表示。

- **错误率**:在传输过程中出错的数据包所占的比例。

- **延迟**:从数据发送到接收的平均时间间隔。

性能测试方法包括:

- **基准测试**:通过传输固定大小的数据包并记录时间来评估传输速率。

- **压力测试**:在高负载条件下测试系统的稳定性和错误率。

- **连续运行测试**:在长时间运行的情况下,检查系统的可靠性和持续工作能力。

测试时,应记录和分析每一项指标的数据,并与预期的性能值进行对比。这些性能数据不仅对于评估当前设计的性能至关重要,而且对于后续设计的优化提供了重要的依据。

### 3.3.3 常见问题的诊断与解决

在进行Aurora IP核的性能测试与验证过程中,可能会遇到各种问题。以下是一些常见问题的诊断与解决方法:

- **低传输速率**:可能的原因包括配置不当、硬件资源限制或者外部干扰。首先检查Aurora IP核的配置参数是否正确,例如波特率、通道数量等。如果配置无误,需要检查硬件是否满足速率要求,最后检查外部通信链路是否有干扰。

- **高错误率**:高错误率可能是由于信号完整性不良造成的。需要检查信号质量,包括时序约束和信号质量分析。如果问题依旧存在,可能需要调整信号的驱动强度或者使用更高质量的线缆。

- **延迟不稳定**:延迟不稳定通常与链路状态有关。检查链路建立是否正常,如果链路反复断开,可能需要优化链路恢复策略或者排查硬件问题。

解决这些问题时,应结合具体的测试数据和环境因素综合分析。在某些情况下,可能需要咨询IP核提供商的技术支持或者查找相关的技术文档进行更深入的诊断。

## 3.4 小结

通过本章节的介绍,我们了解了Aurora IP核在FPGA项目中的集成、配置、性能测试和验证的流程。首先,对Aurora IP核的功能和性能特点有了基本的认识,并掌握如何根据需求选择合适的IP核版本。接着,详细介绍了实例化Aurora IP核的步骤以及如何配置相关参数,强调了根据具体应用场景进行配置的重要性。然后,深入探讨了性能测试环境的搭建、性能测试指标和方法以及常见问题的诊断与解决。以上这些内容为后续章节中的软件接口开发、数据链路应用以及优化与调试奠定了基础。

# 4. Aurora协议的软件接口与应用

随着FPGA在数据通信领域内的应用不断增长,Aurora协议在构建高效可靠的数据链路中扮演了重要角色。在硬件层面上,我们已经了解了Aurora IP核的集成与配置。接下来,我们将深入探讨Aurora协议的软件接口及其应用。这一部分不仅是理论的延伸,也是将Aurora协议应用于实际项目中的关键步骤。

## 4.1 Aurora协议的软件驱动开发

软件驱动在Aurora协议的应用中是不可或缺的,它负责在操作系统和硬件之间架起沟通的桥梁。理解驱动的架构和关键开发技术对于优化通信性能、确保数据传输的可靠性至关重要。

### 4.1.1 软件驱动的作用和架构

驱动程序位于操作系统与硬件设备之间,为上层应用提供了统一的API接口,隐藏了硬件操作的细节。在Aurora协议中,软件驱动确保了用户空间应用程序能够通过标准化的接口与FPGA进行交互。驱动程序的架构通常包括以下几个层次:

- **硬件抽象层(HAL)**:负责管理硬件资源和执行硬件设备的基本操作。

- **中间件层**:提供协议处理、数据缓冲管理等服务。

- **应用接口层(API)**:为应用程序提供接口,完成具体的数据传输任务。

### 4.1.2 驱动开发的关键技术和工具

软件驱动开发涉及一系列的技术和工具。关键的技术包括:

- **中断处理**:用于处理硬件中断,及时响应Aurora协议中的各种事件。

- **内存管理**:涉及DMA(直接内存访问)操作,高效地管理数据在主机内存与FPGA间传输。

- **并发控制**:确保多线程或多进程环境下数据的一致性。

开发工具通常包括:

- **编程环境**:如GCC、Visual Studio等,用于编写和编译驱动代码。

- **调试器**:如GDB、WinDbg等,用于调试驱动程序。

- **性能分析工具**:如Intel VTune、MS PerfView等,用于评估驱动性能。

### 代码示例与分析

例如,下面的代码片段展示了Linux环境下Aurora协议驱动的一个简化初始化函数:

```c

static int aurora_driver_init(void) {

int ret;

/* 注册字符设备 */

ret = register_chrdev(MY_MAJOR, DEVICE_NAME, &fops);

if (ret < 0) {

printk(KERN_ALERT "Error registering device\n");

return ret;

}

/* 初始化硬件抽象层资源 */

hardware_init();

/* 初始化中断 */

ret = request_irq(IRQ_LINE, &irq_handler, IRQF_SHARED, DEVICE_NAME, NULL);

if (ret != 0) {

unregister_chrdev(MY_MAJOR, DEVICE_NAME);

printk(KERN_ALERT "Error requesting IRQ\n");

return ret;

}

/* 初始化数据缓冲区 */

buffer_init();

printk(KERN_INFO "Aurora driver initialized\n");

return 0;

}

```

在上述代码中,首先进行了字符设备的注册操作,之后初始化了硬件资源,包括中断。同时,代码中的每个步骤都附有相应的错误处理,确保驱动程序能够稳定运行。

## 4.2 Aurora协议的应用层开发

应用层开发是将Aurora协议的软件接口集成到用户应用程序中。这个过程中,开发者需要设计和实现应用层接口,同时负责数据链路层的封装和解封装。

### 4.2.1 应用层接口的设计与实现

应用层接口的设计需要考虑易用性和灵活性,以适应不同的使用场景。关键点包括:

- **API设计原则**:提供简洁、一致的接口给用户。

- **数据传输机制**:支持同步和异步的数据传输方式。

- **错误处理**:定义清晰的错误码和异常处理机制。

### 4.2.2 数据链路层的封装与解封装

数据链路层的封装和解封装是确保数据完整性和正确性的关键步骤。封装过程涉及到数据头的添加、错误检测码的计算等。解封装则负责检查数据的完整性,解析数据头,以及错误的纠正或报告。

### 代码示例与分析

下面是一个简化的数据封装函数示例:

```c

size_t aurora_package_data(uint8_t *buffer, size_t len, uint8_t *header) {

/* 将头部信息加入到数据包中 */

memcpy(buffer, header, HEADER_SIZE);

/* 将数据内容追加到头部信息后 */

memcpy(buffer + HEADER_SIZE, data, len);

/* 计算并添加校验码 */

uint32_t checksum = calculate_checksum(buffer, HEADER_SIZE + len);

memcpy(buffer + HEADER_SIZE + len, &checksum, sizeof(checksum));

return HEADER_SIZE + len + sizeof(checksum);

}

```

在上述代码中,我们首先将头部信息复制到缓冲区,然后将实际数据追加到头部之后,最后计算数据包的校验码,并添加到数据包的末尾。

## 4.3 Aurora协议的实际应用案例

Aurora协议广泛应用于高速数据传输领域,其中高性能计算和实时数据采集是最常见的应用场景。

### 4.3.1 高性能计算中的数据链路应用

在高性能计算(HPC)场景下,Aurora协议提供了高速、低延迟的点对点通信机制。典型的案例包括:

- **并行计算集群**:通过Aurora协议连接不同计算节点,实现高速的数据交换。

- **大数据处理**:在数据的聚合和分发过程中利用Aurora协议降低数据传输的时间开销。

### 4.3.2 实时数据采集系统的构建

实时数据采集系统对数据传输的实时性有极高的要求。应用案例包括:

- **工业自动化**:例如机器人控制、生产线监测等场景下,需要实时采集和传输传感器数据。

- **金融服务**:高频交易系统中,通过Aurora协议实现市场数据的实时传输。

### 表格展示案例对比

通过以下表格,我们可以对比在不同应用领域中Aurora协议的具体应用和性能要求:

| 应用领域 | 数据传输需求 | 性能要求 | 应用案例 |

|------------|-----------|-------------------|------------------------------|

| 高性能计算 | 高速、大规模 | 带宽、延迟、吞吐量 | 并行计算集群、大数据处理 |

| 实时数据采集系统 | 实时性、稳定性 | 实时响应时间、持续吞吐量 | 工业自动化、金融服务 |

通过表格可以看出,在高性能计算领域,关注点在于数据传输的高速度和大规模数据处理能力,而在实时数据采集系统中,更关注的是数据传输的实时性和系统稳定性。

### Mermaid流程图展示实时数据采集系统构建

接下来通过Mermaid流程图,我们展示实时数据采集系统构建中的关键步骤:

```mermaid

graph LR

A[开始构建系统] --> B[确定数据采集需求]

B --> C[选择合适的FPGA和Aurora IP核]

C --> D[集成Aurora IP核至FPGA]

D --> E[开发软件驱动]

E --> F[设计应用层接口]

F --> G[集成应用到系统中]

G --> H[测试与验证系统性能]

H --> I{是否满足性能要求?}

I -->|是| J[部署实时数据采集系统]

I -->|否| K[优化系统性能]

K --> J

```

在这个流程图中,首先确定数据采集的需求,然后选择合适的FPGA和Aurora IP核,接下来进行IP核的集成和软件驱动的开发,以及应用层接口的设计,最后进行测试和性能优化,确保系统满足实时数据采集的需求。

通过上述章节的介绍,我们已经对Aurora协议在软件层面的应用和开发有了深入的了解。这将为我们的开发工作提供坚实的基础,帮助我们构建出既高效又可靠的高速数据链路。

# 5. Aurora数据链路的优化与调试

## 5.1 信号完整性和串行通信的优化

### 5.1.1 信号完整性的基本概念

在高速串行通信中,信号完整性(SI)是确保数据准确无误传输的关键因素之一。信号完整性问题主要由信号反射、串扰、电源噪声和信号衰减等引起。为了保持数据链路的稳定性和可靠性,这些问题需要通过优化设计来解决。

### 5.1.2 高速信号的优化策略

优化高速信号通常涉及以下步骤:

- **阻抗匹配**:确保传输线与源和负载的阻抗相匹配,以减少信号反射。

- **布线优化**:使用差分对布线,尽量短而直,并且远离可能引起串扰的信号线。

- **去耦合电容**:在电源引脚附近使用去耦合电容来减少电源噪声。

通过这些策略可以显著提升信号质量,从而保障数据的正确传输。

## 5.2 Aurora数据链路的调试技巧

### 5.2.1 调试工具的选择与使用

调试Aurora数据链路时,选择正确的工具至关重要。常见的调试工具有逻辑分析仪、示波器、信号源以及专业的串行通信分析软件。例如,使用示波器可以观察信号波形,通过逻辑分析仪可以监测数据包的完整性和时序,而串行通信分析软件可以帮助解析协议层面的信息。

### 5.2.2 常见错误的排查与分析

调试过程中常见的错误包括但不限于:

- **时序问题**:时钟域不匹配或信号时序不正确。

- **配置错误**:Aurora IP核配置不当或参数设置错误。

- **信号质量问题**:信号幅度过低、过冲或振铃等。

排查这类问题首先需要采集信号,并在工具中进行详细分析。通常,需要在不同位置检测信号质量,并与预期波形进行比较。一旦发现异常,就需要追溯信号路径,检查设计和布局是否存在缺陷。

## 5.3 性能调优与故障排除

### 5.3.1 性能监控指标与调优方法

性能监控指标通常包括:

- **传输速率**:衡量数据传输的有效速度。

- **错误率**:数据在传输过程中的出错概率,如帧错误、校验错误等。

- **时延**:数据从发送到接收端的总延迟。

性能调优可以通过以下方法进行:

- **优化传输层协议**:例如调整TCP窗口大小,以适应数据链路的带宽。

- **改进数据包处理逻辑**:减少CPU在数据包处理上的负担,例如通过DMA(直接内存访问)机制。

- **调整硬件设计参数**:如提高时钟频率,或增加缓冲区大小。

### 5.3.2 故障诊断流程和排除步骤

故障诊断流程通常遵循以下步骤:

- **收集故障信息**:记录故障发生时的系统状态、操作步骤和错误消息。

- **定位故障源**:利用调试工具缩小问题范围,例如,通过对比正常和异常情况下的信号波形。

- **制定解决方案**:根据诊断结果,采取措施修复问题,这可能涉及修改代码、更改硬件设置或调整系统配置。

- **验证和测试**:实施解决方案后,需要重新测试以确保问题已被彻底解决。

故障排除是整个开发和维护过程中不可缺少的一部分,对提升数据链路的稳定性和效率至关重要。

0

0