计算机组成原理:彻底分析指令集架构与CPU设计优化

发布时间: 2024-12-14 06:40:11 阅读量: 1 订阅数: 3

计算机组成原理:学习指导与习题解答

参考资源链接:[计算机组成原理课后习题及答案-唐朔飞(完整版).ppt](https://wenku.csdn.net/doc/645f3404543f8444888ac128?spm=1055.2635.3001.10343)

# 1. 指令集架构的基础理论

## 1.1 指令集架构的定义与作用

指令集架构(Instruction Set Architecture,简称ISA)是计算机硬件与软件之间的一个重要界面,它定义了处理器硬件能够识别和执行的一套机器语言指令。ISA作为一层抽象,屏蔽了底层硬件的复杂性,为上层软件提供了一套清晰、简洁的编程模型。它既包括了数据类型、寄存器、寻址模式等低级概念,也涵盖了异常处理、内存管理等高级特性。

## 1.2 常见的指令集架构类型

市场上存在多种指令集架构,其中最著名的有复杂指令集计算(Complex Instruction Set Computing,CISC)和精简指令集计算(Reduced Instruction Set Computing,RISC)。CISC架构以x86架构为代表,强调使用少量的复杂指令来实现多种功能;RISC架构则以ARM和MIPS为代表,主张通过大量的简单指令来提高执行效率。这些指令集架构的差异直接影响了处理器的设计和性能优化策略。

## 1.3 指令集架构的重要性

指令集架构对于整个计算机系统的设计和应用具有深远的影响。它不仅决定了处理器的性能、功耗和热效率,还与编程语言、操作系统和编译器等软件系统的开发紧密相关。因此,在CPU设计和软件优化过程中,对指令集架构的理解和运用都是至关重要的。正确选择或设计指令集架构,可以有效提升系统的整体性能,并促进软硬件的协同优化。

# 2. 深入理解CPU的工作原理

## 2.1 CPU的基本组成和功能

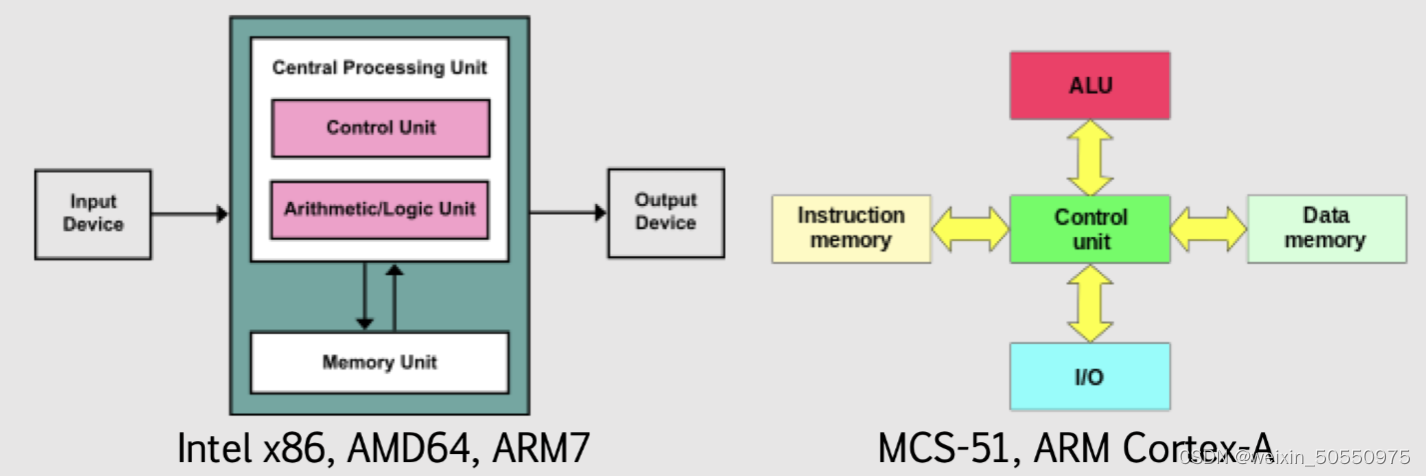

### 2.1.1 CPU内部结构详解

CPU是计算机的核心部件,其内部结构设计决定了计算机的处理能力。CPU主要由运算器、控制器、寄存器组和高速缓存(Cache)组成。

- **运算器**:负责执行所有的运算任务,如算术运算和逻辑运算。

- **控制器**:从内存中取出指令,解释指令并发出相应的控制信号。

- **寄存器组**:暂存指令、数据和地址等信息,是CPU中速度最快的存储部件。

- **高速缓存(Cache)**:用于缓解CPU与主内存之间速度不匹配的问题,存储临时数据和指令以提高访问速度。

除了上述基本组成,现代CPU还包含了其他复杂组件,如指令预取单元、乱序执行引擎等。

### 2.1.2 CPU的指令执行周期

CPU执行程序的过程,实际上是执行一系列指令的过程。每个指令的执行分为几个阶段,通常包括取指(Fetch)、译码(Decode)、执行(Execute)、访存(Memory Access)和写回(Write Back)。

- **取指(Fetch)**:从程序计数器(PC)指向的地址读取指令,存入指令寄存器。

- **译码(Decode)**:对指令进行解码,确定指令类型及操作数。

- **执行(Execute)**:算术逻辑单元(ALU)执行指令所定义的操作。

- **访存(Memory Access)**:访问主内存或高速缓存来读写数据。

- **写回(Write Back)**:将执行结果写回寄存器。

整个周期不断循环,形成程序的执行流程。下面是一个简化的流程图展示这一周期过程:

```mermaid

graph LR

A[取指 Fetch] --> B[译码 Decode]

B --> C[执行 Execute]

C --> D[访存 Memory Access]

D --> E[写回 Write Back]

E --> A

```

## 2.2 CPU的指令处理机制

### 2.2.1 指令的解码过程

指令解码是CPU将机器码转换为可执行操作的过程。这个过程通常涉及到以下几个步骤:

1. **获取指令**:从指令寄存器中读取机器码。

2. **分析指令**:根据指令的格式,识别操作码(Opcode)和操作数。

3. **生成控制信号**:根据操作码,生成控制ALU和其他部件的信号。

### 2.2.2 指令的执行和控制

指令的执行取决于其类型,例如算术指令需要ALU参与运算,而控制指令如跳转和分支则需要改变程序计数器的值。执行过程通常涉及到多个控制单元和逻辑门电路的协作。

### 2.2.3 流水线技术及其优化

流水线技术是现代CPU提高指令执行效率的重要手段。它将指令执行周期拆分成若干个子过程,多个指令可以同时在流水线的不同阶段进行处理,有效提高了CPU的吞吐量。

在流水线设计中,数据冲突、控制冲突和结构冲突是常见的问题。优化流水线,需要考虑平衡各阶段的负载、减少冲突和提高指令并行度等因素。一个简化的流水线模型可以用以下表格表示:

| 时间单元 | 取指 | 译码 | 执行 | 访存 | 写回 |

| -------- | ---- | ---- | ---- | ---- | ---- |

| T1 | I1 | | | | |

| T2 | I2 | I1 | | | |

| T3 | I3 | I2 | I1 | | |

| ... | ... | ... | ... | ... | |

| Tn | In | In-1 | In-2 | In-3 | In-4 |

## 2.3 CPU的性能分析

### 2.3.1 性能评估标准

CPU的性能评估通常使用以下标准:

- **时钟频率**:CPU每秒执行多少次周期。

- **IPC(Instructions Per Cycle)**:每个时钟周期内执行的平均指令数。

- **CPI(Cycles Per Instruction)**:执行每条指令所需的平均周期数。

### 2.3.2 性能提升的策略与方法

提升CPU性能的策略包括提高时钟频率、改进微架构设计、引入多线程和多核心技术等。此外,硬件预取技术和编译器优化技术也常用于提高CPU性能。下面是一个代码块,展示了一个简单指令的执行过程:

```assembly

mov eax, [mem] ; 将内存地址mem处的数据加载到eax寄存器

add eax, 1 ; 将eax寄存器的值加1

```

在这个简单的例子中,首先将内存中的数据加载到寄存器,然后执行加法操作。这个过程涉及到取指、译码、执行和写回阶段。每个指令的执行都依赖于CPU的内部结构,包括运算器、控制器和寄存器组。

# 3. 指令集架构的设计与优化

## 3.1 指令集的分类与特点

### 3.1.1 CISC架构的原理与应用

复杂指令集计算(CISC)架构代表了一类在早期计算机设计中普遍采用的指令集架构(ISA)。CISC的设计理念是将尽可能多的功能封装在单一指令中,以减少程序执行所需的指令数量。这种方法的目的是通过硬件直接支持高级编程语言的功能来简化编译器设计。

CISC架构中的一些典型指令集包括Intel的x86架构和VAX架构。x86架构广泛应用于个人电脑、服务器和嵌入式系统中,其特点是可处理的指令数量多、格式灵活,涵盖了从简单算术运算到复杂数据处理的广泛指令。

然而,CISC架构也面临一些挑战。随着集成电路技术的发展,指令宽度和寻址模式的多样性和复杂性在某些情况下会导致硬件设计复杂,从而影响指令的执行效率。现代CISC处理器通常采用微程序技术来解决这个问题,通过软件模拟来实现复杂指令,使得硬件层面的实现变得更加简单。

在应用方面,x86架构的指令集因其广泛的软件兼容性而在个人电脑和服务器市场占据主导地位。同时,随着技术的进步,现代x86处理器如Intel的Haswell架构也引入了大量RISC风格的微操作,展现了CISC与RISC设计理念的融合。

### 3.1.2 RISC架构的优势与挑战

精简指令集计算(RISC)架构与CISC架构形成鲜明对比,其核心思想是简化指令集,使每条指令都能在一个处理器周期内完成。RISC架构的指令通常都是固定长度,且执行速度快,因为它们对硬件的需求较少。RISC架构的代表包括ARM、MIPS和RISC-V。

RISC架构的优势在于它简化的指令集减少了控制逻辑的复杂度,从而提高了指令执行的频率,并允许处理器在更短的周期内执行指令。此外,由于指令集较为简单,RISC处理器可以利用管道技术来提升性能,而RISC处理器通常具有更简单的流水线设计,能够更有效地提高指令的吞吐量。

尽管RISC架构在设计上具有诸多优势,但也面临挑战。一个主要挑战是编译器必须能够高效地将高级语言转换为简化的RISC指令集,而复杂的操作可能需要多条RISC指令来实现。因此,优秀的编译器技术和优化算法对于RISC架构的成功至关重要。

在实际应用中,ARM架构因其实现了出色的性能与能效比,在移动设备和嵌入式系统市场取得了巨大成功。ARM的设计理念和架构的优化使得它在智能手机和平板电脑等便携式设备中成为主流。RISC架构也在高性能计算领域找到了应用场景,特别是在需要大量并行处理和低功耗要求的环境中。

## 3.2 指令集的扩展与兼容性

### 3.2.1 向量和SIMD指令的扩展

随着科学计算和多媒体处理对高性能的需求日益增长,向量处理成为提高计算效率的重要手段。向量和单指令多数据(SIMD)指令集扩展是对指令集架构的重要补充,允许单条指令同时操作多个数据点。

SIMD扩展技

0

0