【编程Cortex-M3_M4】:新手到专家的逐步教程

发布时间: 2025-01-05 02:43:34 阅读量: 33 订阅数: 16

cortex-M3、Cortex-M4权威指南 英文原版

# 摘要

本文首先介绍了Cortex-M3/M4微控制器的基础知识和硬件架构。详细阐述了Cortex-M3/M4的核心特征,包括处理器核心、指令集、内存保护单元和异常处理机制,并探讨了系统级接口以及外设、中断控制器和电源管理组件的作用。进一步,本文深入讲解了Cortex-M3/M4编程基础,如基础指令集、汇编语言编程、Thumb-2技术和混合编程技巧,并介绍了开发环境和工具链的使用。在Cortex-M3/M4应用开发实践中,研究了中断处理、外设控制、驱动编写和系统性能优化。最后,探讨了高级应用编程技巧,算法实现,并分析了典型应用项目案例,展示了如何将理论知识应用于实际开发中。

# 关键字

Cortex-M3/M4;硬件架构;编程基础;应用开发;系统性能优化;高级应用项目

参考资源链接:[Cortex M3与M4权威指南(第三版):深入理解ARM处理器](https://wenku.csdn.net/doc/3zdsfhe1rg?spm=1055.2635.3001.10343)

# 1. Cortex-M3/M4微控制器简介

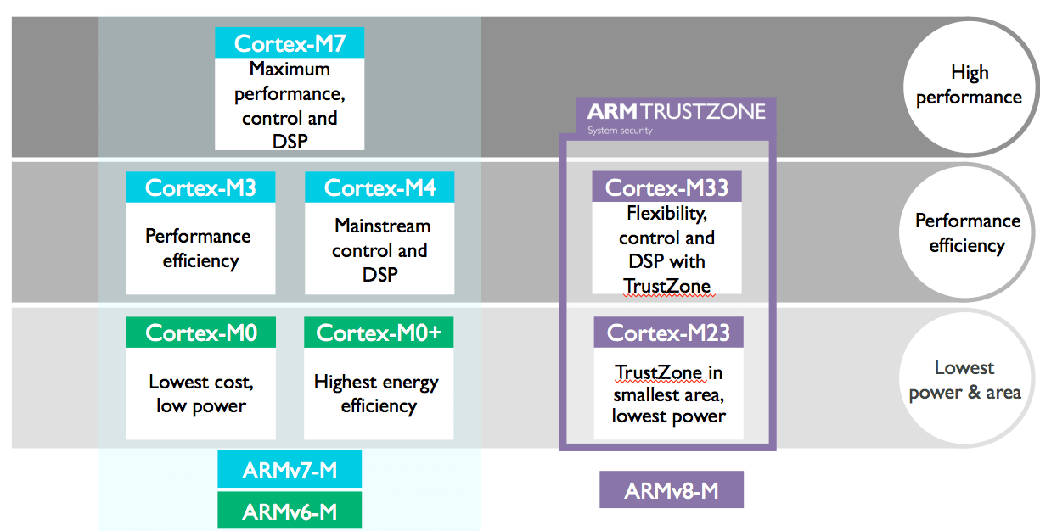

随着物联网和智能设备的发展,Cortex-M3/M4微控制器以其高效能和实时性能,成为了嵌入式开发领域的热门选择。ARM公司设计的Cortex-M3/M4系列,提供了在成本效益和性能之间的理想平衡,尤其适合于需要高性能处理能力的中高端应用。

Cortex-M3和M4在内部架构上大体相似,但M4加入了数字信号处理(DSP)指令集和浮点单元(FPU),使得其在音频处理、控制算法等要求更复杂数据处理的应用中更具优势。两款微控制器都提供了高效的中断响应能力,适合需要快速处理外部事件的场合。

对于开发者而言,理解Cortex-M3/M4的架构和编程特点,可以更好地利用其资源,进行高效的应用开发。接下来的章节将深入探讨Cortex-M3/M4的硬件架构、编程基础、应用开发实践以及高级应用案例,为希望深入这一领域的专业人士提供详细的参考指南。

# 2. Cortex-M3/M4的硬件架构

## 2.1 Cortex-M3/M4核心特征

### 2.1.1 处理器核心和指令集

Cortex-M3和Cortex-M4是ARM推出的针对微控制器市场的一系列高性能处理器核心。这些核心被设计为具有高度的能效比,适合于广泛的嵌入式应用,从简单的传感器到复杂的控制系统。Cortex-M3的核心主要基于ARMv7-M架构,而Cortex-M4则在Cortex-M3的基础上增加了浮点运算单元(FPU),支持单精度浮点运算。

在指令集方面,Cortex-M3和Cortex-M4都采用了ARM的Thumb指令集,特别是为微控制器优化的Thumb-2技术。这种指令集的优势在于它结合了32位和16位指令的优点,能在保持32位指令计算能力的同时,以更小的代码大小提升执行效率。例如,简单的算术操作通常只需要一个16位指令,而条件执行可以不带分支地完成,极大地减少了指令数目和提高性能。

### 2.1.2 内存保护单元和异常处理

Cortex-M3/M4的内存保护单元(MPU)是一个可选的硬件组件,它能够提供内存访问控制的功能,使得开发者能够为不同的内存区域设置访问权限,以及划分内存保护区域,以防止软件错误影响到整个系统的稳定性和安全性。MPU通过允许系统在发生访问违规时触发异常处理,从而提供了软件故障隔离的能力。

异常处理方面,Cortex-M3/M4拥有一个高度灵活的异常模型,允许系统根据需要配置不同的异常优先级和响应机制。这允许实时操作系统(RTOS)和应用软件在发生异常时能高效且可靠地进行上下文切换。异常可以来自中断、系统错误或软件触发的操作,它们都通过一个统一的异常处理框架来管理。

## 2.2 系统级接口和组件

### 2.2.1 外设和内存映射

Cortex-M3/M4微控制器通常包含大量的外围设备,这些设备通过内存映射接口与处理器核心相连。这种设计允许外设访问和处理器的主内存区域一样被访问。每种外设寄存器都有一个固定的地址,通过简单的加载和存储指令即可完成对寄存器的访问,这样大大简化了外设控制的编程模型。

在内存映射设计中,外设被组织在一系列的内存空间内。比如,系统控制空间(System Control Space, SCS)包括了如系统定时器、电源控制等与系统运行至关重要的组件,而通用外设空间则包含了如GPIO、UART等通用外设的寄存器。这样的设计有助于提高系统的可扩展性,因为不同的微控制器可以根据需要引入更多或更少的外设,而应用程序无需修改即可继续工作。

### 2.2.2 中断控制器和电源管理

中断系统是微控制器设计中不可或缺的一部分,它允许外设在需要处理器介入处理时能够中断处理器当前的执行流程。Cortex-M3/M4拥有一个高度优化的中断控制器,可以处理多达240个中断源(包括外设中断和系统异常),并且支持中断优先级的灵活配置。

在电源管理方面,Cortex-M3/M4提供了多种低功耗模式,以支持电池供电的便携式应用或能源敏感的应用。这些模式允许处理器在尽可能低的功耗下工作,甚至可以完全关闭处理器核心,只保持内存和一些关键外设的运行。状态保存和恢复机制使得微控制器可以从睡眠模式快速唤醒,且不会丢失重要的系统状态,这对于实时系统尤其重要。

```mermaid

flowchart LR

A[处理器核心] -->|执行指令| B[指令集架构]

B -->|基于| C[Thumb-2技术]

C -->|优化| D[16位和32位指令]

D -->|支持| E[内存保护单元(MPU)]

E -->|配置| F[内存访问权限]

F -->|触发| G[异常处理机制]

G -->|处理| H[中断系统]

H -->|配置| I[中断优先级]

I -->|响应| J[电源管理]

J -->|低功耗| K[多种模式]

```

由于文章需要的是二级章节的内容,以下是部分二级章节的代码块和逻辑分析的示例:

```assembly

; 示例汇编指令集代码

LDR R0, =0x40000000 ; 加载外设地址到寄存器R0

MOV R1, #0x01 ; 将数据0x01加载到寄存器R1

STR R1, [R0] ; 将R1的值存储到R0指向的地址

; 以上代码的作用是配置特定的外设寄存器

```

在上述代码中,首先通过LDR指令将外设的地址加载到寄存器R0中。然后,MOV指令将数值0x01加载到寄存器R1中,这个数值通常代表寄存器的某个初始值或配置位。最后,STR指令将R1中的值存储到R0指向的外设地址中,实现对外设寄存器的配置。这个过程是微控制器编程中常见的操作,用于初始化和配置外设。

以上内容展示了Cortex-M3/M4处理器的硬件架构核心特征部分,包括处理器核心、内存保护单元、系统级接口及组件的要点。接下来的章节将深入到编程基础,为应用开发实践打下坚实的基础。

# 3. Cortex-M3/M4编程基础

## 3.1 基础指令集和汇编语言编程

### 3.1.1 指令集架构概述

Cortex-M3/M4微控制器使用的ARM Cortex-M系列指令集是专为微控制器设计的简化指令集。它保留了ARM指令集的32位长度,并支持Thumb-2技术,这是一种指令集的扩展,旨在提高代码密度和性能。指令集的设计注重于高效执行,以及对中断的快速响应,非常适合实时应用。

ARM Cortex-M系列指令集主要包括以下几种类型:

- 数据处理指令:用于算术和逻辑运算。

- 载入和存储指令:用于内存访问。

- 分支指令:用于程序流程控制。

- 异常产生和处理指令:用于系统异常和中断管理。

- 特殊指令:包括协处理器访问、系统控制和同步等。

### 3.1.2 汇编语言的基本语法和指令应用

汇编语言编程是微控制器领域的一个基础技能,Cortex-M3/M4的汇编语言也不例外。ARM汇编指令通常包含以下部分:

- 操作码(opcode):指示要执行的操作。

- 操作数:指定操作的参数。

- 条件码:可选,指定指令的执行条件。

以下是一个ARM汇编语言的基本示例,实现了一个简单的加法操作:

```assembly

AREA Reset, DATA, READONLY

EXPORT __main

ENTRY

__main

LDR R0, =0x1234 ; 将地址0x1234加载到寄存器R0

LDR R1, =0x5678 ; 将地址0x5678加载到寄存器R1

ADD R2, R0, R1 ; 将R0和R1的值相加,结果存储在R2

B .

END

```

- `AREA`声明了一个程序区域。

- `EXPORT`和`ENTRY`是汇编程序的入口点。

- `LDR`指令用于从内存中加载数据到寄存器。

- `ADD`指令执行加法操作。

在编写汇编程序时,需要考虑寄存器使用、内存对齐、栈操作等低级细节。此外,合理的注释能

0

0