【GC4663高速电路挑战应对】:信号完整性与电源管理的专家建议

发布时间: 2025-01-04 21:39:36 阅读量: 12 订阅数: 12

# 摘要

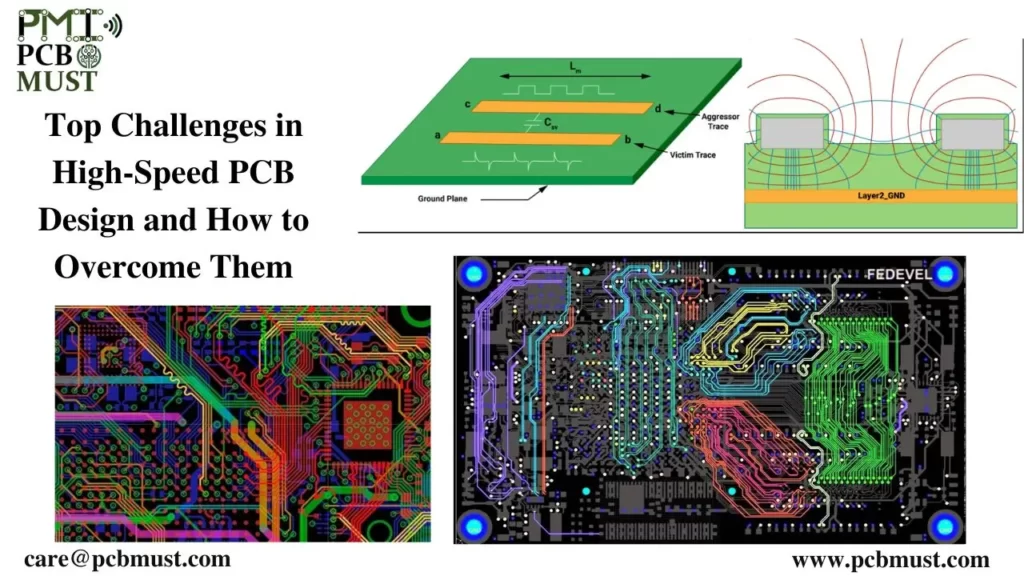

信号完整性和电源管理是高速电路设计中至关重要的两大要素。本文首先介绍了信号完整性及其在高速电路设计中的重要性,随后详细探讨了信号完整性面临的核心问题,分析方法,以及解决策略。接着,文章转而讨论电源管理的基础知识,高效设计策略以及通过实际案例展示电源完整性优化。第四章提出了高级分析工具和方法,对信号和电源完整性的仿真和分析环境进行了深入探讨。最后,展望了未来信号完整性与电源管理的发展趋势,包括下一代高速接口标准的探索和电源管理创新技术,同时提出综合性挑战的应对策略,旨在为工程实践和未来研究方向提供指导。

# 关键字

信号完整性;电源管理;高速电路设计;电磁仿真;电源网络分析;信号与电源协同设计

参考资源链接:[GC4663 CSP: 1/3'' 4Mega CMOS Image Sensor Datasheet](https://wenku.csdn.net/doc/4r6b0eemud?spm=1055.2635.3001.10343)

# 1. 信号完整性的基本概念与重要性

## 1.1 信号完整性的定义

在高速电路设计中,信号完整性(Signal Integrity, SI)是指在电子系统中,信号在传输过程中保持其原始特性的能力,即信号在发送和接收之间没有发生形态、时间或振幅上的不期望变化。理想的信号应当在到达目的地时仍然保持其原有的逻辑状态,但在实际的电路设计中,由于众多物理效应的影响,信号完整性往往会受到破坏。

## 1.2 信号完整性的重要性

信号完整性对系统性能有直接影响。在高速数字电路中,差的信号完整性可能会导致数据传输错误,增加比特误码率(BER),降低系统的可靠性。例如,在高速通信系统中,信号完整性问题可能会引起时钟抖动和数据抖动,进而影响同步和数据完整性。在模拟电路中,信号完整性问题可能会导致信号失真,影响到整体系统的精确度和效率。

## 1.3 信号完整性与系统性能的关系

良好的信号完整性是确保电路系统在规定的性能指标内稳定工作的基础。系统性能的优劣往往直接取决于信号在电路板(PCB)上的传输质量。在设计时,工程师需要通过信号完整性分析预测并解决可能的信号退化问题,以确保系统具备足够的稳定性和可靠性。

总结来说,信号完整性是高速电路设计中不可或缺的一环,从设计到最终产品测试,贯穿整个电子产品的生命周期。下一章,我们将深入探讨高速电路设计中的信号完整性理论,包括其核心问题以及分析方法。

# 2. 高速电路设计中的信号完整性理论

在高速电路设计中,信号完整性是一个不可忽视的重要问题。随着数据速率的增加,信号完整性问题对电路性能的影响也越来越大。本章节将深入探讨高速电路设计中的信号完整性理论,涵盖信号完整性核心问题的分析、分析方法的探讨,以及解决信号完整性问题的策略。

## 2.1 信号完整性的核心问题

在高速电路设计领域,信号完整性问题主要包括信号反射、串扰与耦合以及电源与地平面噪声。这些问题的存在严重影响了信号的传输质量,并可能导致电路性能下降。

### 2.1.1 信号反射

信号在传输过程中,由于阻抗不匹配,会在发送端和接收端产生反射。这种反射会导致信号波形失真,进而影响电路的功能。解决信号反射问题的关键在于阻抗匹配,即确保信号的源阻抗、传输线的特性阻抗以及负载阻抗之间的一致性。

### 2.1.2 串扰与耦合

在高速电路中,信号线之间的电磁场相互影响,产生串扰。串扰会导致信号之间产生不必要的干扰,从而影响信号的清晰度。为了避免和减轻串扰,可以采取隔离敏感信号线、增加信号线间距以及使用差分信号传输等措施。

### 2.1.3 电源与地平面噪声

电源和地平面的噪声也是影响信号完整性的一个重要因素。由于高速电路中的快速电流变化,电源和地平面可能会产生噪声,影响电路的稳定性和可靠性。为了减少噪声,设计中应当采用去耦电容、使用电源平面以及电源管理芯片等方法。

## 2.2 信号完整性分析方法

信号完整性的分析是设计过程中的重要环节,主要分析方法包括时域与频域分析、电磁仿真工具的应用以及实验测试与验证。

### 2.2.1 时域与频域分析

时域分析能够直观地展示信号在时间轴上的变化,而频域分析则有助于理解信号在频域的分布和噪声特性。在设计时,使用时域和频域的分析工具可以帮助设计人员对信号完整性问题进行深入理解。

### 2.2.2 电磁仿真工具的应用

电磁仿真工具是分析信号完整性的强大辅助手段。通过电磁仿真,可以在设计阶段预测信号传输特性和可能的干扰情况,从而进行优化设计。

### 2.2.3 实验测试与验证

除了理论分析和仿真工具,实验测试与验证同样是不可或缺的步骤。通过实际搭建电路并进行测试,可以验证理论分析和仿真的准确性,并针对实际问题进行调整。

## 2.3 解决信号完整性问题的策略

为了在高速电路设计中确保信号完整性,可以采取多种策略,包括路线规划与布局优化、终端匹配与缓冲技术以及高速接口协议考虑。

### 2.3.1 路线规划与布局优化

良好的路线规划与布局优化能够有效减少信号间干扰和噪声。设计者应当合理规划信号路径,避免过长的线迹,以及考虑信号返回路径的连续性。

### 2.3.2 终端匹配与缓冲技术

终端匹配技术能够减少信号反射,提高信号传输质量。常见的终端匹配技术包括串联终端匹配和并联终端匹配。此外,使用适当的缓冲器也能在一定程度上改善信号完整性。

### 2.3.3 高速接口协议考虑

高速接口协议中通常包含了对信号完整性的优化措施。设计者在选择和设计高速接口时,需要考虑协议中规定的信号完整性要求,并进行适当的硬件设计。

```mermaid

graph TD

A[信号完整性核心问题] -->|1| B[信号反射]

A -->|2| C[串扰与耦合]

A -->|3| D[电源与地平面噪声]

B --> E[阻抗匹配]

C --> F[隔离与间距]

D --> G[去耦电容与电源平面]

H[信号完整性分析方法] -->|1| I[时域与频域分析]

H -->|2| J[电磁仿真工具]

H -->|3| K[实验测试与验证]

I --> L[信号时间与频谱分析]

J --> M[电磁场模拟]

K --> N[实际电路验证]

O[解决信号完整性问题的策略] -->|1| P[路线规划与布局优化]

O -->|2| Q[终端匹配与缓冲技术]

O -->|3| R[高速接口协议]

P --> S[路径规划与布局调整]

Q --> T[终端匹配与缓冲器应用]

R --> U[接口协议中完整性措施]

```

通过上述内容,我们已经对高速电路设计中的信号完整性理论有了全面而深入的了解。在接下来的章节中,我们将进一步探讨电源管理在高速电路设计中的实践应用。

# 3. 电源管理在高速电路设计中的实践

## 3.1 电源完整性的基础知识

电源完整性是高速电路设计中不可或缺的一部分。良好的电源完整性意味着电路能够在所有工作条件下提供稳定和干净的电源,这对于确保信号的正确传输至关重要。

### 3.1.1 电源噪声和去耦策略

电源噪声是高速电路中的一个常见问题,它可以由多种因素引起,包括但不限于开关电源的快速变化、高速电路中的

0

0