VITA57.1接口卡信号完整性分析:保持信号质量的秘诀

发布时间: 2024-12-29 13:20:37 阅读量: 25 订阅数: 18

# 摘要

VITA57.1接口卡作为高速数据传输领域的重要组件,其信号完整性至关重要。本文首先概述了VITA57.1接口卡的基本原理和结构,随后深入探讨了信号完整性理论,包括信号完整性的重要性、影响因素、基本概念以及设计原则。在实践中,文章详细介绍了接口卡硬件设计的注意事项、信号测试方法以及实际问题的诊断和解决策略。通过仿真分析,本文强调了仿真工具在预测和优化信号完整性中的应用价值,并且展示了优化技术策略和高级优化技巧。最后,本文展望了VITA57.1接口卡及其信号完整性管理的未来发展趋势,包括新材料、新技术的应用以及智能化设计的重要性。

# 关键字

VITA57.1接口卡;信号完整性;硬件设计;仿真分析;优化策略;未来趋势

参考资源链接:[VITA57.1 FPGA接口卡修订解析:时钟信号与应用定制](https://wenku.csdn.net/doc/6469c2b0543f844488c1d0d2?spm=1055.2635.3001.10343)

# 1. VITA57.1接口卡概述

VITA57.1接口卡作为FPGA领域的一种标准,它为用户提供了一个灵活的平台来扩展各种自定义功能。这种接口卡通常被设计用于高速数字信号处理和数据传输,使其在需要高性能计算的场合中备受青睐。本章将深入探讨VITA57.1接口卡的基础知识,包括它的标准规范、应用场景以及其设计中的核心挑战,为接下来深入信号完整性打下基础。

我们首先从VITA57.1标准的起源和发展谈起,来了解其背后的设计理念和技术规范。然后,将讨论这种接口卡在现代电子系统中的典型应用,以及它为工程师带来的优势。通过本章的学习,读者将获得一个全面的视角,认识并理解VITA57.1接口卡在现代电子工程中的重要性。

# 2. 信号完整性基本理论

## 2.1 信号完整性的重要性

### 2.1.1 信号完整性问题概述

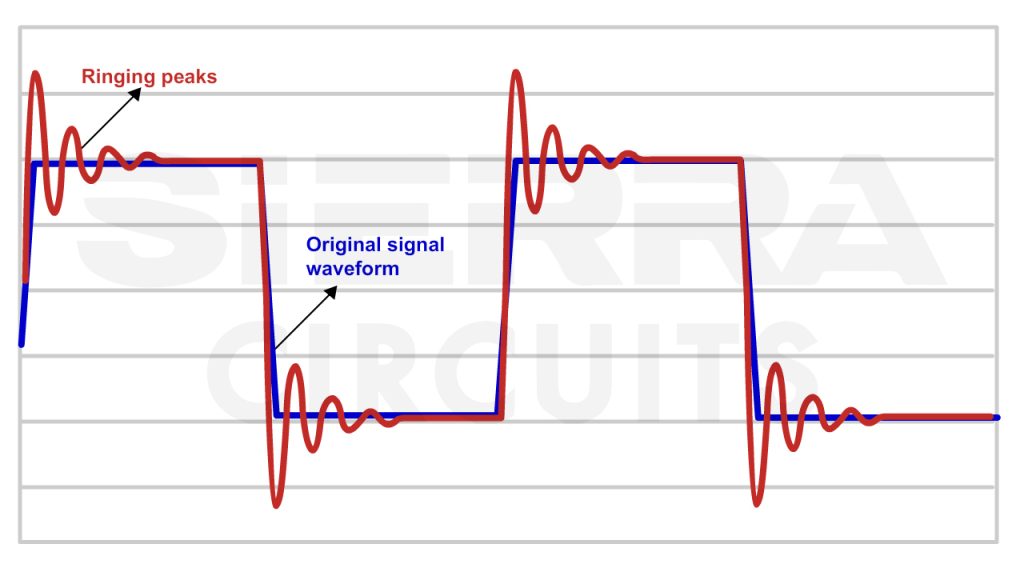

信号完整性(Signal Integrity, SI)是指在高速数字电路中,数字信号能够保持其形状和时间特性,不至于受到系统中各种干扰和失真的影响,从而正确地进行信息传递的能力。随着集成电路的频率越来越高,数据传输速率也随之增加,信号完整性问题便成为了设计高性能电子系统时不可忽视的问题。

### 2.1.2 影响信号完整性的因素

信号完整性问题通常由多种因素共同引起,主要包括反射(Reflection)、串扰(Crosstalk)、电磁干扰(Electromagnetic Interference, EMI)、电源噪声(Power Noise)、地弹(Ground Bounce)等。这些因素会在不同的物理层面上对信号质量产生影响。

## 2.2 信号完整性基础

### 2.2.1 反射、串扰和电磁干扰

**反射**是由于传输线的特性阻抗与源阻抗或负载阻抗不匹配时,导致部分信号波形在传输线上反弹的现象。理想情况下,源阻抗与传输线阻抗匹配,信号可以完全传输,而无反射。

**串扰**则发生在信号在传输时,由于电磁耦合相邻的信号线之间互相干扰。这种干扰会导致信号失真,进而影响信号完整性。

**电磁干扰**通常由外部电磁场源或者高速电路本身产生的电磁辐射造成,它会影响信号的质量,并可能对其他电路造成干扰。

### 2.2.2 传输线理论基础

传输线理论是信号完整性分析的基础,它描述了信号如何在电路板上的传输线上传播。关键概念包括传输线的特性阻抗、传播速度、信号上升时间以及传输线的时延等。

**特性阻抗(Z0)**是传输线上的一个固有属性,它由导线的几何尺寸、介电常数等物理参数决定。特性阻抗的不连续性会导致信号反射。

信号在传输线上的传播速度(v)与介电常数(εr)有关,一般为光速的一定比例,用公式表示为 v = c / √εr。其中 c 是光速,εr 是材料的相对介电常数。

**上升时间(Tr)**是指信号从10%的电平上升到90%的电平所需的时间,它是衡量信号变化快慢的一个参数。

**传输线时延(Td)**表示信号在传输线上从起点到终点的传播时间。传输线时延与传输线的长度和信号传播速度有关。

## 2.3 信号完整性设计原则

### 2.3.1 阻抗控制

为了确保信号的完整性,设计者需要控制传输线的特性阻抗。阻抗控制的原则包括:

- 保持传输线的特性阻抗在整个长度上恒定。

- 避免由于印制电路板(PCB)布局设计不当引起的阻抗不连续。

- 对于高速信号线,尽量使用差分信号线,以减少干扰。

### 2.3.2 终端匹配策略

终端匹配是指在信号的发送端或接收端采取措施,以消除或减少反射。常见的匹配策略包括:

- **源端匹配**:在信号源端通过并联电阻到电源或地来匹配阻抗。

- **负载端匹配**:在信号负载端通过并联电阻到电源或地来匹配阻抗。

- **戴维宁匹配**:通过一个等效电压源和一个电阻并联来匹配负载,以达到终端匹配。

在实际设计中,终端匹配方法的选择取决于特定的设计要求、成本和性能考虑。对于复杂的高速电路设计,可能需要采用多种匹配技术以达到最佳的信号完整性效果。

以上章节内容简要介绍了信号完整性的重要性、基础理论以及设计原则。在第三章中,我们将通过具体的案例来探讨VITA57.1接口卡的信号完整性实践,包括硬件设计、信号测试以及问题解决策略。

# 3. VITA57.1接口卡信号完整性实践

## 3.1 接口卡硬件设计

### 3.1.1 PCB布线技巧

印刷电路板(PCB)布线是硬件设计中至关重要的一步,良好的布线能够显著提高信号的完整性,减少噪声和电磁干扰。在设计VITA57.1接口卡时,以下几个PCB布线技巧需要特别关注:

1. **阻抗控制**:保证走线的阻抗与源端和负载端匹配,通常在高速信号设计中,阻抗需要控制在50欧姆左右。使用微带线或者带状线设计时,需要注意导线的宽度、介质的厚度和介电常数。

2. **减少回流路径**:高速信号的回流路径应当尽可能短且直接,避免尖锐的拐角和不必要的环路,以减少辐射和串扰的可能性。

3. **分割地平面**:在多层PCB设计中,合理地分割数字地和模拟地,可以防止数字部分对模拟部分产生干扰,降低系统的噪声水平。

4. **控制走线长度**:信号传输线长度应当尽可能短,特别是对于高速差分信号而言,过长的走线会导致信号质量和时序问题。

5. **避免高速信号并行走线**:高速信号线如果平行摆放过长,易产生串扰。如果必须并行,可以采用交叉走线或使用地线隔开等策略来降低串扰。

6. **恰当的端接**:在信号线的末端使用适当的端接技术,如RC端接、并联端接、串联端接等,可以减少信号反射。

### 3.1.2 接口卡布局考虑

在布局VITA57.1接口卡时,以下几个布局考虑因素对于保证信号完整性至关重要:

1. **组件放置**:将高速数字组件靠近CPU或FPGA等信号源,并尽量减少与模拟信号组件的交叉干扰。

2. **电源和地平面布局**:电源和地平面应尽可能宽广,为信号提供良好的参考平面,减少电源噪声和地弹。

3. **差分信号对布局**:差分信号对应紧挨着走,并保持恒定的间距,以保证它们受到相同的环境影响,减少外部干扰。

4. **高速连接器布局**:高速连接器应尽量靠近接口卡的边缘,减少信号传输距离,并与相应的接口电路保持一致的阻抗。

5. **散热布局**:考虑高功率组件的散热需求,合理布局散

0

0