CD4518多级计数系统设计:级联技术与同步方法的全面分析

发布时间: 2024-11-30 19:14:12 阅读量: 19 订阅数: 11

参考资源链接:[cd4518引脚图及管脚功能资料](https://wenku.csdn.net/doc/6412b751be7fbd1778d49dfd?spm=1055.2635.3001.10343)

# 1. CD4518多级计数系统设计概述

在当今数字化时代,精确计数成为多种应用的关键。CD4518作为一款广泛应用的双4位二进制计数器,在构建多级计数系统时显示了其独特价值。本章旨在概述CD4518多级计数系统的设计思路,为深入研究级联技术打下基础。

## 1.1 设计背景与意义

CD4518计数系统以其稳定性、可靠性和高精度成为工业和科研领域的首选。在某些应用场景,如频率测量、时间计算等,单个计数器无法满足大范围、高速率计数需求。因此,设计一种能够扩展计数能力的多级计数系统就显得尤为重要。

## 1.2 设计的目标与原则

多级计数系统的设计目标是扩展计数范围,提升计数速度,并保证计数结果的准确性。为了实现这些目标,设计必须遵循以下原则:

- **模块化**:计数系统需要由多个模块级联构成,保持各自独立性的同时实现整体功能。

- **同步性**:所有模块间的数据传输必须同步,避免因时序差异导致的计数错误。

- **扩展性**:系统设计应具有良好的扩展性,方便根据需求增加或减少计数模块。

通过遵循这些原则,我们可以确保CD4518多级计数系统的高效性、稳定性和扩展性。随着后续章节的深入探讨,我们将详细分析每个模块的设计细节及其相互间的协作机制。

# 2. 级联技术的基础理论与应用

## 2.1 级联技术的基本原理

### 2.1.1 级联的定义与重要性

级联技术是一种将多个设备或组件按照特定方式连接起来,使其能够像一个更大、更复杂的系统一样工作的技术。在数字电子学中,级联通常用于扩展计数器、移位寄存器、缓冲器和其他数字电路的功能。定义级联技术的重要性在于它能够实现系统能力的指数级提升,比如在计数系统中,通过级联多个计数器,可以实现更高位数的计数,突破单个计数器位数的限制。

### 2.1.2 级联技术在计数系统中的作用

在CD4518多级计数系统设计中,级联技术的关键作用是能够将多个计数器连接起来,形成一个具有多位计数能力的复合计数器。这不仅增加了系统的计数范围,而且使得设计更加灵活和高效。例如,两个4位的CD4518计数器通过级联可以形成一个8位的计数系统。此外,级联技术还能够减少设计中的组件数量,降低功耗和成本,同时提高系统的可维护性和可靠性。

## 2.2 级联设计的硬件组成

### 2.2.1 CD4518计数器的功能与特性

CD4518是一个双4位同步二进制计数器,每个计数器都有同步清零、同步加载和使能功能。该计数器的输出端可以提供二进制格式的计数值,并且能够通过外部信号实现计数的控制。CD4518计数器的另一个显著特性是它的工作方式可以选择为上升沿触发或下降沿触发。在级联设计中,这些特性使得CD4518计数器能够通过简单的硬件连接实现多级计数。

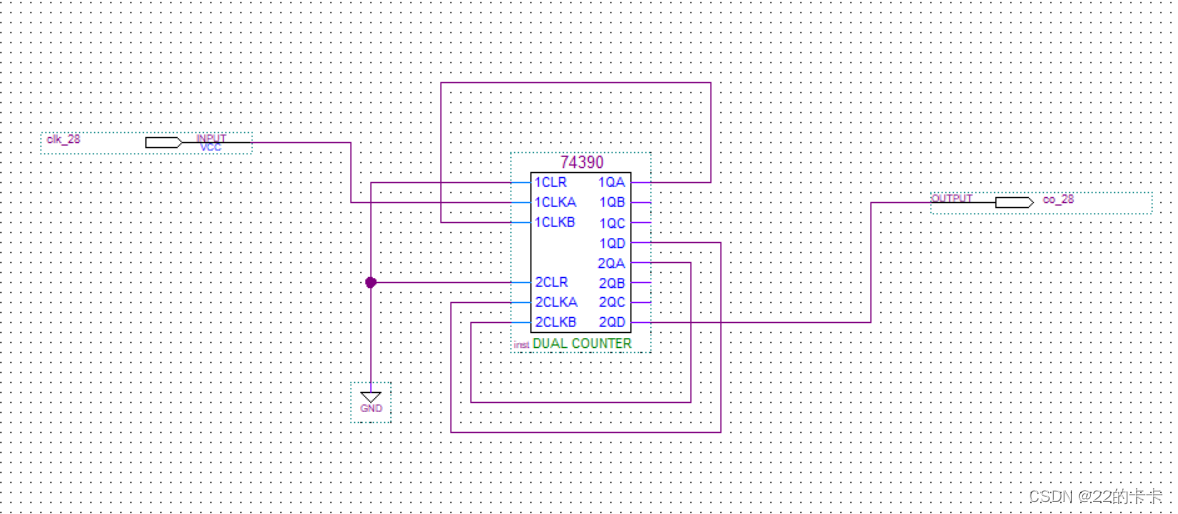

### 2.2.2 级联连接的硬件实现方式

级联连接通常涉及到计数器的输出与下一个计数器的输入端的连接。在CD4518计数系统中,级联连接的实现方式相对简单。主要的连接点是前一个计数器的进位输出(Carry Out)与下一个计数器的使能输入(Enable)。当一个计数器从最大值计数回零(即发生进位)时,该事件会触发下一个计数器开始计数。通过这种方式,多个CD4518计数器可以级联在一起,形成一个能够计数到任意位数的计数器系统。

```mermaid

flowchart LR

A[CD4518 Counter 1] -->|Carry Out| B[CD4518 Counter 2]

B -->|Carry Out| C[CD4518 Counter 3]

C -->|Carry Out| D[...]

D -->|Carry Out| E[CD4518 Counter N]

```

在上图中,箭头表示计数器之间的级联关系。每个计数器的Carry Out信号触发下一个计数器的计数操作。

## 2.3 级联技术的同步机制

### 2.3.1 同步的必要性与实现方式

在级联计数系统中,为了保证计数的准确性,必须实现各级计数器之间的同步。同步机制确保所有计数器在相同的时刻进行状态更新,从而避免计数值的错乱。在CD4518计数器中,同步通常是通过共用时钟信号(Clock Signal)来实现的。所有计数器同时接收到时钟信号,确保它们的计数操作同步进行。

### 2.3.2 同步信号的设计与优化

同步信号的设计是级联技术中最为关键的环节之一。在CD4518计数系统中,设计者需要考虑到信号的传输延迟,以确保所有计数器在相同的时钟边沿触发。可以通过优化电路板的布局来减少传输路径长度,从而降低延迟。此外,使用高速电路设计技术和高质量的信号完整性工具也是优化同步信号的重要手段。优化的目标是确保各级计数器的同步信号几乎没有时间差,以达到最佳的计数精度和系统的稳定性。

```markdown

| 同步设计要素 | 说明 |

| ------------- | ---- |

| 时钟信号分配 | 均匀分配时钟信号,避免偏斜 |

| 信号传输延迟 | 减少路径长度和过孔数量以减少延迟 |

| 电源滤波设计 | 引入去耦电容以提高电源稳定性 |

| 地线设计 | 使用连续的地平面减少干扰 |

```

上述表格总结了同步信号设计时的一些关键要素及其说明。在设计阶段,每个要素都需要细致考虑,以确保系统的同步性能达到最佳。

# 3. CD4518计数系统的设计实践

## 3.1 系统设计前的理论分析

### 3.1.1 计数系统的需求分析

在开始设计CD4518计数系统前,首先需要对系统的需求进行深入分析。这涉及到对计数范围、计数速度、工作电压、工作频率等基本参数的确定。计数范围是系统能够处理的最大数值,而计数速度则涉及到系统对于输入脉冲响应的速率。此外,需要考虑计数系统在不同电压下的稳定性和可靠性,以及在特定频率下的工作性能。

系统的使用场景也是决定需求的关键因素。例如,如果计数系统用于工业控制,可能需要更加注重系统的稳定性与抗干扰能力;若用于科学研究,可能对计数精度和速度有更高的要求。

### 3.1.2 级联技术的可行性分析

级联技术的可行性分析是为了确保通过级联多个CD4518计数器来实现更大范围的计数

0

0