Spartan6开发板高速通信接口设计:PCIe与Gigabit Ethernet深入解析

发布时间: 2024-12-25 01:55:02 阅读量: 4 订阅数: 10

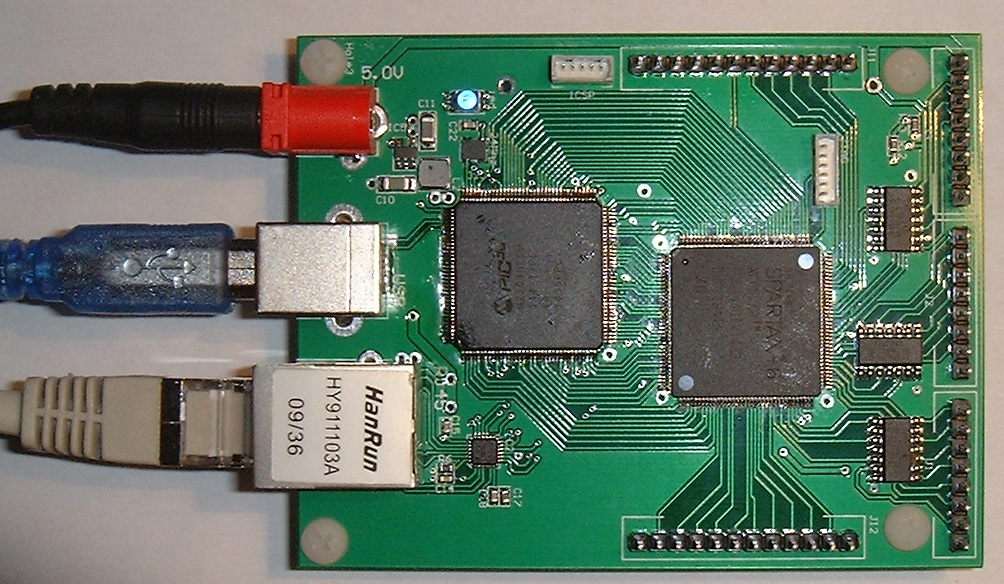

黑金spartan6开发板原理图

# 摘要

随着通信技术的快速发展,Spartan6开发板在高速数据传输中扮演着重要角色。本文详细介绍了Spartan6开发板的高速通信接口,包括PCIe技术的理论基础、硬件设计、固件编程,以及Gigabit Ethernet接口的技术标准、硬件设计和软件实现。文中还探讨了如何将PCIe和Gigabit Ethernet接口集成与优化,并通过实际案例研究分析了Spartan6开发板在高速数据采集系统和网络通信加速器中的应用。最后,本文展望了高速通信接口的未来发展,包括新兴标准的兼容、FPGA技术的演进以及创新应用的前景,强调了高速通信接口技术在5G、AI、物联网和云计算等领域的重要性。

# 关键字

Spartan6开发板;PCIe技术;Gigabit Ethernet;高速通信;硬件设计;软件实现

参考资源链接:[Spartan6开发板详细电路原理及元器件解析](https://wenku.csdn.net/doc/6465798b5928463033ce2d95?spm=1055.2635.3001.10343)

# 1. Spartan6开发板高速通信接口概览

在当今信息爆炸的时代,数据传输的速度和效率已成为评估通信系统性能的关键指标。作为Xilinx Spartan6 FPGA开发板的核心特性之一,高速通信接口在各种高性能计算、网络设备以及数据采集系统中扮演着至关重要的角色。本章将为读者提供一个Spartan6开发板高速通信接口的概览,涵盖PCIe和Gigabit Ethernet技术,并对它们的基本特性和应用场景进行简要说明。

## Spartan6开发板简介

Spartan6系列FPGA是Xilinx公司推出的一款针对成本敏感型市场的高性能可编程逻辑设备。以其低廉的价格和强大的性能,成为了嵌入式系统、通信基础设施以及工业自动化领域中的热门选择。开发板搭载了多个高速通信接口,包括PCI Express (PCIe) 和Gigabit Ethernet,它们使得Spartan6成为实现高速数据传输和处理的理想平台。

PCIe接口允许Spartan6与现代计算机系统实现高速点对点互连,而Gigabit Ethernet则在局域网中提供了高带宽的数据传输能力。这些特性在需要大量数据吞吐量的应用中,如数据采集、网络通信和高性能计算等领域,提供了显著的优势。

随着我们深入探索本章内容,您将了解到这些高速通信接口的技术细节,并学会如何在实际项目中应用它们。接下来的章节将深入探讨PCIe和Gigabit Ethernet的理论基础、硬件设计、固件编程以及软件实现等方面的内容。让我们一起揭开Spartan6开发板高速通信接口的神秘面纱。

# 2. PCIe技术的理论与实践

### 2.1 PCIe架构基础

#### 2.1.1 PCIe总线结构和层次模型

PCI Express (PCIe) 是一种高速串行计算机扩展总线标准,设计用来替代旧有的PCI、PCI-X和AGP总线。PCIe使用点对点连接,允许每个设备直接与CPU通信,这大幅提高了数据传输效率。在架构上,PCIe由三个层次组成:物理层(PHY)、数据链路层和事务层。其中,物理层负责串行数据的发送和接收;数据链路层确保数据包无误地在两个PCIe端点之间传输;事务层则负责处理最终数据包的请求和响应逻辑,类似于OSI模型中的会话层和表示层。

#### 2.1.2 PCIe事务层协议和数据包格式

事务层协议定义了如何在PCIe链路上传输请求和响应,它包括四种主要的数据包类型:内存读写、配置和I/O读写。数据包格式被设计成包含一个或多个头部,每个头部提供不同层次的信息。例如,事务层包(TLP)通常包括请求头、数据负载和结束标记。请求头包含了地址、事务类型、请求长度等信息,而数据负载则包含实际要传输的数据。PCIe标准的严格事务协议保证了复杂系统中的稳定和可靠数据传输。

### 2.2 PCIe接口的硬件设计

#### 2.2.1 Spartan6 PCIe硬核特性

在Xilinx Spartan6 FPGA系列中,硬核PCIe技术提供了一种集成到FPGA设计中的高速串行接口。硬核PCIe解决方案包括了物理层和数据链路层的所有必要组件,用户只需要关注事务层的设计和实现。Spartan6系列的硬核PCIe具有多种速度等级和通道宽度,支持Gen1和Gen2标准,单通道速率达到5 Gbps。硬核PCIe硬核的特性还包括了集成的SERDES(串行/解串器)、时钟数据恢复(CDR)电路、链路训练和状态机(LTSSM)等。

#### 2.2.2 PCIe接口的布线和布局考虑

在实现PCIe接口硬件设计时,布线和布局是关键的步骤,直接影响信号质量与系统稳定性。推荐使用差分信号对进行PCB布局,以确保信号完整性。此外,高速差分信号应尽量等长、并行,减少电磁干扰。在布局时,还应该考虑避免信号交叉和使用多层板设计,从而减少信号损失和干扰。Spartan6开发板上的PCIe接口通常需要遵循一系列设计原则和布局指南,以满足PCIe标准的严格要求。

#### 2.2.3 信号完整性分析和优化策略

信号完整性分析是确保数据传输准确性和速度的关键。在设计PCIe接口时,需要考虑信号的反射、串扰、损耗和时序问题。Spartan6开发板上的PCIe接口可以使用多种工具进行信号完整性仿真,如Cadence Sigrity和Allegro PCB等。仿真可以帮助开发者识别可能的问题,并提出相应的优化策略,如调整终端电阻值、增加去耦合电容、修改布线策略等。这些优化措施有助于确保在高速传输中获得最佳的信号质量。

### 2.3 PCIe接口的固件编程

#### 2.3.1 PCIe端点驱动的开发步骤

PCIe端点驱动的开发涉及多个步骤,从初始化、配置读写、错误处理到电源管理等。在FPGA上实现PCIe端点驱动时,通常要遵循以下步骤:首先,初始化PCIe核,确保链路状态良好;其次,进行配置空间的读写操作,完成资源分配;然后,实现数据传输逻辑,包括内存映射和直接内存访问(DMA)机制;最后,实现错误报告和处理逻辑,确保异常情况下驱动能响应并采取措施。驱动开发通常会使用C/C++结合硬件描述语言(HDL)来完成。

#### 2.3.2 内存映射和DMA传输机制

内存映射是PCIe通信的一个关键概念,它允许端点访问系统内存空间。在Spartan6开发板上,可以通过编程来映射FPGA内部存储器到主机系统的内存地址。DMA传输机制允许数据直接在内存和FPGA内部存储器之间传输,无需CPU介入,极大提升了数据传输效率。实现内存映射和DMA传输需要使用特定的PCIe端点控制器,它们在硬件层面上为这些功能提供了接口,并通过驱动程序在软件层面上进行管理。

#### 2.3.3 高级错误报告和处理机制

PCIe提供了一套完整的错误报告和处理机制,确保通信的可靠性和稳定性。在固件编程中,实现高级错误报告和处理机制意味着编写能够检测和响应错误条件的代码,包括错误更正、错误记录、通知主机系统和进行恢复操作。FPGA端点的PCIe固件需要能够处理数据包校验错误、流控制协议错误、以及链路层错误。高级错误处理不仅提高了系统的健壮性,而且符合PCIe标准的要求,这对于获得认证和进入市场是必不可少的。

通过深入理解PCIe接口的硬件设计、固件编程,以及相关的通信机制,开发者可以设计出高性能、高可靠性的PCIe接口,这将在高速通信技术中发挥关键作用。在下一章节中,我们将深入探讨Gigabit Ethernet接口的理论与实践,比较其与PCIe技术的不同特点和应用场景。

# 3. Gigabit Ethernet接口的理论与实践

## 3.1 Ethernet技术标准演变

### 3.1.1 Ethernet帧结构和协议层次

Ethernet, 作为一种广泛采用的局域网(LAN)技术,自1970年代问世以来,已经经历了多次重要的标准更新和演进。在理解其硬件设计及软件实现前,先熟悉Ethernet的基本架构和帧结构是基础。

Ethernet帧结构包含了一系列的字段:首先是目的地址(Destination Address)和源地址(Source Address),每个地址长度为48比特。随后是类型字段(Type),用来标识上层协议。数据字

0

0