【指令集架构】探索之旅:计算机组成原理实验报告的内核解析

发布时间: 2025-01-03 12:01:11 阅读量: 16 订阅数: 17

# 摘要

本文系统地探讨了计算机组成原理和指令集架构的基础理论及其应用实践。第一章概述了计算机组成原理的基本概念,为深入理解计算机硬件与软件之间的交互打下基础。第二章详细介绍了指令集架构的定义、作用、分类、格式、编码以及性能影响,阐释了其对计算机性能和硬件设计优化的重要性。第三章通过实验报告的解析,阐述了实验方法论、数据收集与分析以及实验结论提炼的过程。第四章着重分析了指令集架构在硬件设计和软件开发中的实际应用,同时对未来的指令集架构进行了展望。最后,第五章通过案例研究深入对比了RISC与CISC架构的原理、特点及发展趋势,为理解不同指令集架构提供了深入见解。

# 关键字

计算机组成原理;指令集架构;硬件设计;软件开发;性能优化;RISC;CISC

参考资源链接:[计算机组成原理实验报告 ](https://wenku.csdn.net/doc/13tmwe3rso?spm=1055.2635.3001.10343)

# 1. 计算机组成原理概述

在探讨计算机技术的各个方面之前,理解计算机组成原理是至关重要的。计算机是一个复杂的系统,它由多个部分协作完成信息的处理、存储和传输。本章将简要回顾计算机硬件的基本组成,以及各组件之间的交互方式。

## 1.1 计算机的基本组成

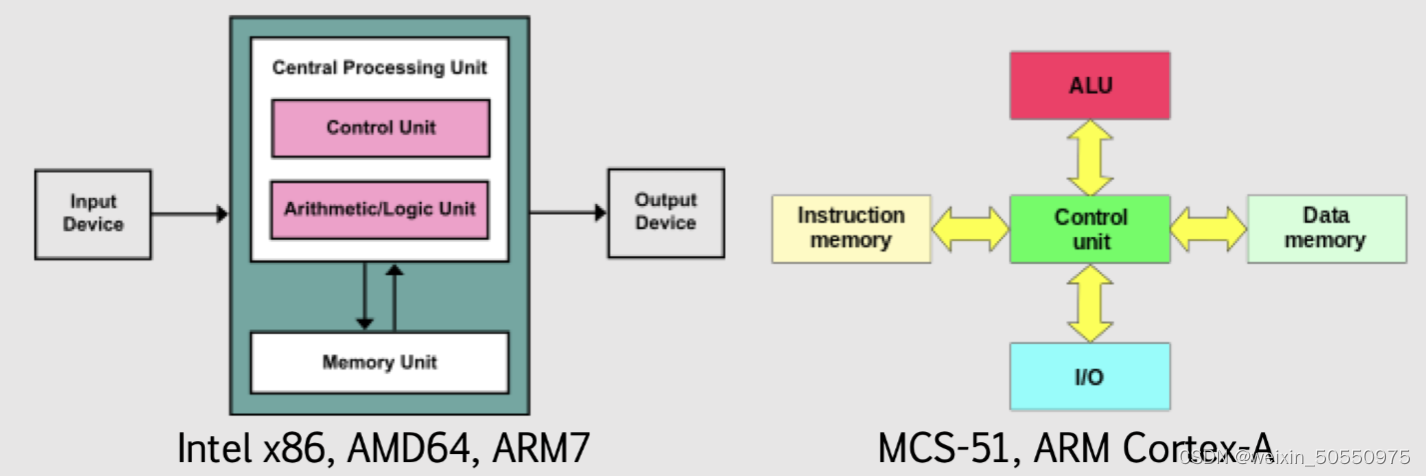

计算机的核心组件包括中央处理器(CPU)、内存、输入/输出设备和存储设备。CPU是计算机的"大脑",负责执行指令和处理数据。内存用于暂存CPU正在处理的数据和指令,输入/输出设备负责与外部环境的信息交换,而存储设备则提供长期的数据保存。

## 1.2 数据表示与处理

在计算机内部,所有的数据和指令都以二进制的形式存在。CPU通过算术逻辑单元(ALU)进行数据的运算,控制单元(CU)协调指令的提取、解码和执行。数据的表示和处理方式对于计算机性能有着直接的影响,它涉及到数据宽度、寻址方式以及指令执行的速度等。

## 1.3 硬件与软件的协同

计算机系统的运行既需要硬件的支撑,也需要软件的配合。软件系统提供了用户交互的界面和应用程序,而操作系统则在硬件和软件之间起到桥梁的作用,负责管理和调度系统资源。硬件和软件的协同工作保证了计算机能够高效稳定地运行。

本章作为入门篇章,为我们后续深入探讨计算机内部的工作原理和指令集架构奠定了基础。通过了解计算机的基本组成和数据处理的基本原理,我们能够更好地理解接下来章节中关于指令集架构的讨论。

# 2. 指令集架构基础理论

## 2.1 指令集架构的概念和作用

### 2.1.1 计算机硬件与指令集的关系

指令集架构(Instruction Set Architecture, ISA)是硬件与软件之间的一层抽象,它定义了计算机硬件能够识别和执行的指令集合,以及这些指令的编码方式、寄存器的使用、内存访问模式等。简而言之,ISA就像是硬件的软件界面,它为程序员和编译器提供了一种编程模型,使得软件开发者不需要关心具体的硬件实现细节,便能编写出在不同计算机上运行的程序。

ISA的设计对硬件的实现方式有直接影响。例如,一个精简指令集(RISC)架构倾向于使用简单的指令和固定的指令长度,这使得处理器的硬件设计可以更加简单高效。相反,复杂指令集(CISC)架构则可能包含更复杂的指令和变长的指令编码,这要求硬件设计中包含更复杂的指令解码逻辑。

ISA的选取也会影响到软件的性能。一些ISA为了提高性能,提供了更多的专门指令来执行特定类型的操作,这可以加快这些操作的执行速度。然而,这样的指令集可能导致编写的程序体积更大,处理速度变慢。

### 2.1.2 指令集架构的分类

指令集架构可以大致分为两大类:复杂指令集计算(CISC)和精简指令集计算(RISC)。CISC架构以Intel的x86架构为代表,它包含了大量的指令和操作模式,旨在通过较少的指令完成复杂的功能。CISC的这一特点使其在较早的计算机时代非常受欢迎,因为那时编译器技术还不够成熟,需要依赖程序员编写更多的底层代码。

而RISC架构则以ARM和MIPS架构为例,它倡导通过简化的指令集和固定的指令长度来提高处理器的执行效率。在RISC架构中,每条指令通常执行单一操作,并且处理器可以更快速地完成指令的取指、译码和执行。这种架构促进了编译器优化技术的发展,因为编译器可以更有效地安排指令的执行顺序,从而提升程序性能。

## 2.2 指令的格式与编码

### 2.2.1 指令格式的组成

指令是计算机程序的基本操作单位,每条指令包含操作码(opcode)和操作数(operand)。操作码指定了处理器应执行的操作类型,例如加法、减法、跳转等;操作数则表示操作的目标或源数据。现代处理器的指令集支持不同类型的指令格式,包括但不限于立即数(immediate)、寄存器(register)、寄存器间接和内存寻址等。

指令格式的设计必须兼顾指令编码的效率和易解码性。例如,固定长度的指令编码可以简化处理器的指令解码逻辑,但可能无法充分利用指令空间,导致编码效率不高。而变长指令编码虽然可以更高效地使用指令空间,但可能会增加解码逻辑的复杂度。

### 2.2.2 操作码和操作数的编码

操作码是用于指定操作类型的字段,通常在指令格式中占据一定数量的比特位。为了使指令集能够支持更多的操作,设计者通常会对操作码进行编码,这可以通过简单的二进制编码或者更复杂的变长编码来实现。例如,ARM指令集采用32位固定长度编码,其中操作码通常集中在指令的前4个比特。

操作数的编码则依据不同的寻址模式而有所不同。常见的寻址模式包括立即数寻址、寄存器寻址、直接寻址、间接寻址和基址加偏移量寻址等。每种寻址模式都有其适用场景,例如,立即数寻址适用于直接使用常量值的场景,而寄存器寻址适合频繁操作的场景。为了正确执行指令,处理器必须能够根据操作码和操作数的编码信息正确解析出操作类型和操作数的值。

## 2.3 指令集与性能

### 2.3.1 指令并行性的概念

在现代处理器中,指令的并行执行是提高性能的关键技术之一。指令并行性是指处理器能够同时处理多条指令的能力。简单来说,它包括了指令级别的并行性(ILP)和数据级别的并行性(DLP)。ILP允许处理器在一个时钟周期内执行多个指令,而DLP指的是对同一数据集进行并

0

0