【硬件描述语言】:深入理解TestBench的并行性与事件驱动模型

发布时间: 2025-01-04 16:19:25 阅读量: 17 订阅数: 14

# 摘要

硬件描述语言(HDL)是设计和测试集成电路的基础工具,而TestBench是验证硬件设计正确性的关键组成部分。本文详细介绍了TestBench的并行性原理及其在硬件仿真中的重要角色,深入探讨了进程和任务的概念及其应用,以及并行事件的管理和同步机制。随后,文章阐述了事件驱动模型的基础知识,包括工作机制和触发处理,并讨论了其在验证中的应用。实践应用章节通过实例研究了并行TestBench环境的构建,以及事件驱动模型在故障注入与监控中的实践。最后,文章展望了TestBench技术的高级主题和未来发展,包括自动化测试用例管理、验证方法学的创新,以及人工智能、机器学习和跨域验证技术的潜力和方向。

# 关键字

硬件描述语言;TestBench;并行性原理;事件驱动模型;故障注入;自动化测试;形式化验证

参考资源链接:[Verilog Testbench详解:模块测试与激励信号生成](https://wenku.csdn.net/doc/34i1ooncbf?spm=1055.2635.3001.10343)

# 1. 硬件描述语言与TestBench概述

在现代数字系统设计中,硬件描述语言(HDL)扮演着至关重要的角色,它使得设计师能够通过高级的抽象层来描述和模拟硬件的行为。而TestBench,作为硬件验证的核心部分,用于对硬件描述进行测试,确保其符合设计规格和性能要求。在本章中,我们将概述硬件描述语言的基本知识,以及TestBench的基本结构和工作原理。理解这些基础知识是深入研究TestBench并行性原理和事件驱动模型的先决条件。

硬件描述语言(HDL)如VHDL和Verilog,允许工程师以文本形式精确地描述复杂的电子系统。HDL不仅限于描述硬件的结构,还可以描述其功能和时序。这些描述经过综合和优化,最终生成可以在实际硬件上执行的门级网表。

TestBench是一种特殊的HDL代码,它不直接转化为硬件,而是用于生成输入信号、监视输出信号、比较预期输出与实际输出,并记录测试结果。TestBench的主要目标是通过提供一个可控的环境来验证硬件设计的正确性。在本章的后半部分,我们将探究TestBench的基本组件,以及如何编写简单的TestBench来验证基本的硬件描述。

# 2. TestBench并行性原理

### 2.1 并行性在硬件仿真中的角色

#### 2.1.1 并行性概念解释

并行性是指在给定时间内,多个进程或任务同时执行的能力,它使得计算资源可以同时处理多个操作。在硬件仿真领域,尤其是在创建TestBench时,利用并行性可以大幅度提升仿真效率。由于硬件电路本身是并行工作的,因此在仿真中模拟其行为时,也必须考虑并行性来确保仿真的真实性和效率。

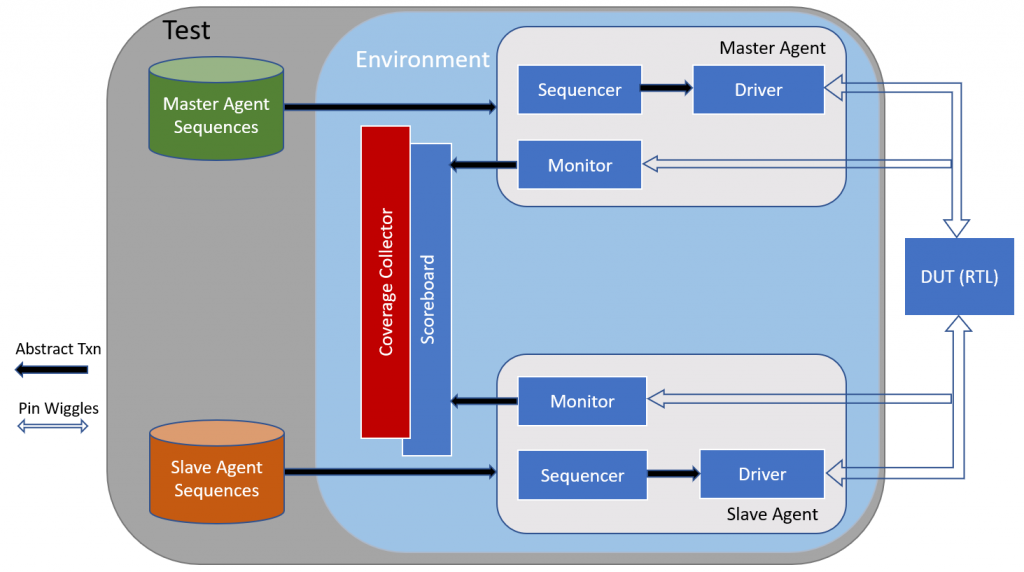

在硬件仿真中,TestBench负责生成仿真环境所需的激励信号,并监测DUT(Design Under Test)的行为是否符合预期。传统上,TestBench中的测试用例顺序执行,这种方式对于复杂设计和长周期仿真会导致仿真时间过长。通过引入并行性,仿真可以同时运行多个测试用例,这不仅可以缩短整体仿真时间,还可以提高硬件设计的验证覆盖率。

#### 2.1.2 并行性与仿真性能

并行性对仿真性能的提升,可以从多个方面进行评估。首先,当多个测试用例并行运行时,可以充分利用多核处理器的能力,减少因等待单个测试用例完成而造成的空闲时间。其次,并行性还可以提高测试用例的执行速度,因为多个测试用例可以共享内存和其他资源,减少了对资源的竞争和等待时间。

然而,采用并行性并不总是带来性能提升。在并行系统中,不同的进程或任务间可能存在数据依赖关系,如果不妥善管理这些依赖关系,反而可能产生竞争条件(race condition),导致仿真结果不稳定。因此,在设计TestBench时,必须小心地设计并行策略,以实现性能提升而避免潜在问题。

### 2.2 TestBench中的进程和任务

#### 2.2.1 进程的概念及其在TestBench中的应用

在硬件描述语言(HDL)中,进程是描述并行行为的基本单位。在Verilog中,进程的概念对应于始终块(always block),而在VHDL中则对应于进程块(process block)。这些进程块可以在不同的时刻被触发,并且可以独立于其他进程块运行。

在TestBench中,进程被用来模拟DUT的不同方面,例如模拟不同的输入信号源,或者模拟各种环境条件对DUT的影响。利用进程的并行特性,可以同时处理多个信号源或环境,这样就能够在仿真中重现更加真实的场景,并提升验证的全面性。

#### 2.2.2 任务的定义和调度机制

除了进程,HDL还提供了任务(task)的概念,用于简化可重用代码的编写。任务不像进程那样具有并行性,它们在被调用时执行其内容,然后返回。在TestBench中,任务可以用来封装一些复杂的验证逻辑,使得代码更加模块化和易于管理。

任务的调度是由仿真器在运行时自动管理的。当一个任务在TestBench中被调用时,仿真器会安排任务在合适的时间执行。任务可以在进程内被调用,也可以在其他任务内被调用。但要注意,如果任务内含有对共享资源的访问,则可能需要特别的同步机制来确保数据的一致性和访问安全。

### 2.3 并行事件的管理

#### 2.3.1 事件队列和调度顺序

在并行的硬件仿真环境中,事件(例如信号状态改变)需要被记录并在合适的时间被处理。事件通常被放入事件队列中,仿真器根据优先级和时间戳来调度事件的执行顺序。正确管理这些事件队列是确保仿真实时性和正确性的重要部分。

事件队列的实现需要考虑多个因素,例如怎样处理具有相同时间戳的多个事件,以及如何处理事件优先级。一个设计良好的事件队列可以确保事件按照预定的顺序被正确处理,这样就可以模拟硬件电路中信号传播和处理的真实时序。

#### 2.3.2 并行测试中的事件同步与互斥

在并行测试中,多个进程或任务可能会同时操作共享资源,例如寄存器、内存位置或信号。这就需要一些机制来同步这些操作,确保在任一时刻只有一个进程或任务能够修改资源,从而避免数据竞争和条件竞争。

事件同步和互斥可以通过锁(lock)、信号量(semaphore)、屏障(barrier)等同步机制来实现。这些机制确保了并行操作的安全性,但同时也增加了额外的开销,因此在设计时需要平衡性能和同步需求。

#### 2.3.3 代码示例与逻辑分析

```verilog

// Verilog代码示例:并行事件处理示例

module testbench;

reg event1, event2;

// 进程1:产生事件1

always @(posedge clk) begin

event1 <= #10 1'b1;

end

// 进程2:产生事件2

always @(posedge clk) begin

event2 <= #15 1'b1;

end

// 任务:处理两个事件

task handle_events;

if (event1) begin

// 处理事件1...

event1 <= #5 1'b0;

end

if (event2) begin

// 处理事件2...

event2 <= #5 1'b0;

end

endtask

// 主进程:并行处理两个事件

initial begin

while (1) begin

#10; // 延迟一段时间,模拟真实环境

handle_events; // 调用任务处理事件

end

end

endmodul

```

0

0