IP5306 I2C信号完整性:问题诊断与优化秘籍

发布时间: 2024-12-25 00:39:18 阅读量: 3 订阅数: 8

罗克韦尔自动化:支持CIP Security的工业控制设备.pdf

# 摘要

I2C通信协议因其简单高效在电子系统中广泛使用,然而信号完整性问题会严重影响系统的稳定性和性能。本文首先对I2C信号完整性进行概述,深入分析了I2C通信协议的基本概念和物理层设计要点,接着探讨了I2C信号完整性问题的诊断方法和常见故障案例。在优化策略方面,文中提出了从电路设计、软件优化到元件选择与管理的多层面解决方案,并通过IP5306 I2C信号完整性优化的实战演练,验证了这些策略的有效性。本文旨在为I2C系统的可靠性提供科学的分析方法和优化指南。

# 关键字

I2C信号完整性;通信协议;信号特性;电路设计;软件优化;元件管理

参考资源链接:[IP5306-I2C充电宝芯片V1.4:I2C协议详解及操作指南](https://wenku.csdn.net/doc/775o4rzybh?spm=1055.2635.3001.10343)

# 1. I2C信号完整性概述

## 1.1 信号完整性的重要性

在电子系统设计中,I2C信号完整性对于保证数据传输的准确性和系统稳定性至关重要。由于I2C是一种多主从设备的串行通信总线,信号完整性问题可能会导致数据错误、通信中断甚至系统故障。因此,深入理解并优化I2C信号完整性是硬件工程师和系统设计师在产品设计和调试阶段必须面对的关键任务。

## 1.2 影响信号完整性的因素

I2C信号完整性可能受到多种因素的影响,包括但不限于:

- 板级设计,如线路长度、布线和PCB布局。

- 信号质量,如抖动、反射、串扰和电源噪声。

- 元件选择,例如上拉电阻的大小和电源质量。

## 1.3 信号完整性优化的目标

优化I2C信号完整性的目标是确保高速、可靠的数据传输和设备间的兼容性。这需要设计时考虑到时序兼容性、电气兼容性和电磁兼容性,以及对设计进行细致的测试和调整。只有这样,才能在满足性能要求的同时,延长设备的使用寿命,并减少维护成本。接下来的章节将详细介绍I2C通信协议、信号完整性问题的诊断方法、优化策略以及如何在实战中应用这些知识。

# 2. I2C通信协议深入分析

## 2.1 I2C协议基本概念

### 2.1.1 I2C协议的起源与发展

I2C(Inter-Integrated Circuit),即“内部集成电路总线”,由荷兰飞利浦半导体公司(现为NXP Semiconductors)于1982年引入。最初设计是为了解决微控制器与各种外围设备之间的低速数据交换需求。作为串行通信的一种,I2C协议因其简单易用、硬件需求低、支持多主多从等特性,成为电子设计中最流行的通信协议之一。

经过几十年的发展,I2C技术经历了多次标准的更新,包括但不限于支持更高传输速率的快速模式(Fast-mode)、增强型快速模式(Fast-mode Plus)、高速模式(High-speed mode)以及最新的超快速模式(Ultra Fast-mode)等。这些扩展允许I2C协议在不同的应用场景中,根据对速度和距离的需求来选择合适的通信模式。

### 2.1.2 I2C协议框架和工作机制

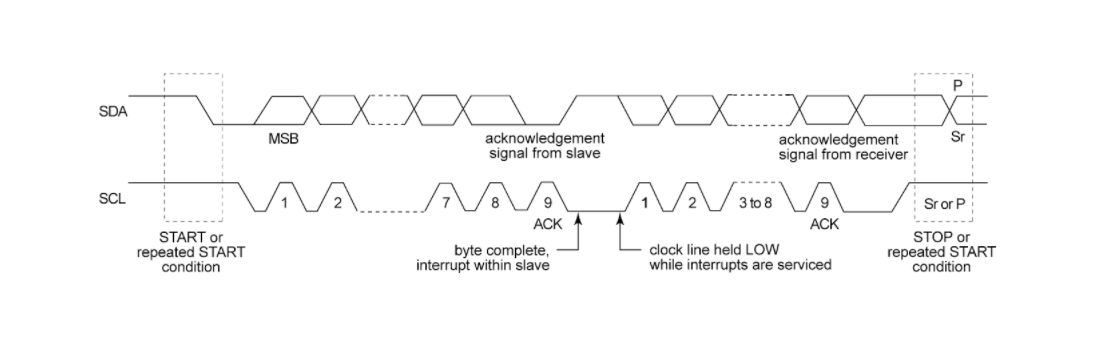

I2C协议的核心在于其总线概念,其使用两条信号线:串行数据线(SDA)和串行时钟线(SCL)。所有连接到I2C总线的设备都通过这两条线进行通信。一条总线上可以连接多个主设备(Master)和从设备(Slave),设备通过地址进行区分。

在通信过程中,主设备发起传输,通过SCL线提供时钟信号,SDA线则用于数据传输。数据以8位字节的形式进行传输,每传输一个字节后都会有一个应答位(ACK)或非应答位(NACK),用于确认数据是否成功接收。

I2C协议支持多主模式,即多个主设备可以尝试控制总线,但在同一时间只能由一个主设备控制总线。为了避免冲突,I2C协议中设有仲裁机制。当多个主设备同时尝试发送数据时,通过比较SDA线上电平的高低来决定哪个主设备获得总线控制权。

## 2.2 I2C信号特性与要求

### 2.2.1 信号电平与传输速率

I2C总线的信号电平通常为逻辑电平,并且与供电电压相关。在5V系统中,逻辑"1"可能被定义为2.4V到5V之间的任意值,逻辑"0"则为0到0.4V之间的值。在现代低功耗设计中,I2C总线的电压可能远低于5V,比如1.8V或3.3V。信号电平的定义必须与所使用的设备兼容。

传输速率是I2C通信的重要参数,快速模式的最大传输速率可达400kbps,高速模式下可以达到3.4Mbps。传输速率的增加也对信号的质量提出了更高的要求。高速模式对信号的上升和下降时间有更严格的要求,以避免信号完整性问题。

### 2.2.2 信号抖动与时钟同步

信号抖动是数字电路中常见的现象,是指信号边沿的随机变化。在I2C通信中,信号抖动可能会造成时钟线上的不稳定性,进而影响数据的同步和准确性。信号抖动可能由电磁干扰(EMI)、电源噪声或高速信号线的反射等因素造成。

为确保数据的正确同步,I2C协议引入了时钟同步机制,即主设备在发送时钟信号时,需等待所有从设备的响应。当主设备检测到SCL线被拉低时,表示有从设备需要更多时间来处理数据,此时主设备会暂停发送数据,直到SCL线再次释放。

## 2.3 I2C物理层设计要点

### 2.3.1 线路设计与布局考虑

I2C总线的线路设计和布局对信号完整性至关重要。为了减少信号反射和串扰,应尽可能缩短信号路径的长度。在PCB布局时,应将I2C设备紧挨在一起,并且SDA和SCL信号线应保持尽可能平行且靠近。

通常建议在设计中加入端接电阻,以减少信号反射。端接电阻值的确定需要根据总线的电容负载和电缆长度来计算。在高速I2C系统中,可能还需要考虑终端匹配网络的设计。

### 2.3.2 终端匹配与噪声抑制

I2C总线的终端匹配对于信号的完整性和抗干扰能力至关重要。在I2C总线的两端加入上拉电阻至供电电压,确保当总线空闲时,SDA和SCL线路被保持在高电平状态。上拉电阻的阻值需要根据总线的电容负载和设备要求来选择,既不能太大影响信号的上升时间,也不能太小导致过大的静态电流。

为了进

0

0