【多层次PCB设计】:Zynq-7000 SoC的复杂性管理与优化指南

发布时间: 2025-01-04 22:39:50 阅读量: 12 订阅数: 15

Xilinx Zynq-7000系列原理图PCB封装库(AD库)

# 摘要

本文旨在全面探讨多层次PCB设计和Zynq-7000 SoC在现代电子系统中的应用。首先,对Zynq-7000 SoC架构及其处理器与FPGA的集成技术进行了深入解析,重点分析了内存管理策略和I/O接口技术。随后,文章转向多层次PCB设计,详细介绍了设计前期的准备工作、布局和布线策略以及设计验证和仿真的重要性。特别强调了设计优化案例,如性能优化和散热策略,以及测试与故障排除的方法。最后,探讨了当前PCB设计中所使用的工具与资源,包括软件选型、设计资源管理和设计社区的专业支持。本文为设计师提供了一个全面的多层次PCB设计和Zynq-7000 SoC应用的参考资料,有助于提升设计效率和系统性能。

# 关键字

PCB设计;Zynq-7000 SoC;处理器集成;内存管理;布线策略;散热策略

参考资源链接:[Zynq-7000 SoC PCB设计指南:UG933修订历史与布局要点](https://wenku.csdn.net/doc/5husxataqm?spm=1055.2635.3001.10343)

# 1. 多层次PCB设计概述

## 1.1 PCB设计的基本概念

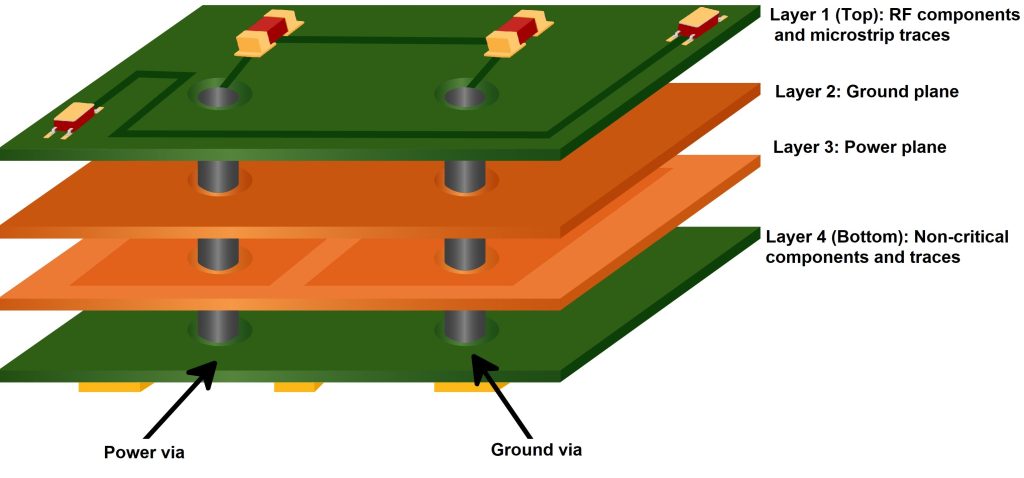

在电子信息工程领域,印刷电路板(PCB)作为电子设备的核心组成部分,承载着电子元器件以及它们之间的电气连接。多层次PCB设计是指在一个PCB内包含多个信号层、电源层和地平面层,通过精细的布局布线,实现信号传输的最优化和电磁兼容性(EMC)的保证。

## 1.2 多层次PCB设计的重要性

随着电子产品的性能要求日益提高,单一或双面板已经无法满足复杂电路设计的需求。多层次PCB设计能够有效减小PCB面积、提高信号质量、增强电路稳定性和抗干扰能力,从而显著提升产品的性能和可靠性。此外,它也是实现高速信号完整性和低功耗设计的关键技术。

## 1.3 设计流程概述

多层次PCB设计流程包括多个阶段:项目规划、原理图设计、PCB布局、布线、设计验证和输出制造数据。每个阶段都需要对设计进行评估和优化,以确保最终产品的质量和性能。设计工程师需要掌握一系列专业工具和技巧,这涉及到精确计算、仿真分析以及遵循设计规则。

# 2. Zynq-7000 SoC架构解析

## 2.1 Zynq-7000 SoC的处理器和FPGA集成

### 2.1.1 双核ARM Cortex-A9 MPCore处理器介绍

Zynq-7000系列系统级芯片(SoC)由Xilinx开发,具有独特的处理器和可编程逻辑的集成。其中处理器部分由双核ARM Cortex-A9 MPCore构成,为高性能计算任务提供了坚实的基础。ARM Cortex-A9 MPCore处理器设计用于实现高性能与能效比的平衡,它支持ARM的v7指令集,并在设计中融入了NEON技术,专门针对高吞吐量和信号处理进行了优化。

该处理器核心运行频率高达1 GHz,并且支持双精度浮点单元(FPU)。多核处理器之间的同步和负载分配,通过内部集成的Snoop Control Unit(SCU)和Global Interrupt Controller(GIC)实现,这允许核心间高效协作,减少通信延迟。

双核Cortex-A9处理器的集成使得Zynq-7000 SoC能够在执行应用层软件时,如操作系统和用户应用程序,达到出色的性能表现。这一点在嵌入式系统领域尤为宝贵,因为它能够处理图形、视频处理和复杂的算法运算任务。

### 2.1.2 可编程逻辑的FPGA结构分析

可编程逻辑部分由Xilinx的7系列FPGA架构组成,它为Zynq-7000 SoC提供了可编程的灵活性和强大的数据处理能力。这部分由逻辑阵列、DSP单元、存储资源和高级输入/输出资源构成。逻辑阵列由大量的查找表(LUTs)、触发器、和布线资源组成,这些资源可用来实现各种数字逻辑和存储功能。

DSP单元则专注于执行乘累加运算,用于数字信号处理等高性能计算应用。存储资源包括了各种大小和类型的RAM块,可以实现诸如缓存、缓冲区、以及复杂数据结构的存储。而高级输入/输出资源则包括了高速串行接口,如PCIe、SATA、以及千兆以太网接口等。

这种FPGA结构在Zynq-7000 SoC中承担了重要的角色。首先,它使得设计者能够在硬件级别实现加速,对特定的计算密集型任务进行优化。其次,它的灵活性意味着设计者可以根据需要调整逻辑功能,甚至是系统运行后,依然能够对功能进行升级和修改。

## 2.2 Zynq-7000 SoC的内存管理

### 2.2.1 内存架构和缓存机制

Zynq-7000 SoC采用了灵活而高效的内存架构设计,以支持双核Cortex-A9处理器的高效运行。内存架构不仅包括了处理器内置的一级(L1)和二级(L2)缓存,还包括了外部的DDR内存接口。L1缓存提供了极低的延迟访问,分为数据缓存和指令缓存,通常大小为32KB,而L2缓存则是两个核心共享的,大小可达512KB。这有助于在执行指令和数据访问时减少延迟和提高吞吐量。

此外,Zynq-7000 SoC还支持高达4GB的DDR3或DDR3L内存,通过多通道内存接口实现了高带宽和高容量的内存访问。与FPGA部分的数据交换通过Advanced eXtensible Interface (AXI)进行,这是一种高性能的协议,能够保证处理器与FPGA之间高效的数据传输。

### 2.2.2 外部存储器接口配置

除了处理器内部和处理器与DDR内存之间的接口外,Zynq-7000 SoC的外部存储器接口配置也极为重要。这些接口支持多种类型的存储器,如NAND Flash、NOR Flash、以及SD/SDIO卡等。通过这些接口,系统可以访问程序代码和大量数据,包括操作系统镜像、文件系统以及用户数据。

配置和使用外部存储器接口需要综合考虑性能、成本和尺寸等因素。例如,对于需要频繁读写的存储任务,可能需要选择具有较高写入速度的NAND Flash。而对于需要保证数据完整性和长期存储的任务,则可能需要选择NOR Flash,尽管其成本和写入速度可能不如NAND Flash。

Zynq-7000 SoC提供了灵活的配置选项,设计者可以根据应用需求,选择合适的存储器类型以及配置接口参数,如时序、速度等级等。通过这些配置,可以优化整体系统的性能和成本,以及满足特定的可靠性要求。

## 2.3 Zynq-7000 SoC的I/O和接口技术

### 2.3.1 高速串行接口标准

Zynq-7000 SoC拥有多种高速串行接口,以支持大量数据和高速信号的传输。这些接口是现代通信系统和数据采集系统的关键部分,包括了诸如PCI Express (PCIe)、千兆以太网(GigE)、以及 Serial ATA (SATA)等标准。

PCI Express接口能够在Zynq-7000 SoC上实现高性能的硬件加速和高速数据通信。例如,它可用于连接外部高性能图形处理单元(GPU)

0

0