数字电路设计入门:简易裁判表决器构建指南

发布时间: 2024-12-26 20:31:34 阅读量: 7 订阅数: 10

# 摘要

本文系统介绍了数字电路设计的基础知识,包括数字电路的组成、分类、信号和逻辑级别以及分析工具。在此基础上,深入探讨了逻辑门和逻辑表达式的设计、组合及其应用。文章重点论述了裁判表决器的设计理论、工作原理以及实现过程,强调了公平性和一致性的重要性,并提供了实现裁判表决器的电路设计和物理实现步骤。最后,本文详细阐述了裁判表决器的测试方案、性能评估以及问题解决与改进措施,旨在为类似系统的开发提供参考和指导。

# 关键字

数字电路设计;逻辑门;逻辑表达式;裁判表决器;测试与验证;电路实现

参考资源链接:[数字电路课程设计-裁判表决电路](https://wenku.csdn.net/doc/649d265c50e8173efdb2779d?spm=1055.2635.3001.10343)

# 1. 数字电路设计基础知识

数字电路是电子系统中的基础构件,它通过离散的信号电平来表示和处理信息。数字电路设计涉及从基本的逻辑门电路到复杂的处理器设计的各个方面。

## 1.1 数字电路的组成与分类

数字电路主要由逻辑门电路组成,这些门电路以基本的"开"和"关"状态对应二进制的"1"和"0"。它们可以被分类为组合逻辑电路和时序逻辑电路。组合逻辑电路的输出仅取决于当前输入,而时序逻辑电路的输出不仅取决于当前输入,还取决于先前的状态。

## 1.2 信号和逻辑级别

在数字电路中,信号通常具有两个逻辑级别,分别是高电平(逻辑1)和低电平(逻辑0)。这些级别的电压值由电路设计规范定义,例如,TTL(晶体管-晶体管逻辑)电路中,高电平约为5伏,低电平约为0伏。

## 1.3 常用数字电路分析工具简介

为了设计和分析数字电路,工程师通常会使用一系列工具。这些工具包括逻辑模拟器,如Logisim或Multisim,它们允许用户在没有物理组件的情况下测试电路设计;还有硬件描述语言(HDL),如VHDL或Verilog,它们可以用来在高层次上描述电路的行为,随后进行综合和仿真。

```mermaid

graph TD

A[数字电路基础] --> B[组成与分类]

A --> C[信号和逻辑级别]

A --> D[分析工具简介]

```

通过这张流程图,我们可以看到数字电路设计基础知识的三个主要领域,每个领域都是数字电路设计不可或缺的一部分。

# 2. ```

# 第二章:逻辑门和逻辑表达式

## 2.1 基本逻辑门介绍

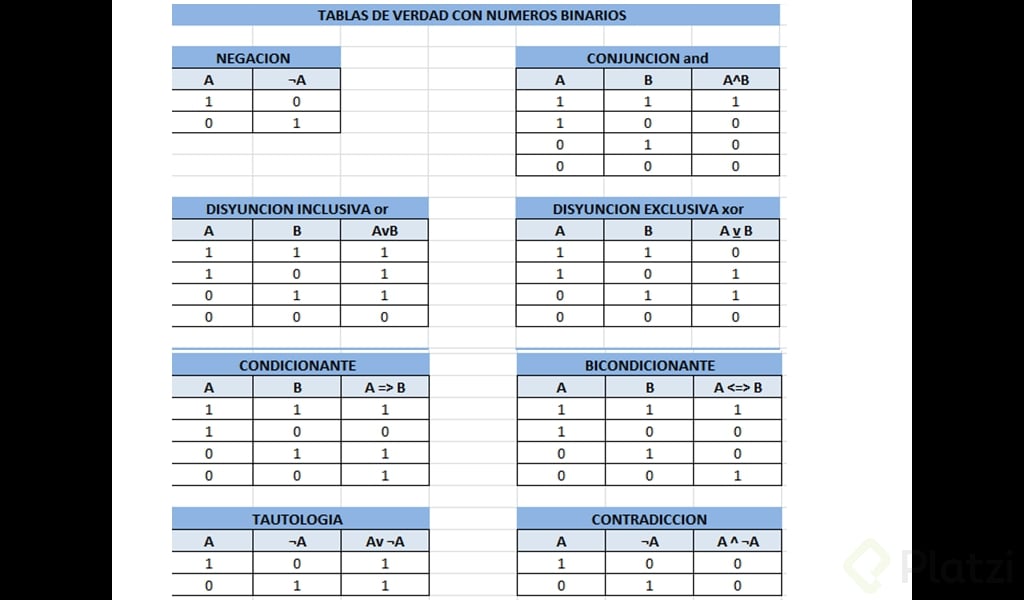

### 2.1.1 与门(AND)

与门是最基础的逻辑门之一,在数字电路中表示逻辑乘法操作。只有当所有输入都为高电平(1)时,输出才为高电平(1);否则,输出为低电平(0)。其逻辑表达式可以表示为:Y = A·B,其中Y为输出,A和B为输入。

```

输入A 输入B 输出Y

0 0 0

0 1 0

1 0 0

1 1 1

```

在实际电路设计中,与门通常用于实现组合逻辑,它与其它逻辑门结合可以构建出复杂的逻辑功能。

### 2.1.2 或门(OR)

或门在数字电路中表示逻辑加法操作。当至少有一个输入为高电平(1)时,输出即为高电平(1);如果所有输入都为低电平(0),输出才为低电平(0)。其逻辑表达式可以表示为:Y = A + B。

```

输入A 输入B 输出Y

0 0 0

0 1 1

1 0 1

1 1 1

```

或门常用于实现选择性逻辑,例如在多输入条件的判断中,一个或多个条件满足时,即可得出相应的结果。

### 2.1.3 非门(NOT)

非门是一个简单的逻辑门,它只有一个输入和一个输出,其功能是反转输入的逻辑电平。如果输入为高电平(1),输出就为低电平(0),反之亦然。其逻辑表达式可以表示为:Y = ¬A。

```

输入A 输出Y

0 1

1 0

```

非门在逻辑表达式中起着关键的作用,它是逻辑运算中不可或缺的基础元素,用于实现逻辑电路的反向功能。

## 2.2 逻辑表达式的基础

### 2.2.1 逻辑表达式的构建

构建逻辑表达式是数字电路设计的核心步骤之一。一个有效的逻辑表达式可以精简电路设计,从而减少资源的消耗。构建逻辑表达式首先需要定义问题的输入输出关系,然后根据这些关系和逻辑门的功能,写出对应的表达式。

例如,对于一个简单的两输入表决器,它的要求是只有当两个输入都为1时输出才为1,否则输出为0。构建出的逻辑表达式就是Y = A·B。

### 2.2.2 表达式的简化与布尔代数

布尔代数是处理逻辑表达式的数学分支,它提供了一系列法则来简化逻辑表达式。例如,德摩根定律就经常用于将复杂的逻辑表达式简化。简化逻辑表达式有助于减少所需的逻辑门数量,优化电路设计。

例如,表达式Y = (A + B)·(A + ¬B)可以通过布尔代数简化为Y = A。这是因为(¬B + A) = A,因为B和¬B是互斥的,它们的和一定为真。

## 2.3 逻辑门的组合与应用

### 2.3.1 复合逻辑门设计

复合逻辑门是通过将基本逻辑门组合起来实现更复杂的逻辑功能。例如,一个包含与门和或门的电路可以实现XOR(异或)逻辑。

设计复合逻辑门时,可以使用逻辑门图、真值表或者卡诺图等工具。每一种工具都提供了不同的视角和方法来设计电路。

### 2.3.2 逻辑门的级联与优化

级联是将逻辑门按一定的顺序连接起来。级联电路可以实现更复杂的逻辑功能,但是级联太多可能会导致电路性能下降。因此,逻辑门级联和优化是设计过程中要考虑的重点。

在优化逻辑门级联时,可以考虑减少延时、降低功耗、减小电路尺寸等因素。通过使用更少的门或者更优化的逻辑组合,我们可以提高整个电路的效率和可靠性。

```

# 3. 裁判表决器设计理论

裁判表决器是一种基于特定算法实现公平决策的电子设备。在体育竞赛、投票选举等多个领域扮演着关键角色。正确理解其设计理论对于确保裁判表决器能公正无误地执行任务至关重要。本章节将深入探讨裁判表决器的设计要求、工作原理和数学模型,为裁判表决器的构建与实现打下坚实的基础。

## 3.1 裁判表决器的工作原理

裁判表决器的工作原理涉及将多个输入信号(即裁判的判决)通过特定的逻辑电路进行处理,从而得出最终的表决结果。在处理过程中,需要考虑诸如表决器应能有效处理不同输入的组合,并且在特定情况下要能实现故障容错。

在工作原理上,表决器可以被视作一个黑盒,其内部可采用不同的电路和算法设计。例如,一个简单的多数表决器(Majority Voter)会根据“多数人决定”的原则输出结果。而更加复杂的表决器可能会运用更高级的算法来处理输入信号,减少错误判决的影响。

## 3.2 表决逻辑的设计要求

为了保证裁判表决器的准确性和公平性,表决逻辑的设计需遵循特定的要求。我们来深入探讨这些要求。

### 3.2.1 公平性和一致性

一个裁判表决器在设计时,必须保证其输出结果具有高度的公平性和一致性。这意味着表决器在相同输入的情况下应当输出相同的结果,对于输入信号的微小变动不应产生剧烈的输出变化,以避免误判。

公平性和一致性在设计中体现为对输入信号的加权处理,确保没有任何单一输入能够主导整个表决结果。设计时,还需要考虑算法的鲁棒性,使得表决器能适应不同场合的需要,并保持公正。

### 3.2.2 简化表决逻辑的策略

简化表决逻辑有助于减少表决器的实现复杂度和潜在的故障点。简化的方法包括逻辑表达式的优化和使用标准化的电路模块。例如,使用卡诺图(Karnaugh Map)来简化布尔表达式,可以有效降低逻辑门的数量,减少电路的复杂性。

在实现方面,选择合适的集成电路(IC)可使设计更为紧凑。此外,软件辅助设计工具可以在设计阶段发现逻辑错误,提高整体设计效率和准确性。

## 3.3 裁判表决器的数学模型

在设计裁判表决器时,采用数学模型可以更精确地描述表决器的工作原理和逻辑关系。接下来,我们将介绍投票系统的基础数学概念以及逻辑等价与投票算法。

### 3.3.1 投票系统的数学基础

投票系统的基本数学模型通常涉及布尔代数和集合论。每个裁判的判决可以被视作一个二进制变量,所有裁判的判决组合则形成一个n维的布尔空间。表决逻辑可以被建模为从这个布尔空间到最终决策的映射。

为了准确地表达表决逻辑,引入数学工具如概率论和组合数学来分析不同裁判判决组合出现的概率以及对最终结果的影响。这些模型有助于评估表决器在不同场景下的性能和准确性。

### 3.3.2 逻辑等价与投票算法

在表决器设计中,一个关键的概念是逻辑等价,即两个逻辑表达式在相同的输入下能产生相同的结果。通过逻辑等价的概念,可以将复杂的逻辑表达式简化为更简洁的形式,这在优化表决器的逻辑电路设计时尤为重要。

投票算法是指用于处理裁判判决的数学过程。常见的算法包括简单多数算法、加权多数算法等。每种算法都有其适用场景和优缺点。设计时需要根据具体需求选择合适的算法,并对算法进行调整以满足表决器的特定设计要求。

在本章节中,我们探讨了裁判表决器的设计理论基础。接下来章节将具体讨论如何构建和实现一个裁判表决器。

# 4. 裁判表决器的构建与实现

裁判表决器是数字电路设计中的一个复杂应用案例,其设计和实现涉及到电路理论、逻辑设计、硬件搭建等多个方面。本章节将详细介绍裁判表决器的电路设计与物理实现过程。

## 4.1 裁判表决器的电路设计

### 4.1.1 电路图绘制与原理分析

构建裁判表决器的第一步是绘制其电路图。电路图是数字电路设计中的蓝图,它详细展示了各个组件之间的连接关系。对于裁判表决器而言,电路图需要准确反映出表决逻辑的实现。

**电路图绘制步骤:**

1. 确定裁判表决器的功能需求和表决逻辑。

2. 选择合适的逻辑门来实现所需逻辑功能。

3. 使用电路设计软件绘制电路图,确保所有逻辑门正确连接。

**原理分析:**

- 使用与门(AND)来实现“同时满足多个条件”的逻辑。

- 使用或门(OR)来实现“满足任意条件”的逻辑。

- 使用非门(NOT)来实现“否定某条件”的逻辑。

电路图中通常包含以下元素:

- 电源和地线

- 逻辑门符号

- 连接线表示信号流向

- 输入输出标识

例如,一个三输入的裁判表决器电路图可能需要三个AND门,每个AND门连接三个输入信号,然后将这三个AND门的输出连接到一个最终的OR门上,以实现多数投票逻辑。

### 4.1.2 选择合适的逻辑门与组件

在构建裁判表决器时,选择合适的逻辑门和电子组件至关重要。这不仅影响到表决器的功能实现,还关系到电路的稳定性和成本。

**逻辑门选择:**

- 逻辑门的速度和类型应根据表决器的速度要求和逻辑功能来选择。

- 对于复杂逻辑设计,考虑使用可编程逻辑设备,如PLD、CPLD或FPGA。

**电子组件:**

- 电阻、电容等被动组件用于信号处理和电源滤波。

- 二极管、晶体管等主动组件可用于信号控制和驱动。

**参数说明:**

- 考虑到信号的稳定性,逻辑门的供电电压要与组件规范匹配。

- 温度系数、频率响应等参数应满足表决器的工作环境和性能要求。

## 4.2 裁判表决器的物理实现

物理实现是将电路设计转化为实际可工作的硬件系统。这一过程需要精密的搭建步骤,以及对电路的调试与故障排查。

### 4.2.1 硬件搭建步骤

硬件搭建主要包括组件的焊接、电路板的布局和组装等。

**组装步骤:**

1. 选择合适尺寸和布局的PCB板。

2. 在PCB板上焊接所有被动和主动组件。

3. 使用导线连接逻辑门芯片之间的引脚。

**焊接注意事项:**

- 使用适合的焊接工具和焊锡材料,保证焊点质量。

- 避免过度加热,以防损坏组件。

- 确保所有组件的极性正确无误。

### 4.2.2 电路调试与故障排查

电路搭建完毕后,需要进行调试和测试来确保裁判表决器的正确工作。

**调试步骤:**

1. 使用多用电表检查电源电压和地线连接是否正确。

2. 逐个检查逻辑门的输入输出是否符合预期。

3. 进行简单的输入测试,观察输出结果是否正确。

**故障排查:**

- 若表决器未按预期工作,首先检查电源和地线连接。

- 使用逻辑分析仪对信号进行监视,帮助确定故障点。

- 检查焊接点是否有虚焊、短路现象。

调试和故障排查是确保裁判表决器可靠性的关键步骤,需要耐心和细致的操作。

```

// 示例代码块,展示如何使用逻辑分析仪检测信号

// 注意:以下代码仅为示例,不代表实际操作步骤

void measureSignal(LogicAnalyzer *analyzer, int channel) {

analyzer->setChannel(channel);

analyzer->setTriggerLevel(1.5); // 设置触发阈值为1.5V

analyzer->setSampleRate(100e6); // 设置采样率为100MHz

while (1) {

analyzer->startAcquisition(); // 开始采集

// 等待触发信号

while (!analyzer->isTriggered());

// 循环读取数据并分析

while (analyzer->isAcquiring()) {

LogicSample sample = analyzer->readSample();

if (sample.state == LogicHigh) {

// 处理高电平逻辑

} else {

// 处理低电平逻辑

}

}

}

}

```

该代码块中的`measureSignal`函数能够控制逻辑分析仪开始采集信号,并设置触发阈值和采样率。此函数模拟了在调试过程中,如何连续读取数据并进行分析。

在本节中,我们讨论了裁判表决器的电路设计与物理实现,包括电路图的绘制、逻辑门和组件的选择、硬件搭建步骤以及电路调试与故障排查。通过这些详细的构建过程,我们能够理解如何将理论应用于实践,以实现一个可靠工作的裁判表决器。

# 5. 裁判表决器的测试与验证

在数字电路设计中,裁判表决器不仅要求逻辑设计的正确,还要求在真实应用场景下的稳定性和可靠性。测试和验证是确保裁判表决器满足设计规格的必要步骤。本章将介绍测试方案设计、性能评估、问题解决和改进措施。

## 5.1 测试方案的设计

在进行裁判表决器测试之前,设计一个全面的测试方案至关重要。测试用例应覆盖所有可能的输入组合,确保表决器在各种条件下都能正确工作。

### 5.1.1 测试用例的编写

测试用例应包括正常情况下的输入以及边界条件的测试。例如,对于一个三输入的裁判表决器,测试用例应该包括以下几种情况:

| 输入 A | 输入 B | 输入 C | 预期输出 |

|--------|--------|--------|----------|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

### 5.1.2 功能性测试与边界条件分析

功能性测试确保裁判表决器在正常工作范围内能给出正确的输出。边界条件分析则检验在极端情况下,如输入信号不稳定时,表决器的表现是否符合预期。

## 5.2 表决器性能的评估

性能评估是测试过程中的关键环节,它直接影响到裁判表决器的可靠性和用户信任度。

### 5.2.1 响应时间与准确性测试

响应时间是指从输入信号发生变化到表决器输出结果的时间间隔。准确性测试则用于验证表决器在长时间运行或大量测试用例中的正确率。

```bash

# 示例代码:计算响应时间和准确性

import time

# 假设我们有一个表决器函数 vote()

def vote(a, b, c):

# 表决器逻辑实现

pass

# 测试响应时间

start_time = time.time()

vote(1, 0, 1)

print(f"Response time: {time.time() - start_time}s")

# 测试准确性

total_tests = 100000

correct_answers = 0

for _ in range(total_tests):

a, b, c = random.randint(0, 1), random.randint(0, 1), random.randint(0, 1)

if vote(a, b, c) == expected_output(a, b, c):

correct_answers += 1

print(f"Accuracy: {correct_answers/total_tests * 100}%")

```

### 5.2.2 稳定性与可靠性评估

稳定性指的是裁判表决器在连续工作一段时间后,输出是否依然稳定。可靠性测试则是在不同的环境条件下,如温度、湿度变化,对表决器的影响。

## 5.3 问题解决与改进

在测试过程中发现的问题需要被详细记录并解决。这一节我们将讨论问题的常见解决方法及未来可能的改进方向。

### 5.3.1 遇到的问题及解决方法

假设在测试中发现表决器在高温环境下工作不稳定,可以通过散热设计的改进、使用耐高温材料或调整电路设计来解决。

### 5.3.2 改进措施和未来发展方向

除了修复现有问题外,还可以考虑采用更先进的技术如FPGA或ASIC来优化性能,或者增加自检功能来提高系统的可靠性。

通过以上几个方面的测试与验证,裁判表决器在交付使用前能确保达到较高的设计规格标准。本章介绍的测试流程和方法论,对于确保数字电路设计的质量同样适用。

0

0