FPGA上的游戏革命:【如何打造】推箱子游戏的系统级优化

发布时间: 2025-01-03 18:35:31 阅读量: 10 订阅数: 10

FPGA实现推箱子游戏.7z

# 摘要

随着FPGA技术的不断发展,其在游戏开发领域的应用逐渐成为技术革新的一部分。本文通过分析FPGA的基本组成和工作原理,探讨了推箱子游戏的系统设计与优化策略。文章详细讨论了硬件逻辑的优化方法,包括时序和资源的优化、并行处理和流水线技术的应用。在软件逻辑优化方面,本文重点介绍了代码级别的优化方法和存储资源的高效管理。此外,本文还关注了用户接口和交互体验的优化,以及系统级优化案例分析,并对未来FPGA技术在游戏行业的潜在应用进行了展望。

# 关键字

FPGA;游戏开发;硬件逻辑优化;软件逻辑优化;用户交互;系统性能评估

参考资源链接:[FPGA实现的推箱子游戏:探索硬件与交互设计](https://wenku.csdn.net/doc/6412b4bbbe7fbd1778d409fc?spm=1055.2635.3001.10343)

# 1. FPGA与游戏革命概述

FPGA(现场可编程门阵列)技术已经在众多领域获得广泛应用,但在游戏行业的应用尚处于起步阶段。随着游戏图形和物理处理需求的日益增长,FPGA以其并行处理能力和低延迟特性,被认为是推动游戏硬件革命的关键技术。

本章将首先介绍FPGA在游戏领域中的潜力,以及其如何在传统游戏开发流程中扮演更为重要的角色。接着,通过案例分析,揭示FPGA如何为游戏带来前所未有的性能提升,同时探索其在游戏行业的未来应用场景和发展趋势。

通过深入探讨FPGA技术在游戏中的应用,本章旨在为读者提供一个全面的FPGA与游戏革命概览,为后续章节中对推箱子游戏在FPGA上的设计、优化和用户交互改进等内容奠定基础。

# 2. 推箱子游戏的FPGA基础

### 2.1 FPGA的硬件架构与游戏开发

#### 2.1.1 FPGA的基本组成和工作原理

现场可编程门阵列(FPGA)是一种可以根据设计需求进行现场编程的集成电路。其内部包含成千上万个可配置的逻辑块(CLBs),这些逻辑块可以被编程以实现特定的逻辑功能。FPGA的主要优点在于它的可重配置性、并行处理能力和硬件加速潜力,这些特性使得FPGA非常适合用于游戏硬件加速。

FPGA的基本组成包括:

- **可配置逻辑块(CLBs)**:这是FPGA的最小处理单元,可以实现各种逻辑功能。

- **输入/输出块(IOBs)**:负责与FPGA外部的信号进行交互。

- **可编程互连**:连接CLBs和IOBs,构成逻辑电路。

- **嵌入式存储器和DSP模块**:用于数据存储和数字信号处理。

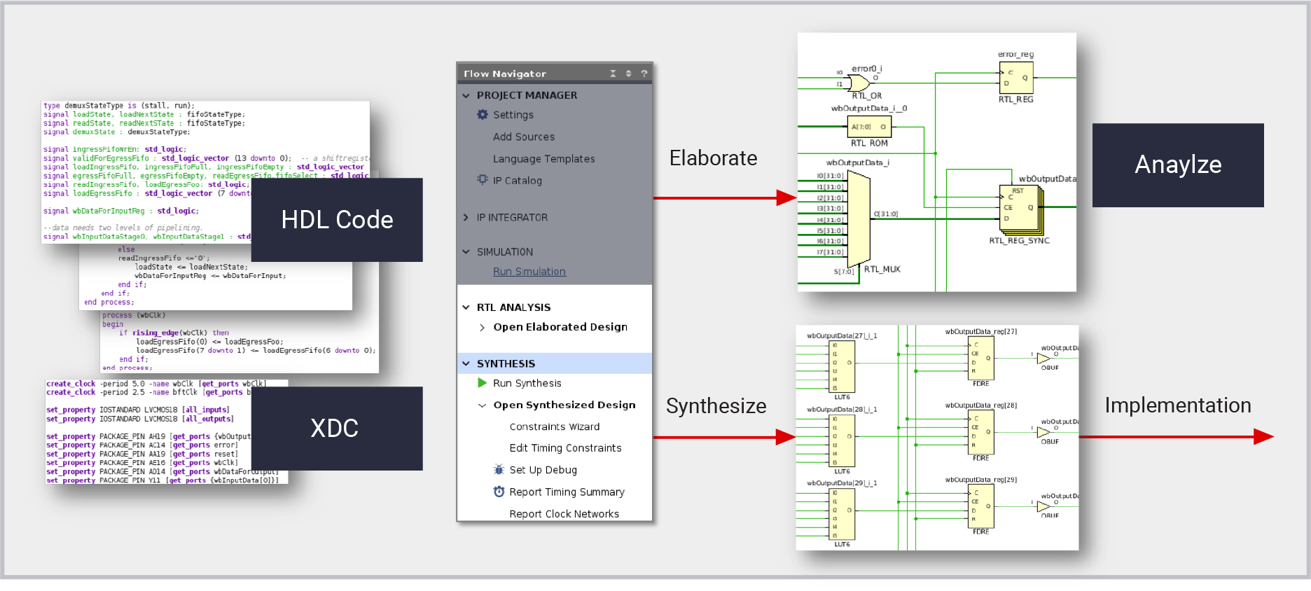

FPGA的工作原理是基于静态随机存取存储器(SRAM)或反熔丝技术来配置其逻辑块和互连。开发人员使用硬件描述语言(HDL),如VHDL或Verilog,编写代码来描述逻辑功能,然后通过综合和布局布线工具将其转换为FPGA的配置。

在游戏开发中,FPGA可以用来加速游戏的某些特定部分,比如图形渲染、物理计算或音频处理等。由于其并行处理的特性,FPGA能够同时处理大量的运算任务,从而大幅提高游戏性能。

#### 2.1.2 FPGA在游戏硬件加速中的应用

随着游戏图形和物理处理的复杂度不断增长,传统的中央处理单元(CPU)在某些情况下已经无法满足高性能需求。FPGA以其灵活的硬件架构和并行处理能力,成为游戏硬件加速的新选择。

在游戏硬件加速中的具体应用包括:

- **图形渲染**:通过自定义的图形处理单元(GPU)加速图形渲染过程,FPGA可以在硬件层面优化渲染算法,减少CPU的负担。

- **物理模拟**:FPGA可以通过并行处理能力实现复杂的物理模拟,提供更为逼真的物理效果。

- **音频处理**:利用FPGA进行音频信号的快速处理和3D音效生成。

使用FPGA进行游戏硬件加速的关键在于定制化。开发者可以根据游戏的需求,设计专门的硬件加速逻辑,从而达到最优的性能。然而,这需要开发者具备深厚的硬件知识和编程能力,才能有效利用FPGA的潜力。

### 2.2 推箱子游戏的系统设计

#### 2.2.1 游戏逻辑和规则的实现

推箱子游戏是一种经典的益智游戏,其基本规则是玩家需要将箱子推到指定的位置。游戏的挑战在于如何在有限的空间和数量限制下,合理安排移动策略。

游戏逻辑和规则的实现涉及以下几个方面:

- **地图设计**:定义游戏区域的大小和布局,确定玩家和箱子的初始位置以及目标点。

- **移动算法**:编写算法来处理玩家的输入,控制角色的移动,并在移动过程中检测碰撞。

- **游戏状态管理**:管理游戏的当前状态,例如计分、通关状态和撤销/重做的功能。

为了保证游戏逻辑的清晰和可维护性,可以采用模块化设计的方法。例如,可以将游戏分成几个主要模块,如用户输入模块、游戏逻辑模块和渲染模块,每个模块负责不同的功能。

```verilog

// 示例:FPGA上实现的推箱子游戏地图模块

module GameMap(

input clk,

input reset,

input [15:0] x_pos,

input [15:0] y_pos,

input direction,

output reg [15:0] box_x_pos,

output reg [15:0] box_y_pos,

output reg isCompleted

);

// 地图数据存储和逻辑处理逻辑(省略详细实现)

endmodule

```

在Verilog代码块中,`GameMap`模块负责管理游戏地图和箱子的位置。输入信号包括时钟信号`clk`、复位信号`reset`、玩家的位置坐标和移动方向。输出信号为箱子的位置坐标和游戏是否完成的标志`isCompleted`。

#### 2.2.2 系统级的框架搭建

系统级框架搭建是指如何将各个模块组合成一个完整的游戏系统,并确保各个部分能够高效协同工作。在FPGA上实现推箱子游戏,需要考虑硬件资源的分配、时序的安排和信号的同步等问题。

一个典型的系统级框架应包括以下几个方面:

- **主控制单元**:负责整个游戏的流程控制和状态转换。

- **数据通路设计**:确保数据能够在各个模块间正确传输。

- **时钟管理**:保证系统内部时钟同步,避免时序问题。

- **外围接口**:实现与外部设备(如按钮、LED显示器等)的接口。

```verilog

// 示例:主控制单元模块

module MainControlUnit(

input clk,

input reset,

input [3:0] playerInput,

output reg movePlayer,

output reg moveBox

);

// 控制逻辑实现(省略详细实现)

endmodule

```

在这个`MainControlUnit`模块中,主控制单元根据玩家的输入信号`playerInput`来决定游戏逻辑单元的行动,如是否移动玩家或箱子。`movePlayer`和`moveBox`是控制信号,用于通知游戏逻辑模块进行相应的动作。

构建系统级框架是一个复杂的过程,它需要开发者对整个游戏系统的运行机制有深入的理解。同时,合理的设计可以提高系统的整体性能和稳定性,为游戏提供流畅的用户体验。

# 3. 推箱子游戏的硬件逻辑优化

## 3.1 时序和资源的优化

### 3.1.1 时序约束与优化技巧

在FPGA开发中,时序约束是确保电路正确运作的关键。它们定义了信号的传播时间、时钟频率以及数据的接收时间。在推箱子游戏的硬件设计中,未能正确施加时序约束将导致数据传输失败、时钟偏斜甚至设备无法运行。

时序优化首先要确保FPGA中的时钟域能够同步。通过合理设置时钟约束,保证所有时钟网络中的信号能够在一个时钟周期内稳定传输,避免出现时钟偏斜问题。此外,工程师需要使用FPGA开发工具中的时序分析器来识别和解决时序违规问题。

对于FPGA设计,以下是一些时序优化技巧:

- **优化布局布线(Placement & Routing)**:FPGA工具提供的布局布线优化选项,可降低延迟和提高信号完整性。

- **使用同步电路设计**:尽量避免使用异步电路,因为异步电路通常难以满足严格的时序要求。

- **利用寄存器重定时(Register Retiming)**:这是一种自动调整寄存器位置以优化时序的方法。

- **路径分组**:将影响时序的路径分组,并对这些路径单独进行优化处理。

### 3.1.2 资源分配和复用策略

资源分配和复用策略对FPGA的性能和成本效益至关重要。FPGA资源有限,包括查找表(LUTs)、寄存器、DSP块等。有效的资源管理能够提高FPGA的资源利用率,降低成本,甚至可以在相同的硬件上实现更复杂的功能。

一种常见的资源复用技术是时分复用(TDM)。通过在不同的时间间隔使用相同的硬件资源来处理不同的数据流,可以在不增加硬件资源的情况下完成多个任务。

在推箱子游戏中,可以复用以下资源:

- **图形渲染单元**:渲染逻辑可以在不同的时间处理不同的屏幕区域或不同的图形元素。

- **控制器逻辑**:在控制器逻辑中,可以对输入的处理进行时间复用,以支持同时处理多个玩家的移动请求。

资源复用策略的实现可以有效降低FPGA的物理资源占用,并提高系统的整体性能。工程师需要精心设计并测试资源复用策略,以避免引入额外的时序问题。

## 3.2 并行处理和流水线技术

### 3.2.1 并行处理原理和应用

并行处理是利用多个处理单元同时进行运算的技术。在推箱子游戏中,许多游戏逻辑可以被分割为多个并行任务来执行,例如同时检查多个游戏区域的合法移动、更新多个游戏对象的状态等。

并行处理的主要原理包括:

- **任务分解**:将复杂的任务分解成可以并行执行的小任务。

- **同步机制**:确保并行任务之间的正确执行顺序和数据一致性。

- **负载平衡**:在多个处理单元之间合理分配任务,避免有的单元闲置而有的单元过载。

在FPGA实现并行处理时,设计师需要考虑数据流的管理,确保每个处理单元都能及时获得所需的数据并输出结果。同时,设计者应该注意避免过高的并行度导致的资源浪费。

### 3.2.2 流水线技术的实现和优化

流水线技术是一种常见的并行处理技术,它将处理过程分为若干个阶段,每个阶段在不同的硬件单元中顺序执行。这种技术可以显著提高处理速度,因为它允许每个阶段独立操作,而无需等待前一个阶段完成后才开始。

在推箱子游戏中实现流水线技术时,我们需要:

- **确定流水线的各个阶段**:例如,输入信号的处理、游戏逻辑的执行、图形的渲染等。

- **处理数据依赖性问题**:确保后续阶段的数据不会依赖于前一阶段的输出结果。

- **解决流水线的冲突和暂停问题**:例如,流水线的冒泡和数据前推技术用于解决冲突。

以下是一个简单的代码块示例,展示了如何在Verilog中实现一个基本的流水线结构:

```verilog

module pipeline_example(

input clk,

input reset,

// 输入信号

input [7:0] in_data,

// 输出信号

output reg [7:0] out_data

);

reg [7:0] stage1_data, stage2_data;

always @(posedge clk or posedge reset) begin

if (reset) begin

stage1_data <= 0;

stage2_data <= 0;

out_data <= 0;

end else begin

// 第一阶段处理

stage1_data <= in_data;

// 第二阶段处理

stage2_data <= stage1_data + 1;

// 最终输出结果

out_data <= stage2_data + 1;

end

end

endmodule

```

在流水线技术中,设计师通常需要仔细设计各级之间的数据流和控制流,确保数据的顺利传递和正确同步。此外,对于流水线的深度、宽度和级数,设计师需要根据实际的硬件资源和性能需求来进行权衡和优化。

优化流水线通常涉及以下方面:

- **优化各级流水线的处理时间**:确保各级之间的平衡,避免出现流水线的瓶颈。

- **处理数据冒险和控制冒险**:通过数据前推或延迟分支技术解决冒险问题。

- **提高流水线的吞吐率**:通过优化每个阶段的操作,减少不必要的等待周期。

# 4. 推箱子游戏的软件逻辑优化

在现代游戏设计中,软件逻辑的优化是提升性能和玩家体验的关键步骤。本章节重点介绍在FPGA上实现推箱子游戏的软件逻辑优化方法,包括代码级别的优化、资源访问与管理优化等方面,并结合案例进行分析。

## 4.1 代码级别的优化方法

### 4.1.1 高级语言在FPGA上的应用

FPGA领域常用的硬件描述语言(HDL)包括VHDL和Verilog。随着技术进步,高级语言如SystemVerilog和更接近传统编程语言的C/C++也开始在FPGA编程中扮演重要角色。高级语言带来更高级别的抽象,可读性更强,同时能在设计阶段发现潜在错误,提高了开发效率。

#### 示例代码块

```verilog

// Verilog 示例代码块

module game_processor (

input clk,

input reset,

// ... 其他输入输出信号

output reg [7:0] game_state // 游戏状态寄存器

);

always @(posedge clk or posedge reset) begin

if (reset) begin

game_state <= 0;

end else begin

// 游戏逻辑更新状态

// ...

end

end

// ... 其他游戏逻辑代码

endmodule

```

#### 参数说明

- `clk`: 时钟信号,用于同步硬件逻辑。

- `reset`: 复位信号,用于重置游戏状态。

- `game_state`: 寄存器,用于保存当前游戏状态。

#### 执行逻辑说明

在每个时钟上升沿,若复位信号为高,则重置游戏状态;否则执行游戏逻辑更新。

### 4.1.2 算法优化策略和实例分析

算法优化是提高软件性能的另一重要方面。通过减少不必要的计算和存储,以及优化数据结构和算法逻辑,可以有效提升效率。

#### 表格:算法优化策略比较

| 策略 | 描述 | 效果 |

| --- | --- | --- |

| 循环展开 | 减少循环开销,直接展开循环体 | 提高执行速度 |

| 查找表 | 使用预先计算好的表代替复杂计算 | 加快查找过程 |

| 分支预测 | 预测执行路径,减少分支开销 | 减少延迟 |

#### 代码块:分支预测优化示例

```c

// C 语言中的分支预测优化示例

int predict_branch(int a, int b) {

if (a > b) {

// 预测路径

return a * 2;

} else {

// 少走路径

return b * 2;

}

}

```

#### 执行逻辑说明

在上述代码中,编译器或程序员通过预测执行路径减少分支延迟。

## 4.2 资源访问与管理优化

### 4.2.1 存储资源的优化

存储资源是FPGA上宝贵的资源之一,优化存储使用不仅可以减少硬件资源的占用,还能提高运行速度。

#### 表格:存储资源优化策略

| 策略 | 描述 | 效果 |

| --- | --- | --- |

| 缓存技术 | 利用缓存减少对主存储器的访问次数 | 提高数据访问速度 |

| 存储器合并 | 合并相邻的内存访问请求 | 减少内存访问次数 |

| 数据复用 | 多次重用存储中的数据,而非重新读取 | 减少内存访问量 |

### 4.2.2 缓存机制和数据一致性

缓存机制对于提高访问速度至关重要,但也引入了数据一致性的问题。确保缓存数据与主存储器同步是系统设计时必须考虑的。

#### Mermaid流程图:缓存机制与数据一致性流程

```mermaid

graph LR

A[开始] --> B[CPU发出读请求]

B --> C{检查缓存命中?}

C -- 是 --> D[读取缓存数据]

C -- 否 --> E[检查缓存是否满了]

E -- 是 --> F[替换旧缓存数据]

E -- 否 --> G[将数据加载到缓存]

F --> D

G --> D

D --> H[更新缓存状态]

H --> I[结束]

```

在该流程图中,展示了CPU读取数据时缓存检查和数据加载的决策路径,以确保数据的一致性和及时更新。

### 总结

本章深入讨论了在FPGA上实现推箱子游戏的软件逻辑优化。通过高级语言的应用和算法优化,我们可以提高设计效率和运行性能。存储资源的优化和缓存机制的应用是保证游戏性能的关键,同时也需要注意数据一致性的维护。这些软件逻辑优化策略和具体案例分析,为游戏开发者在FPGA平台上的优化实践提供了参考。

# 5. 推箱子游戏的用户接口与交互优化

### 5.1 用户输入处理和反馈机制

推箱子游戏的用户体验很大程度上依赖于用户输入的处理效率和游戏状态的实时反馈。用户界面和输入处理不当不仅会导致玩家挫败感,还可能对游戏性能造成不必要的影响。为了确保游戏响应迅速且友好,我们需要关注以下几个方面:

#### 5.1.1 输入检测和去抖动处理

输入检测是指识别并响应用户的物理操作,如按键或触摸屏的点击。在FPGA上,输入检测必须实时发生,并且准确无误。去抖动处理是确保输入信号稳定性的关键步骤,尤其是针对机械开关等可能导致电信号波动的输入设备。以下是实现稳定输入处理的一个基本代码块示例及其解释:

```verilog

// Verilog代码块:去抖动模块

module debounce(

input clk, // 时钟信号

input rst_n, // 异步复位信号,低电平有效

input noisy_signal, // 带噪声的输入信号

output reg clean_signal // 去抖动后的输出信号

);

// 参数定义:计数器大小

parameter COUNTER_MAX = 25000; // 根据时钟频率和需要去抖动的时间确定

// 寄存器定义:用于计数和中间状态

reg [15:0] counter;

reg new_state;

// 去抖动逻辑

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

counter <= 0;

clean_signal <= 0;

new_state <= 0;

end else begin

if (noisy_signal != new_state) begin

counter <= counter + 1;

if (counter == COUNTER_MAX) begin

clean_signal <= new_state;

counter <= 0;

end

end else begin

counter <= 0;

clean_signal <= new_state;

end

new_state <= noisy_signal;

end

end

endmodule

```

该模块接收一个带噪声的信号`noisy_signal`,在`counter`达到设定值`COUNTER_MAX`之前,如果信号状态保持稳定,则将稳定的状态输出到`clean_signal`。这保证了即使输入信号有多次短暂的波动,输出信号也会保持稳定,从而去除了抖动。

#### 5.1.2 游戏状态的实时反馈

为了提供流畅的游戏体验,游戏状态的实时反馈至关重要。这意味着游戏需要以固定的帧率渲染每一帧画面,并且及时响应用户的输入。这通常涉及到精细的调度策略,以确保所有的渲染任务和用户输入都能得到及时处理。为了实现这一点,可以采用双缓冲技术,这样可以在不中断当前帧的显示的情况下,对下一帧进行处理。

### 5.2 高级用户界面技术

用户界面(UI)是游戏体验的重要组成部分。用户界面技术的目的是以直观、清晰的方式展示信息,同时提供流畅、便捷的操作体验。在FPGA平台上实现高级用户界面需要特别注意渲染效率和显示技术的运用。

#### 5.2.1 显示器接口和分辨率优化

为了实现高效的显示,FPGA需要能够支持各种显示器接口和分辨率。这不仅包括VGA、HDMI等常见的接口标准,还包括对不同分辨率的支持。实现这一目标的关键在于设计一个灵活的显示控制器,它能够根据显示设备的特性调整同步信号和分辨率。

```verilog

// Verilog代码块:显示控制器的简单实现

module display_controller(

input clk, // 时钟信号

input [1:0] resolution, // 分辨率选择信号

output reg hsync, // 水平同步信号

output reg vsync, // 垂直同步信号

output reg [7:0] r, // 红色信号

output reg [7:0] g, // 绿色信号

output reg [7:0] b // 蓝色信号

);

// 根据分辨率选择不同的同步参数和时序

always @(*) begin

case (resolution)

2'b00: begin // 640x480@60Hz

// 设置同步信号和颜色信号的参数

end

2'b01: begin // 800x600@60Hz

// 设置同步信号和颜色信号的参数

end

// 其他分辨率参数...

endcase

end

// 定义渲染逻辑...

endmodule

```

#### 5.2.2 用户体验和界面友好性改进

用户体验改进的目标是使操作直观、响应迅速,并且具有吸引力。在FPGA实现中,这通常涉及到定制的图形处理逻辑,比如抗锯齿、颜色校正、字体渲染等。此外,为了提高界面的友好性,可以利用状态机来管理UI状态,比如菜单导航、游戏暂停和恢复等。

```mermaid

graph LR

A[开始] --> B[主菜单]

B --> C[新游戏]

B --> D[加载游戏]

B --> E[设置]

C --> F[游戏进行中]

D --> F

E --> G[音效设置]

E --> H[分辨率设置]

E --> I[退出]

F --> J[游戏暂停]

F --> K[游戏结束]

J --> L[选项菜单]

J --> M[返回游戏]

L --> I

K --> I

```

上图展示了一个简化的状态机示例,它描述了用户如何通过菜单导航和游戏状态进行互动。每个状态都对应于用户界面的一个特定部分,而状态之间的转换则定义了用户操作如何影响界面。

在用户界面技术的应用中,还需要注意实时性能的优化,以避免不必要的延迟,从而保证游戏运行流畅。这可能涉及到优化渲染管道,减少图形和逻辑处理中的瓶颈,以及采用流水线技术和并行处理技术。

随着硬件技术的不断进步,未来的FPGA将拥有更多的资源和更高的处理能力,这将为开发者提供更广阔的空间去创造更加复杂、丰富和吸引人的用户界面和交互体验。

# 6. 推箱子游戏的综合系统级优化案例分析

在前文所述的章节中,我们已经深入探讨了推箱子游戏在FPGA上的硬件和软件逻辑优化。现在,我们将目光转向系统级的综合优化,这涉及对整个游戏系统性能的评估、瓶颈的分析,并且整合之前章节中提到的各项优化技术。此外,我们还将展望未来技术趋势,以及它们如何进一步革新推箱子游戏。

## 6.1 系统级优化策略的综合应用

### 6.1.1 系统性能评估和瓶颈分析

在进行系统级优化之前,首先需要对游戏的性能进行全面评估。评估的范围包括但不限于游戏运行速度、资源使用率、响应时间以及用户输入处理能力。通过这些评估,我们可以识别出游戏性能的瓶颈所在。

性能瓶颈可能来自多个方面,包括但不限于:

- **时序约束未满足**:如果游戏中存在时序违规,可能会导致游戏运行不稳定或速度下降。

- **资源过度使用**:资源使用达到上限,可能会导致系统无法正常运行或出现性能下降。

- **内存访问瓶颈**:不合理的内存访问模式,如随机访问大量数据,会显著影响系统性能。

为了分析这些瓶颈,我们可以使用FPGA开发工具中的性能分析工具,如Xilinx的Vivado,来查看系统资源使用情况,以及执行时序分析。

### 6.1.2 整合优化流程和案例展示

整合优化流程是一个系统化的过程,它要求开发者将前面章节中提到的硬件逻辑优化、软件逻辑优化以及用户接口优化技术综合应用。

以下是一个整合优化的案例:

1. **时序优化**:通过添加适当的时钟约束,并且使用逻辑重定时(retiming)技术,将关键路径上的寄存器优化,以此来满足时序要求。

2. **资源复用**:采用资源共享技术和模块化设计,减少硬件资源使用,尤其是在有限的FPGA资源下。

3. **软件逻辑优化**:重构算法代码,减少不必要的操作,并采用更有效的数据结构,比如使用查找表来优化算法。

4. **用户接口优化**:重新设计用户接口,提高显示器接口的分辨率,并采用流水线技术改善响应时间。

通过这些优化,我们可以看到系统运行效率的提升,用户体验的改善,并且减少系统故障的可能性。

## 6.2 未来趋势与技术展望

### 6.2.1 FPGA在游戏行业的潜在革新

FPGA作为一种能够提供高性能和快速开发周期的硬件平台,已经开始在游戏行业显示出其潜在的应用前景。随着半导体技术的持续进步,FPGA的性能和集成度将得到进一步的提升。未来,我们可能会看到:

- **实时渲染**:FPGA将能够提供更高质量的实时渲染能力,从而让游戏开发者有机会创造出更加丰富和真实的视觉体验。

- **AI辅助设计**:随着人工智能技术的发展,游戏开发流程中可能会越来越多地借助AI进行自动化的优化和决策。

### 6.2.2 新技术在推箱子游戏优化中的应用前景

除了FPGA本身的革新之外,一些新兴技术也将被应用在推箱子游戏的优化之中:

- **量子计算**:虽然目前还处于起步阶段,量子计算的计算能力理论上能够处理极其复杂的游戏算法,有可能成为未来游戏开发中的突破点。

- **边缘计算**:将游戏处理更靠近数据源,可以减少延迟并提高交互实时性,边缘计算将在未来的云游戏和分布式游戏场景中发挥重要作用。

通过这些新技术的应用,推箱子游戏将在未来的娱乐行业中保持其独特的位置,同时为玩家提供更加丰富的互动体验和更高的游戏质量。

0

0