VHDL入门:2选1多路选择器与组合电路设计

需积分: 9 120 浏览量

更新于2024-07-23

1

收藏 695KB PDF 举报

"EDA技术实用教程,专注于VHDL设计初步,通过介绍2选1、3选1多路选择器及半加器等基础电路的VHDL描述,讲解了VHDL的关键语法元素,包括实体声明、端口模式、数据类型、结构体表达、逻辑操作符、信号定义以及控制流语句等核心概念。"

在电子设计自动化(EDA)领域,VHDL是一种广泛使用的硬件描述语言,用于设计和验证数字系统的逻辑功能。本教程主要针对VHDL设计的初学者,通过实例逐步解析VHDL的基础知识。

首先,VHDL设计从实体(Entity)开始,它是描述硬件模块接口的蓝图,包括实体名、端口列表以及端口模式。端口模式包括IN(输入)、OUT(输出)、INOUT(双向)和BUFFER(缓冲),它们定义了信号的方向和用途。例如,2选1多路选择器的VHDL描述会包含输入信号、选择信号和输出信号的定义。

接下来,数据类型是VHDL中的关键元素,它决定了信号或变量可以携带的信息种类。标准逻辑位数据类型如STD_LOGIC用于表示单个比特的逻辑状态。同时,VHDL提供了结构体表达方式来组织和描述复杂的电路结构。

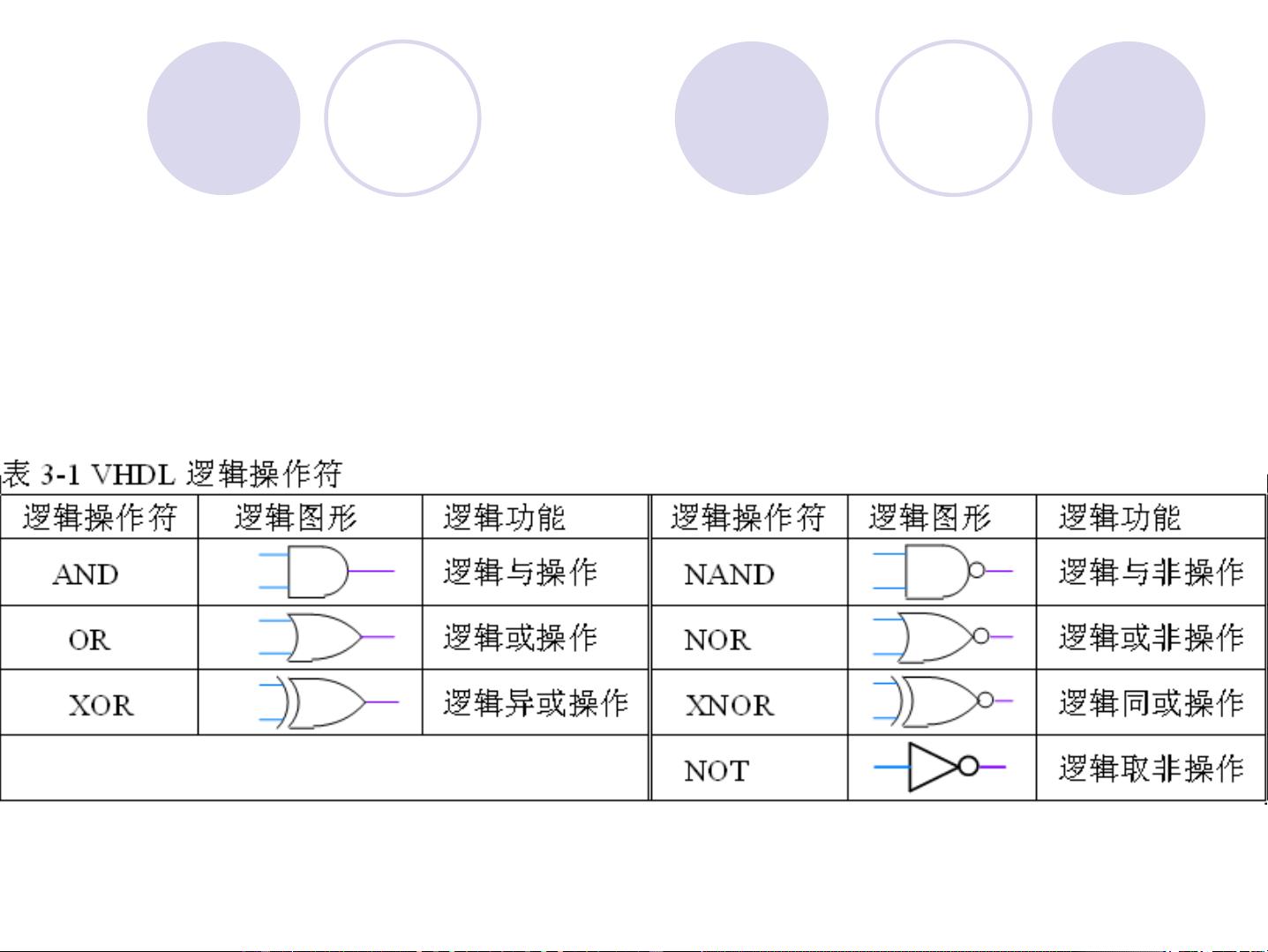

逻辑操作符,如AND、OR、NOT,用于构建布尔表达式,它们在组合逻辑电路的设计中不可或缺。例如,2选1多路选择器的VHDL描述会使用这些操作符来根据选择信号决定输出。

设计库和标准程序包,如IEEE库,提供了预定义的数据类型、函数和组件,简化了VHDL代码的编写。信号定义和数据对象则是存储和传递信息的核心部分,它们可以是变量或信号,分别代表瞬态和连续变化的状态。

控制流语句,如IF_THEN_ELSE和CASE语句,允许根据条件执行不同的逻辑路径。进程(PROCESS)语句则用于描述并行和顺序行为,常用于模拟时序电路的行为。

以半加器为例,VHDL描述将涵盖输入(两个进位和两个加数)和输出(和与进位)的定义,以及使用IF或CASE语句来计算结果。此外,标准逻辑矢量数据类型如STD_LOGIC_VECTOR可以用来表示多位的逻辑状态,适合描述多位算术运算。

本教程通过VHDL描述组合电路,如多路选择器和半加器,深入浅出地介绍了VHDL的基本语法和设计方法,为学习者提供了实践和理解VHDL的坚实基础。

2016-04-21 上传

2019-09-24 上传

2017-11-12 上传

2010-06-14 上传

2010-05-11 上传

2021-10-07 上传

2021-10-07 上传