ADP5134:高效电源时序控制策略与分立器件比较

62 浏览量

更新于2024-08-30

收藏 299KB PDF 举报

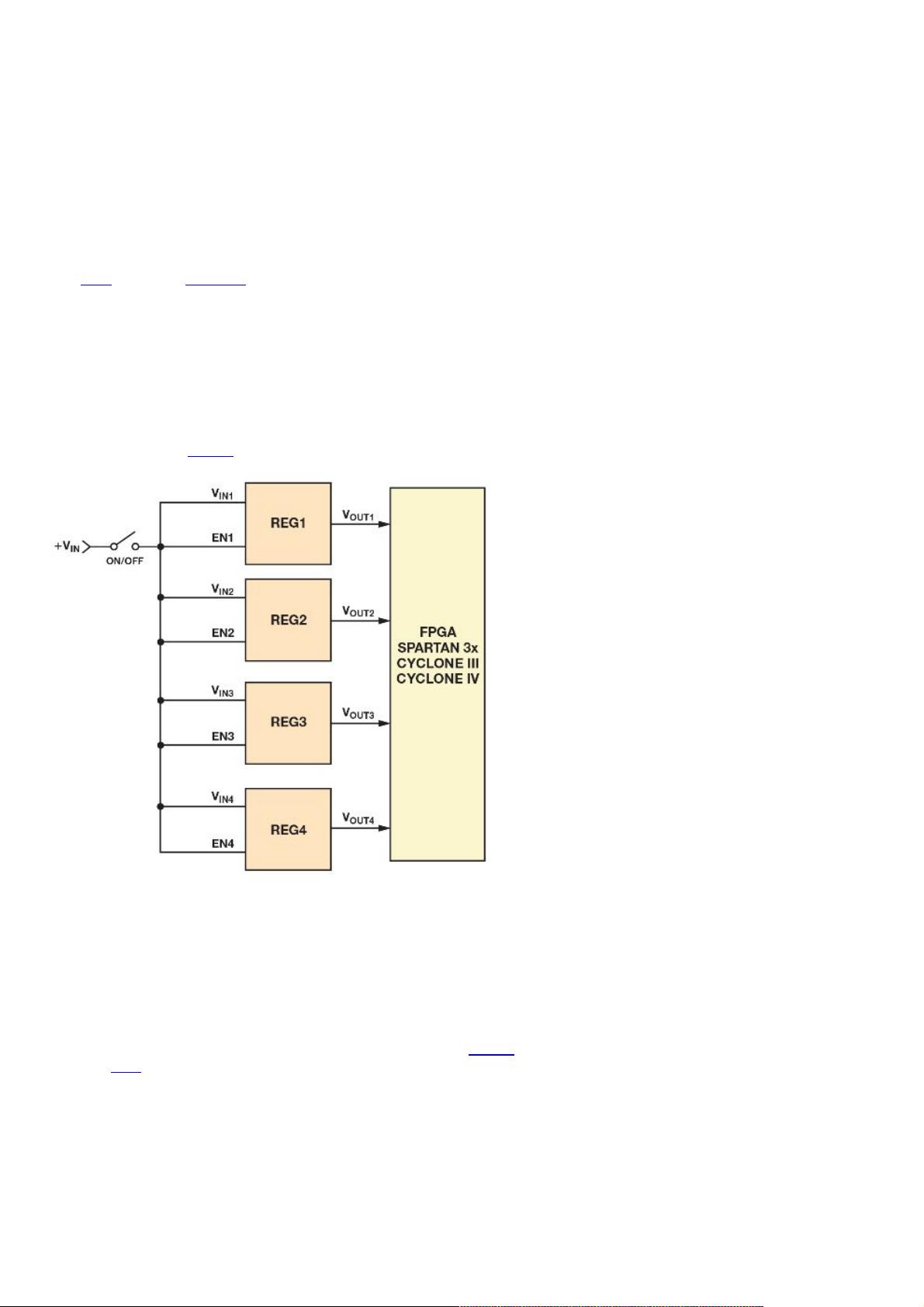

电源时序控制是现代电子设计中不可或缺的一部分,特别是对于微控制器、FPGA、DSP、ADC等高性能集成电路。这类设备通常需要多电压轨供电,确保内核、模拟模块、数字I/O等部分按照特定顺序上电,以防止因电源瞬间冲击(如闩锁效应和ESD)导致的硬件损坏。正确的时间安排至关重要,它可以避免设备启动时的浪涌电流,减少对供电系统的压力,尤其在使用限流电源时。

本文探讨了使用分立器件进行电源时序控制的优势和局限性。分立器件的优点包括灵活性高,可以根据具体设计需求调整上电顺序,但缺点可能包括复杂性增加、成本较高以及精确度受限于元件选择。作为替代方案,ADP5134这款集成解决方案被提出,它内置了两个1.2-A降压调节器和两个300-mA LDO,简化了设计过程,并且提供了内部精密使能引脚,使得实现时序控制更加简单且高效。

通过ADP5134,设计师可以利用无源延迟网络(如电阻、电容和二极管)来控制电源输入的延迟,这有助于控制各供电轨的激活时间,确保符合系统时序规范。例如,如Xilinx Spartan-3 AFPGA的实例,其内置的上电复位电路可以帮助管理电源上电顺序,但外部电路仍需遵循特定的电源时序要求,比如在配置器件之前先上电VCC_INT,再上电VCC_AUX,最后是VCCO。

对于那些对电源时序控制有更高精度和灵活性需求的应用,本文还推荐了一系列适合的集成电路,这些IC能够提供更为定制化的解决方案,以适应不同的设计环境和性能指标。

总结来说,复杂的电源时序控制不仅是提高设备稳定性和可靠性的重要手段,也是电子设计中必须考虑的工程实践。理解各种电源控制策略、器件特性以及如何结合实际应用案例,可以帮助工程师们制定出高效且安全的电源管理方案。

2015-10-12 上传

点击了解资源详情

2021-05-22 上传

点击了解资源详情

点击了解资源详情

2020-10-20 上传

2020-12-10 上传

2020-10-19 上传

2021-01-13 上传

weixin_38746738

- 粉丝: 4

- 资源: 931

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析