Xilinx FPGA原语详解与应用

需积分: 23 196 浏览量

更新于2024-07-22

收藏 548KB DOCX 举报

"Xilinx FPGA原语使用方法及分类详解"

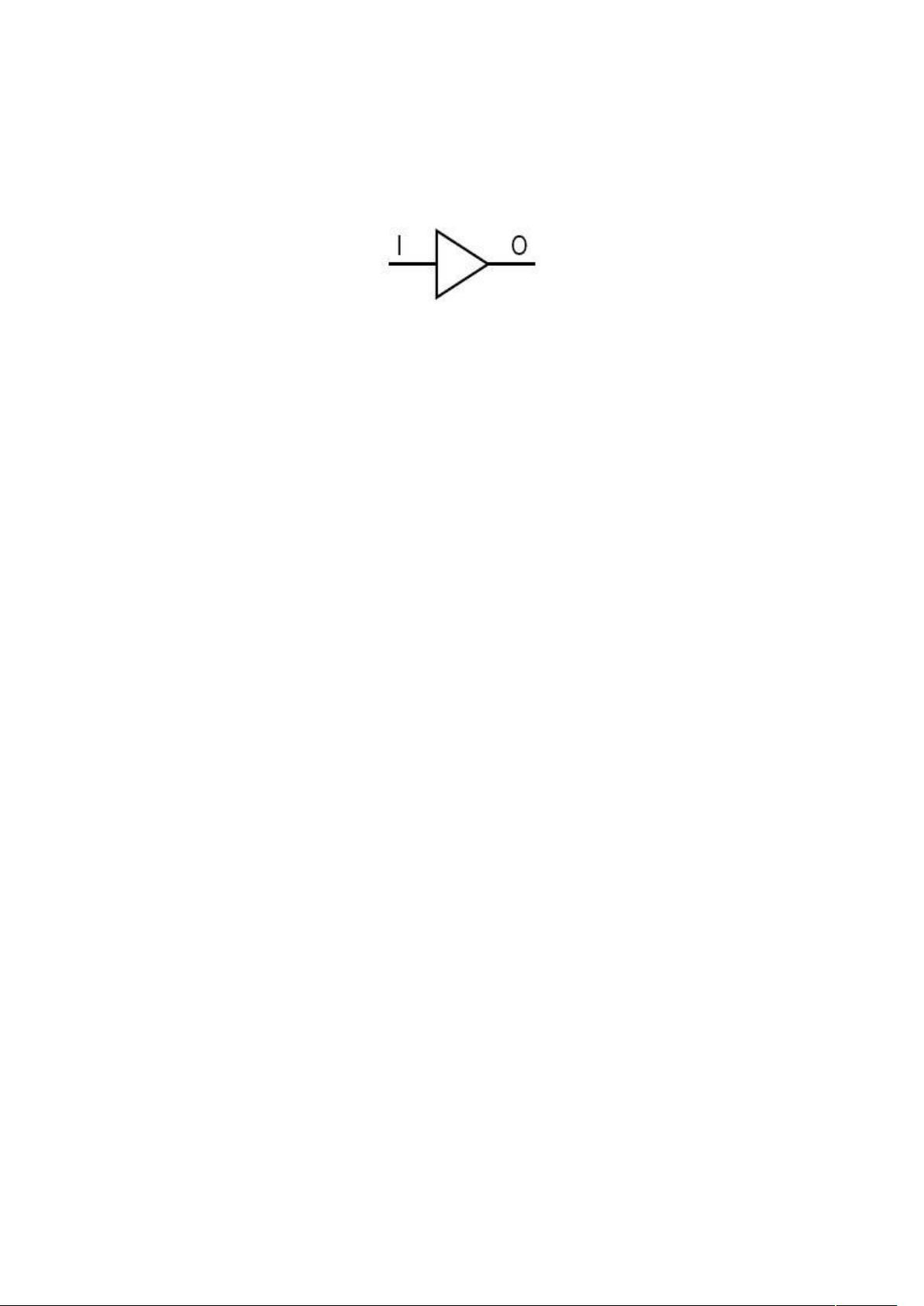

在FPGA设计中,Xilinx原语扮演着至关重要的角色,它们是构建FPGA逻辑电路的基础元件,类似于软件开发中的库函数或机器语言指令。原语是直接映射到硬件上的逻辑单元,包括查找表(LUT)、触发器、RAM等基本组件,确保设计能够被转化为实际的硬件实现。理解并熟练运用原语是高效利用Xilinx FPGA资源的关键。

Xilinx提供了丰富的原语库,覆盖了各种功能需求。例如,计算组件主要包含DSP48核,这是一个强大的硬件乘法器,用于实现高效的数字信号处理运算。DSP48核由一个18比特乘法器和一个48比特加法器组成,具有灵活的位宽配置和流水线能力,适用于滤波器等应用,能够提高系统性能并节省逻辑资源。

在Verilog HDL中,使用原语通常涉及直接例化,就像实例化一个普通模块一样。例如,实例化一个DSP48核的代码模板如下:

```verilog

module fpga_v4_dsp48(

BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN, CARRYINSEL, CEA, CEB,

CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE,

PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP, SUBTRACT);

output [17:0] BCOUT;

output [47:0] P, PCOUT;

// ...其他输入/输出端口定义

endmodule

```

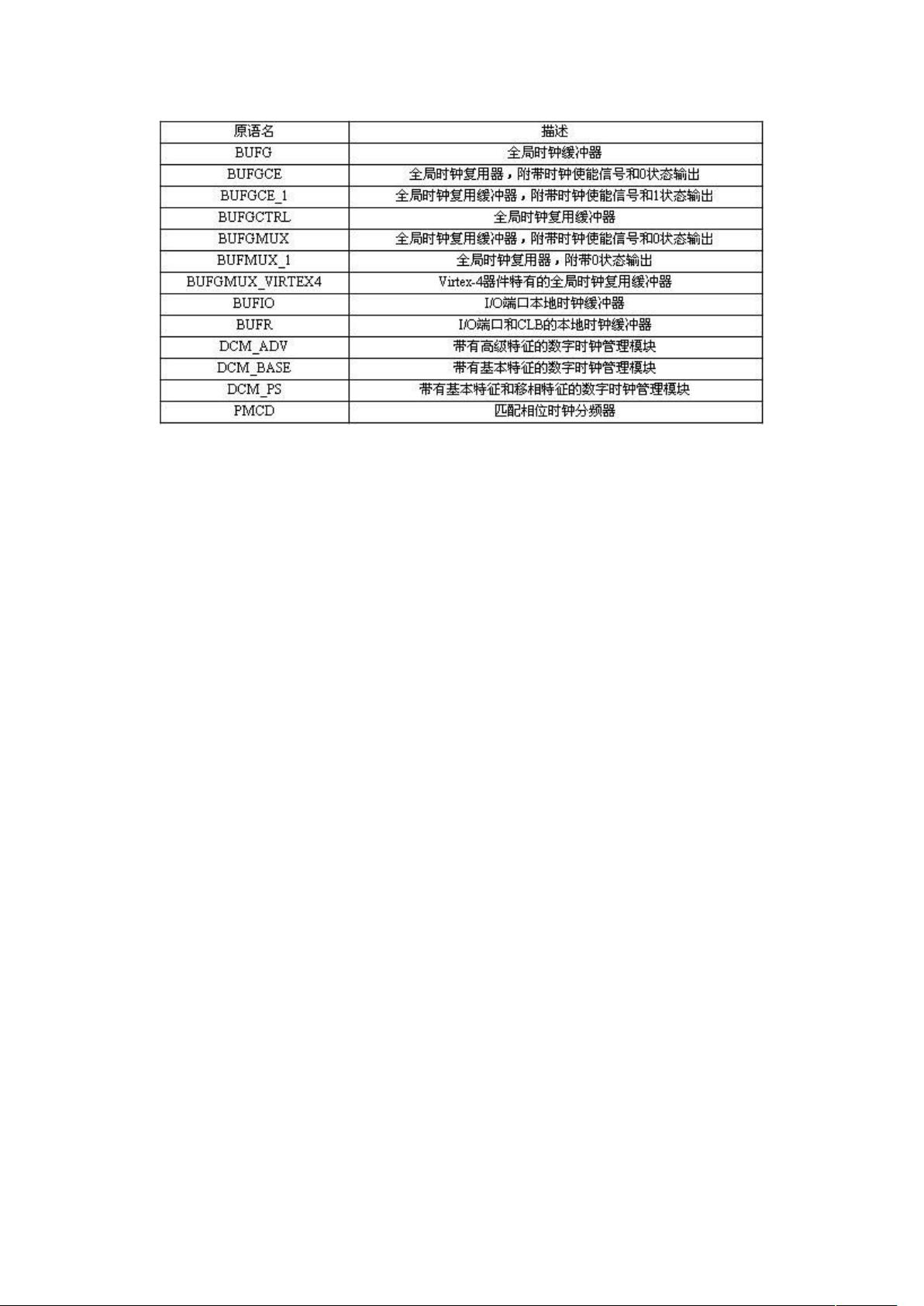

除了计算组件,原语还涵盖了I/O端口、寄存器和锁存器、时钟管理、处理器接口、移位寄存器、配置和检测组件、RAM/ROM存储器、Slice/CLB逻辑单元以及G比特收发器等类别。这些组件共同构成了FPGA设计的基础框架,满足从简单逻辑控制到复杂数字信号处理的各种需求。

I/O端口组件提供与外部世界交互的能力,如输入输出缓冲和驱动;寄存器和锁存器用于数据存储和时序控制;时钟组件则用于管理和同步系统时钟;处理器组件如PLIC(Platform Level Interrupt Controller)支持嵌入式处理器系统的中断管理。

移位寄存器在串行通信和数据处理中广泛使用;配置和检测组件帮助设置FPGA的初始化状态和运行时监控;RAM/ROM组件用于实现静态存储功能;Slice/CLB(Configurable Logic Block)组件是FPGA内部的基本逻辑构建块,通过它们可以构造任意复杂的逻辑功能。

最后,G比特收发器组件是高速通信接口的关键,如Xilinx的GTX/GTH收发器,能支持高速串行数据传输,适用于以太网、PCIe等高速接口标准。

每个原语都有特定的用途和适用场景,选择和使用原语时需考虑器件特性、性能需求以及功耗限制。设计者应根据具体项目的需求,结合Xilinx的器件手册和设计指南,恰当地选用和配置原语,以实现最优的FPGA设计方案。

2012-10-22 上传

135 浏览量

114 浏览量

点击了解资源详情

2023-08-23 上传

2023-05-18 上传

2023-08-22 上传

2016-05-19 上传

frq871231

- 粉丝: 0

- 资源: 3

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能