系统级Verilog的时钟域交叉设计与验证技术

需积分: 10 35 浏览量

更新于2024-07-19

收藏 1.73MB PDF 举报

"好学的CDC教程 - 使用SystemVerilog进行时钟域穿越设计与验证技术"

这篇教程主要探讨了在数字系统设计中至关重要的时钟域穿越(CDC)技术。时钟域穿越是指数据在不同时钟域之间传递的过程,这是多时钟系统设计中的核心挑战。作者Clifford E. Cummings通过Sunburst Design公司分享了自2001年以来的新技术和最佳实践,这些技术和方法用于解决单个信号和多个信号跨时钟域传输的问题。

1.0 引言

教程开头介绍了为什么时钟域穿越设计是关键,特别是在高速、高复杂度的数字系统中,确保数据在不同时钟域间准确无误地传输是系统可靠性的重要保证。

2.0 存储不稳定性(Metastability)

2.1 为什么存储不稳定性是个问题?

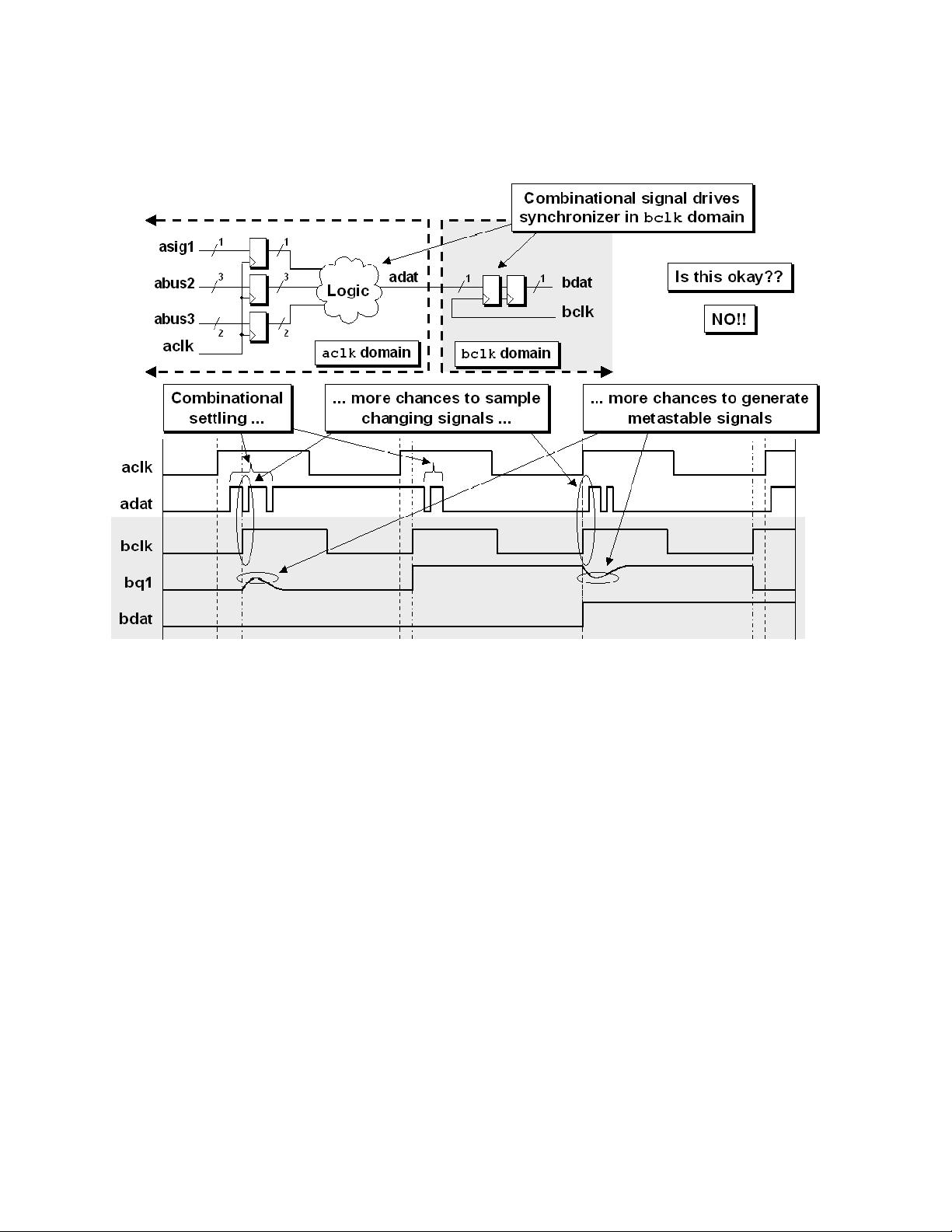

存储不稳定性是指在时钟边沿捕获数据时可能出现的一种短暂的不确定状态。这种状态可能导致逻辑错误,如果不正确处理,会严重影响系统的稳定性和可靠性。

3.0 同步器

3.1 两种同步场景

同步器是解决存储不稳定性问题的关键组件。文中详细讨论了两种常见的同步场景:数据的初次同步和多次同步,以确保数据在跨越时钟域后能稳定下来。

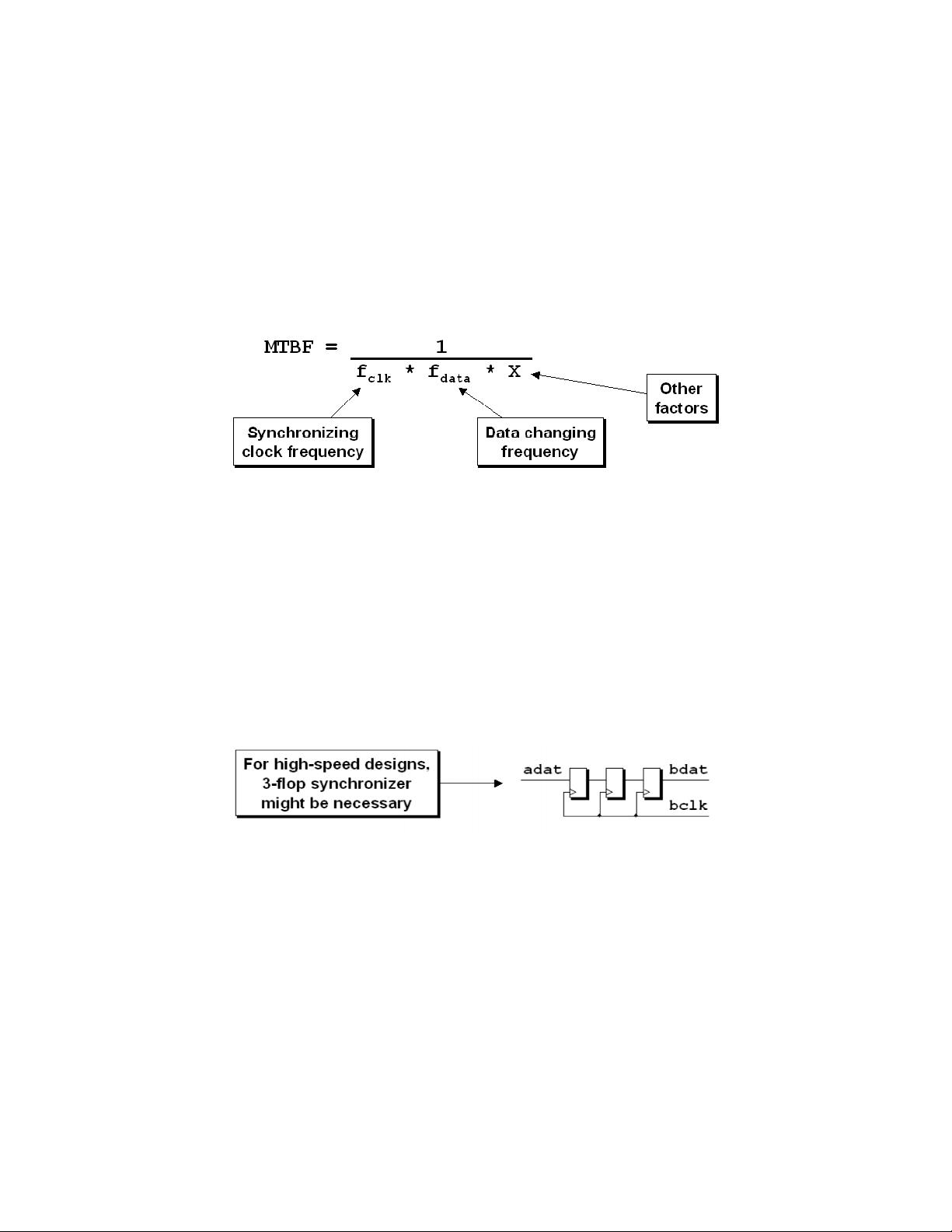

3.2 双级触发器同步器

双级触发器结构是最基本的同步器形式,通过两个独立的时钟域中的D触发器级联,增加了数据稳定的时间,从而降低存储不稳定性的影响。

4.0 CDC验证

该教程还涵盖了CDC验证的技术,这是确保设计正确性的必要步骤。使用SystemVerilog的高级特性,如断言和接口,可以构建强大的验证环境来检测潜在的CDC问题。

5.0 2深度FIFO设计

文中介绍了一个有趣的2深度FIFO设计,用于在不同时钟域之间传递多个控制信号。FIFO(先进先出)结构提供了一种有效的方法来缓冲数据,确保在不同时钟速率下也能正确处理。

6.0 SystemVerilog的应用

尽管所描述的设计方法可以用任何硬件描述语言实现,但教程中的示例特别使用了SystemVerilog的高效特性,这使得设计更加简洁和可维护。

7.0 结论

通过这个教程,读者将获得关于如何有效地处理时钟域穿越问题的深入理解,并能够利用SystemVerilog的强大功能来实现可靠的多时钟系统设计。

"好学的CDC教程"提供了关于时钟域穿越设计和验证的最新策略和最佳实践,对于任何从事多时钟系统设计的工程师来说都是宝贵的资源。通过深入探讨存储不稳定性、同步器设计以及高效的SystemVerilog实现,该教程有助于提升设计者在这一关键领域的专业技能。

2022-07-08 上传

2012-05-14 上传

2021-02-17 上传

2022-03-06 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_39508176

- 粉丝: 0

- 资源: 1

最新资源

- FtCookie:一个简单的幸运饼干

- 参考资料-2M.02.06.02 示例-流程目录.zip

- Application_Soiree:应用移动设备重新组合迷你面包机

- Gallery图片预览功能

- FipeRama:用于教育目的的Web应用程序,它使用api,jQuery,ajax和bootstrap从pepe表返回信息的api

- Accuinsight-1.0.2-py2.py3-none-any.whl.zip

- .net银行大厅自助信息系统asp毕业设计(源代码+论文).zip

- ChatCord:多人聊天

- Praktika

- 参考资料-2M.02.06.01 业务流程目录(客户业务).zip

- rajshree

- BERT用于分类毒性:只需要一个种族主义者的评论就能吸引在线讨论。 重点关注的是机器学习模型,该模型可以识别在线对话中的种族歧视,其中种族歧视被定义为任何粗鲁,不尊重或以其他方式可能使某人离开讨论的东西。 如果可以确定这些有毒的贡献,我们将拥有一个更安全,更协作的互联网。 我在这个个人项目中使用变压器,给每条推文一个毒性评分。 该数据集来自kaggle拼图多语言有毒评论分类挑战

- recap-project-frontend:我的后端项目“ ReCapProject”的前端

- 基于人脸识别考勤系统的设计与实现.zip

- 时分复用(TDM):这是TDM的代码-matlab开发

- sparql-utils:Scala SPARQL实用程序