Verilog HDL实现的PWM输出控制系统设计

"该文介绍了基于Verilog HDL设计PWM输出控制的方法,主要应用于电机控制和交流检测。通过Verilog HDL,可以实现更灵活和实时的PWM控制系统,相较于传统单片机控制,提高了设计弹性。设计中采用了ALTERA公司的MAX9000系列芯片,并在Quartus II开发平台上进行编程。"

PWM(Pulse Width Modulation)是一种常见的数字信号调制技术,用于通过调整脉冲宽度来模拟不同电压等级,常用于电机控制、电源管理、音频信号处理等领域。Verilog HDL是一种硬件描述语言,允许设计者用代码方式描述数字系统的逻辑功能,便于仿真、综合和实现硬件电路。

在基于Verilog HDL的PWM输出控制系统设计中,通常会涉及以下几个关键知识点:

1. **PWM生成原理**:PWM信号是通过开关元件(如晶体管或IGBT)的快速切换来生成的,通过调节脉冲的宽度,即高电平持续时间相对于总周期的比例,可以实现对平均电压的控制。

2. **Verilog HDL编程**:Verilog HDL允许设计者描述计数器、比较器、逻辑门等基本电路单元,以生成所需PWM波形。设计中,可能包括一个计数器来生成时钟周期,一个比较器将计数值与预设的占空比值进行比较,然后根据比较结果控制开关元件的状态。

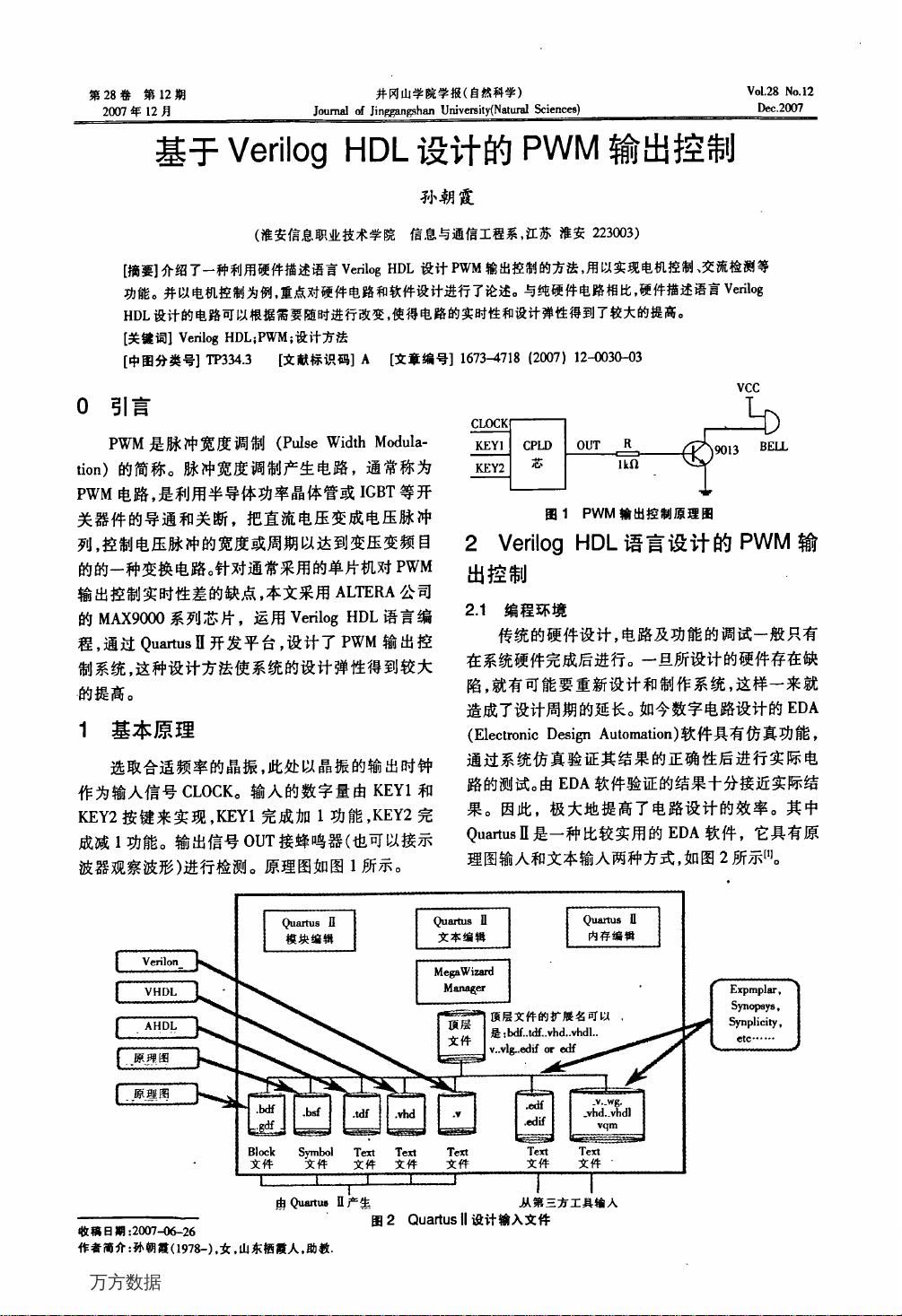

3. **MAX9000系列芯片**:ALTERA的MAX9000系列是 CPLD(复杂可编程逻辑器件)之一,提供了可编程逻辑资源,可以实现PWM控制器的硬件逻辑。在Verilog HDL设计完成后,可以通过Quartus II这样的EDA工具进行编译、仿真和下载到CPLD中。

4. **设计流程**:在Verilog HDL环境中,首先需要定义PWM生成模块,包括输入和输出接口,以及内部逻辑。接着,编写控制逻辑,如占空比调整、启动和停止信号等。然后,通过仿真验证设计的功能正确性。最后,综合代码并将设计配置到实际硬件上。

5. **实时性和设计弹性**:使用Verilog HDL设计的PWM控制器可以根据需求动态修改参数,如占空比和频率,而无需更改硬件,增强了系统的实时响应能力和设计灵活性。

6. **调试与测试**:在Verilog HDL设计中,可以通过软件仿真进行前期的错误检查和功能验证,降低了硬件原型制作的需求。此外,实际输出可以通过连接蜂鸣器或示波器等设备进行检测。

基于Verilog HDL的PWM输出控制提供了一种高效且灵活的设计方案,能够满足不同应用场景对PWM信号生成和控制的复杂需求。

2259 浏览量

106 浏览量

141 浏览量

2023-06-03 上传

2023-05-25 上传

107 浏览量

2023-05-18 上传

u012413444

- 粉丝: 0

- 资源: 1