电磁兼容设计关键:逻辑电路与接地策略

需积分: 11 75 浏览量

更新于2024-07-14

收藏 841KB PPT 举报

"这篇资源是关于电磁兼容设计的讲座,主要讨论了逻辑电路在电磁兼容设计中的应用和重要性。讲座涵盖了电磁兼容的基本定义、为何要考虑EMC、EMI和EMS试验、解决EMC的时间点以及相关的解决方案。此外,还详细讲解了接地、屏蔽和滤波等关键的EMC设计策略,并介绍了不同类型的接地方式,如单点接地和多点接地。"

正文:

在电子设计中,逻辑电路的使用必须考虑到电磁兼容(EMC)问题。高速逻辑电路可能产生大量的电磁干扰(EMI),对其他电子设备造成影响,因此,避免在不必要的地方使用高速逻辑电路是降低EMC问题的一个基本策略。此外,为了减小信号噪声,通常会在集成电路(IC)附近的电源和地之间加入旁路去耦电容,如104电容,以稳定电压并减少高频噪声。

电磁兼容(EMC)涉及三个方面:干扰源、敏感设备和传播途径。产品需符合国内外的技术标准和法规要求,如CISPR22和GB9254对于EMI试验的规定,以及GB/T17626系列对于EMS试验的要求,包括静电放电抗扰性、射频电磁场辐射抗扰性等多方面的测试。解决EMC问题应该尽早介入,最好在设计阶段就开始考虑,因为这样可以降低成本,提高产品的可靠性。

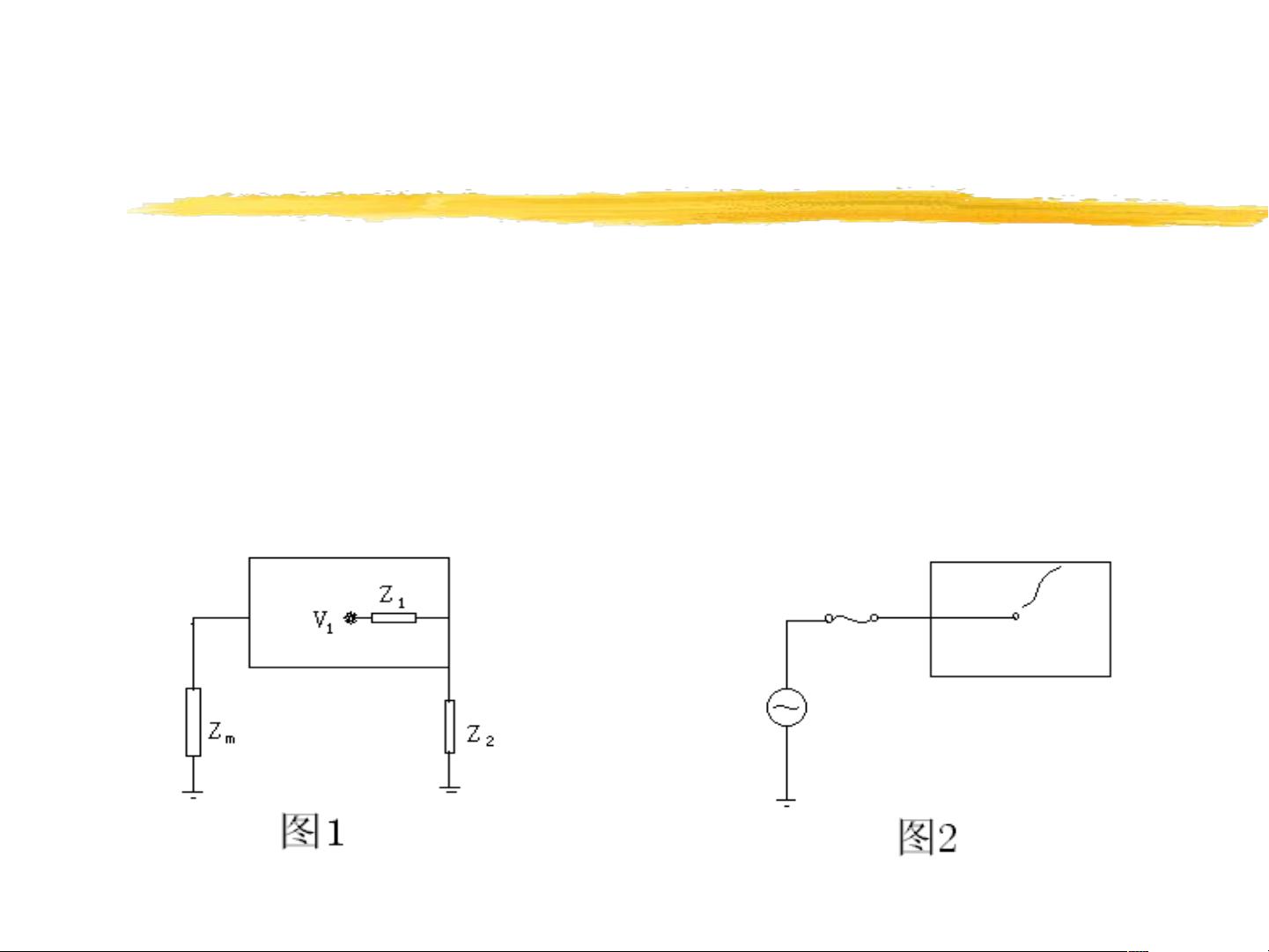

EMC设计包括接地、屏蔽和滤波等多个方面。接地是防止电击和消除干扰的重要手段,分为安全接地和信号接地。安全接地主要是将电气设备的外壳连接到大地,确保人员安全;而信号接地则为电路提供参考点,减少噪声干扰。接地方式有单点接地和多点接地,单点接地适用于低能量系统,而多点接地则适用于高频环境,以降低接地阻抗。

屏蔽是通过金属外壳或屏蔽层来阻止电磁能量的传播,减少干扰。滤波则是利用滤波器来抑制特定频段的噪声,改善信号质量。在内部设计,如印刷电路板(PCB)设计时,合理的布局和布线也是减少EMC问题的关键。

EMC设计通常分为三个阶段:问题解决阶段,规范设计阶段和分析预测阶段。在问题解决阶段,主要是针对已经出现的EMC问题进行调试;规范设计阶段则是在设计初期就遵循EMC标准,避免问题的发生;分析预测阶段则通过仿真工具提前预测并解决可能的EMC问题。

电磁兼容设计对于逻辑电路的使用至关重要,它涉及到产品性能、可靠性和市场准入等多个方面。通过深入理解EMC的基本概念和设计策略,工程师可以更有效地控制和优化电路中的电磁干扰,从而打造出高质量、符合标准的电子产品。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-10-11 上传

2011-11-27 上传

2023-04-21 上传

3548 浏览量

点击了解资源详情

点击了解资源详情

xxxibb

- 粉丝: 22

- 资源: 2万+

最新资源

- 驱动器:用于数据存储和传输的android应用

- wheather-kotlin-app:应用Kotlin博物馆

- cse427:uw的计算生物学课程

- bash入门学习实例

- spacedesk安装包

- RTSP拉流软件显示.zip

- ReCapProject:租车计划

- spooky-authors-identification:该存储库介绍了我们在哥伦比亚大学IEOR 4523数据分析课程的背景下实现的项目中的工作

- 在WPF MVVM应用程序中使用IValueConverter选择UserControl / View

- 一次性电子邮件域

- 教育核算点财务管理考核方案

- USIM_Explorer.rar

- ucsf_www.ucsf.edu_tests:www.ucsf.edu 重新设计的测试场景

- DummyWebApp

- C语言期末作业——民航票务系统

- 电信设备-基于改进蚁群AODV协议的多机器人通信组网方法.zip