Verilog实现的出租车计费系统设计

版权申诉

194 浏览量

更新于2024-07-10

收藏 612KB DOC 举报

"基于Verilog语言的出租车计费器设计文档"

这篇文档是关于使用Verilog语言设计出租车计费器的工程实践,涉及到电子设计自动化(EDA)技术的应用。Verilog是一种硬件描述语言(HDL),常用于数字电路和系统的建模与仿真。通过Verilog,设计者可以描述电路的行为和结构,然后利用EDA工具进行编译、综合、布局布线等步骤,最终生成可编程逻辑器件(如FPGA或ASIC)的具体配置。

设计要求包括:

1. 起步费设定:行程3公里内(含3公里)且等待时间2分钟内(含2分钟),费用为6.0元。

2. 计费规则:超出3公里的部分按每公里1.0元计费,等待时间超过2分钟的部分按每分钟1.0元计费。

3. 显示功能:需要显示行驶公里数、等待累计时间和总费用,所有显示的数值范围和分辨率都有明确限制。

工作原理部分描述了计费器的基本工作流程:

1. 开始服务时,计费器启动,里程计数器和时间计数器从零开始记录。

2. 费用计数器初始化为6元,表示起步费。

3. 随着车辆行驶,里程计数器增加,超出发车点3公里后,开始按照每公里1元累加费用。

4. 如果车辆等待,时间计数器也会增加,超过2分钟后,每分钟额外收取1元费用。

5. 最终,费用计数器会反映出行驶的总费用。

这个设计的灵活性在于,通过修改Verilog代码中的计费参数,可以适应不同地区的出租车计费标准。此外,如果将设计实例化并结合到实际硬件中,只需调整费用计算规则,即可广泛应用于各种出租车计费系统。

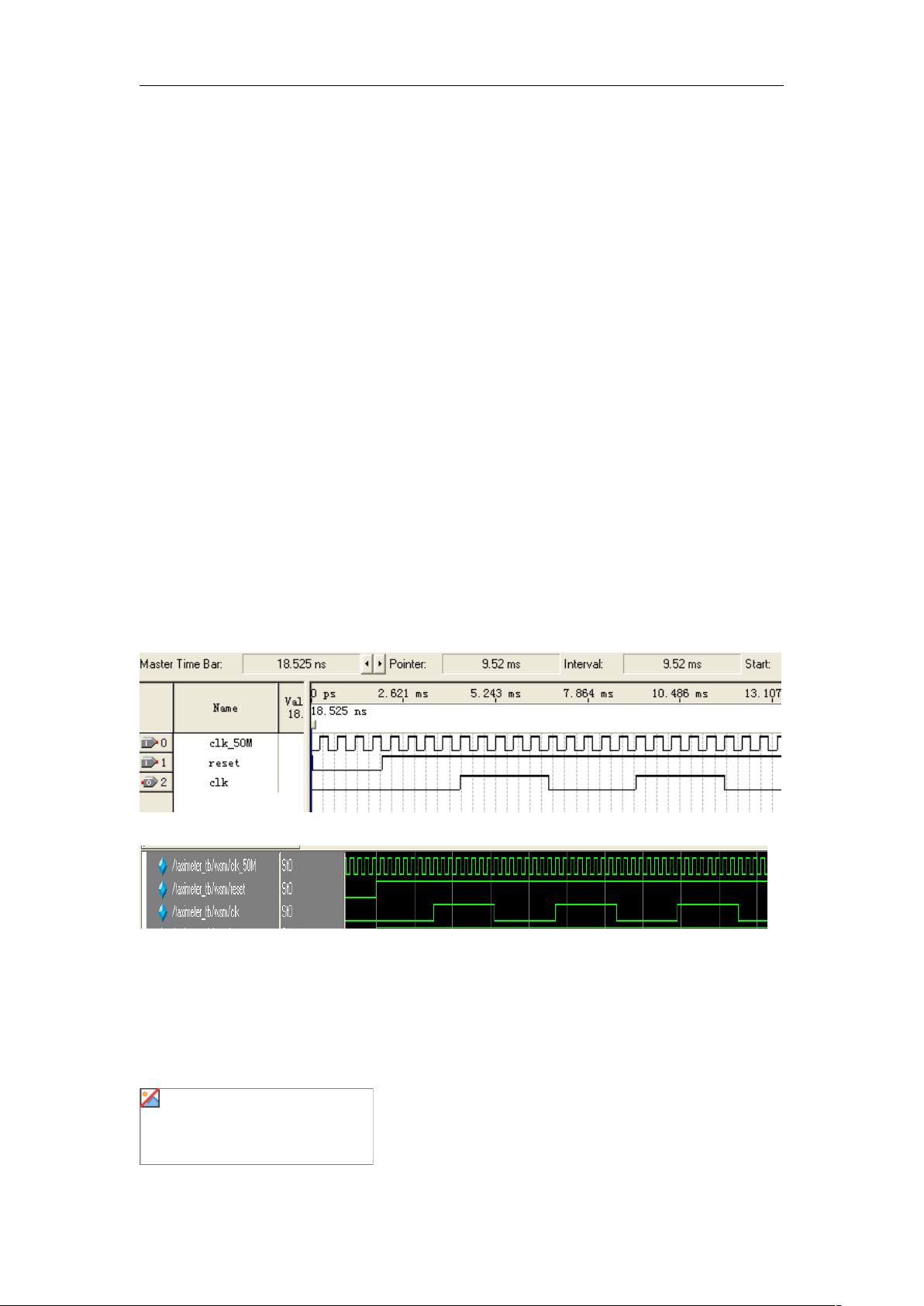

整个设计流程涉及到了ModelSim和Quartus这两个重要的EDA工具。ModelSim是一款常用的逻辑仿真软件,用于验证Verilog代码的功能是否正确;Quartus是Altera公司的综合和实现工具,能够将Verilog设计转化为适合特定 FPGA 的配置文件,进而实现硬件的编程。

通过这样的设计,不仅可以学习Verilog语言和EDA技术,还能理解电子系统如何根据特定规则处理实时数据,为电子工程领域的学习和实践提供了宝贵的实例。

346 浏览量

657 浏览量

2023-06-22 上传

132 浏览量

2024-11-11 上传

2024-11-11 上传

149 浏览量

2024-11-11 上传

2024-12-14 上传