JEDEC 260-pin DDR4 SDRAM SODIMM Annex K: R33 Design Specificatio...

版权申诉

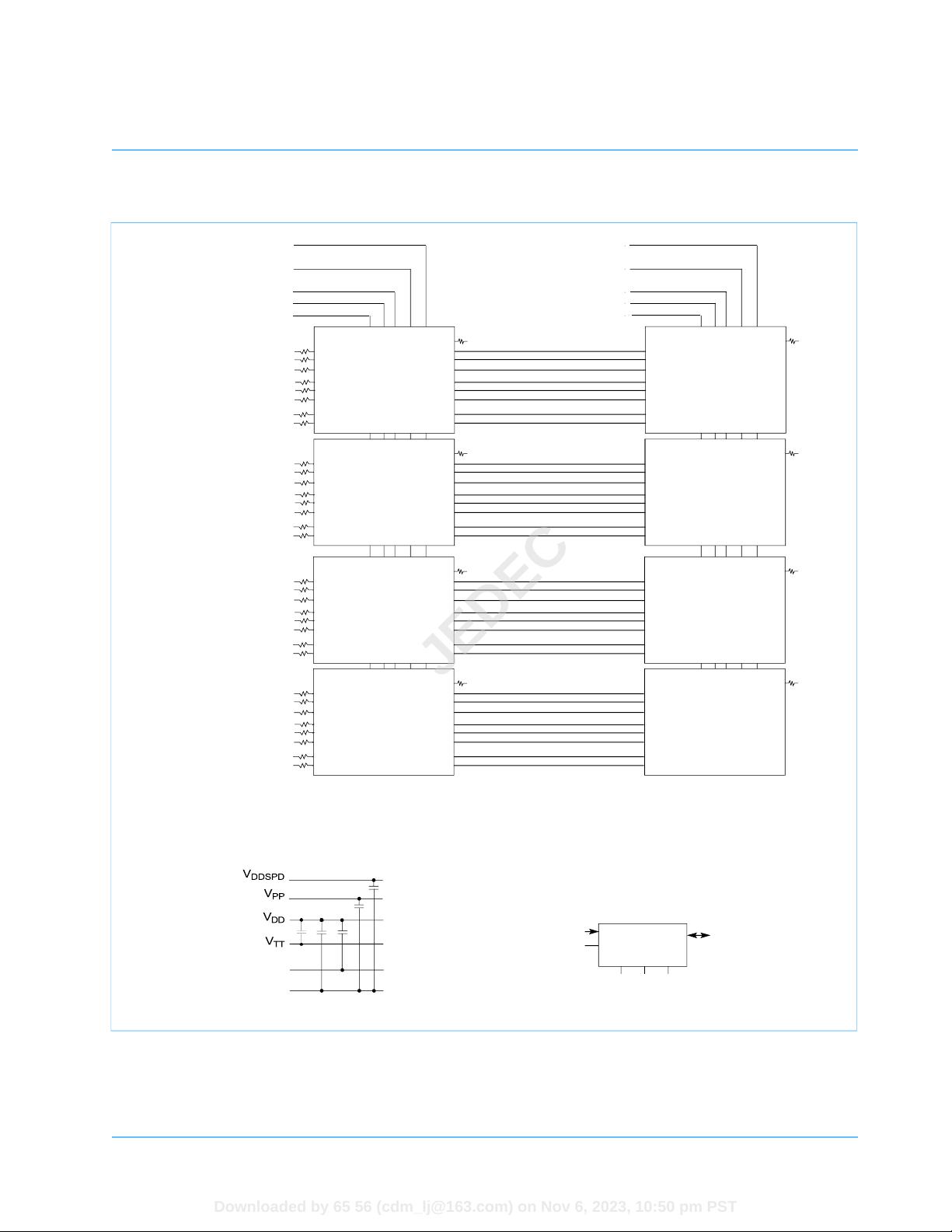

本文档是JEDEC标准21C(Release 33)的第4_20_25节,即DDR4 SDRAM Small Outline DIMM(SODIMM)设计规范的附件K,名为"Annex K - Raw Card K"。该附件关注于260-pin DDR4 SODIMM的设计,工作电压为1.2V(VDD),支持多种频率规格,包括PC4-1600、PC4-1866、PC4-2133、PC4-2400、PC4-2666和PC4-3200。

附件K提供了两个版本的Raw Card设计文件:K0和K1。K0版本对应于2018年4月3日的PC4-SODIMM_RC_K0_R100_V100.brd布局文件和2019年4月4日的PC4-SODIMM_RC_K0_R101_V100_BOM.xls物料清单。而K1版本在2023年1月30日更新,包含PC4-SODIMM_RC_K1_R200.brd布线图和相应的PC4-SODIMM_RC_K1_R200_BOM.xlsx物料清单。

设计规格详细说明了SDRAM的配置,包括每种容量(2GB, 4GB, 8GB, 16GB)对应的存储单元(die)数量、内存模块内的排数(ranks)、地址位数(#ofAddressbits)、行/列排列(row/col MO-310)、以及密度组织(Die Density Organization)。例如,2GB的SODIMM有256Mx64的存储单元,总共有8个这样的单元,分布在2个包装(package)中,每个包装内有14/10个排(ranks),地址位数为16,其中A16位与RAS_n信号进行复用。

SDRAM配置部分还提到,最高地址位(A16)的使用是基于它被与RAS_n信号进行多路复用。此外,文档指出,所有这些设计文件可能会随着技术更新和规范澄清而更新,但只会在必要时发布。最终的SODIMM规格会反映最新的设计文件,但也可能仅针对规格本身进行修订,不涉及设计文件的更新。

这个文档对于设计者和工程师来说是一个重要的参考,因为它提供了详细的DDR4 SODIMM物理实现和电气特性,以及所需设计文件和物料清单,确保了模块的兼容性和性能。理解这些参数对于开发和验证符合JEDEC标准的SODIMM产品至关重要。

2022-06-13 上传

2023-05-19 上传

2021-09-02 上传

2021-10-01 上传

2021-09-02 上传

2022-11-28 上传

2022-11-28 上传

点击了解资源详情

点击了解资源详情

RedCar

- 粉丝: 57

- 资源: 2027

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析