高速CMOS钟控比较器设计:提升性能与速度

90 浏览量

更新于2024-09-01

1

收藏 210KB PDF 举报

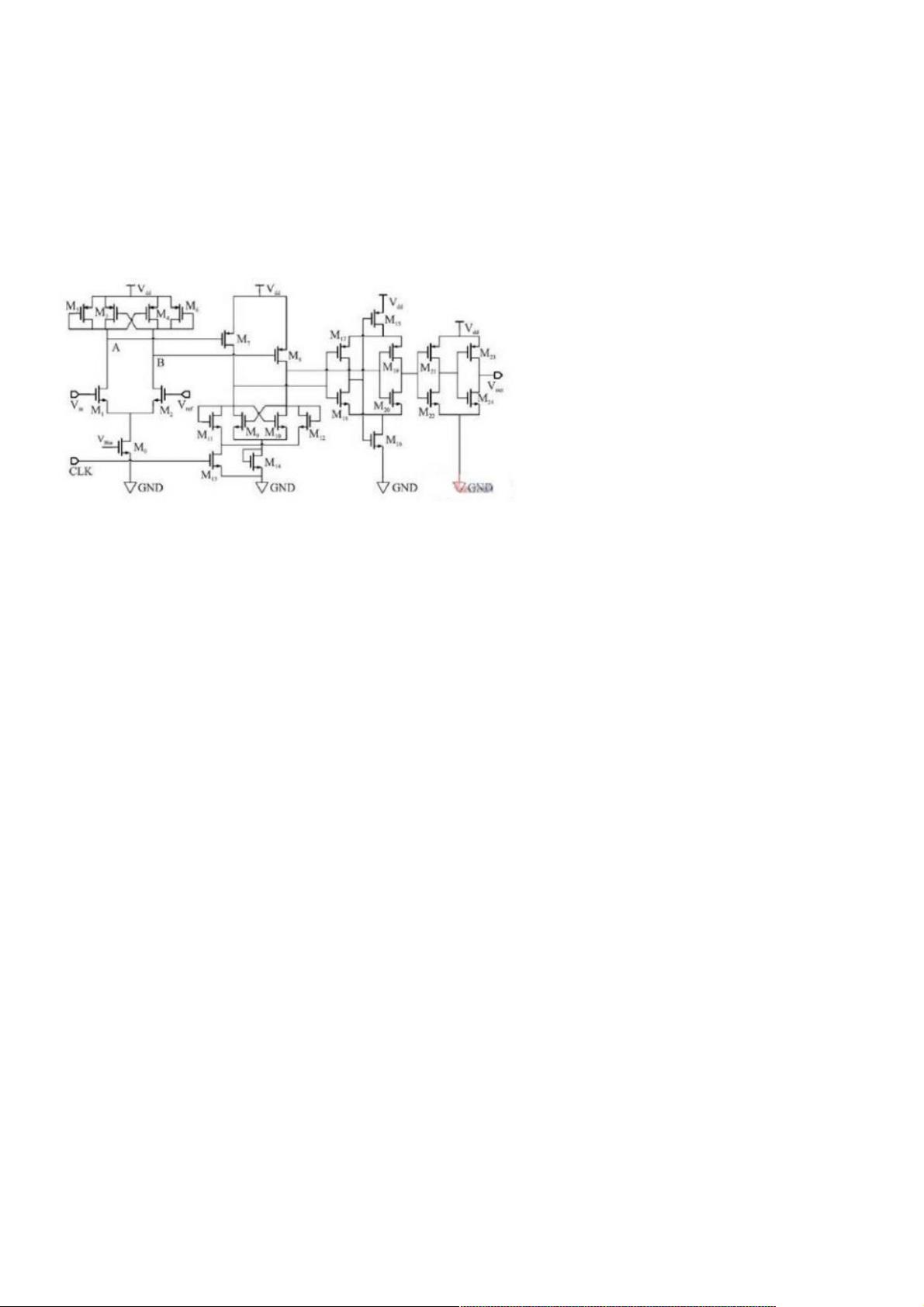

"本文主要介绍了高速CMOS钟控电压比较器的设计,包括预放大级、判断级和输出级的详细设计,以及如何利用时钟脉冲提高比较器的性能和速度。设计的比较器具有低输入失调电压和低踢回噪声,适用于高速Flash ADC电路。"

在高速CMOS集成电路中,电压比较器是至关重要的组件,尤其是在高速数据转换系统如Flash ADC(闪存型模数转换器)中。本文探讨的高速CMOS钟控电压比较器旨在提供更高的速度和精度,同时降低噪声影响。

首先,比较器的整体设计包含预放大级、判断级和输出级。预放大级的作用是放大输入信号,增强其敏感度,同时隔离输入信号与反馈噪声。通常,预放大级由多级放大器组成,以实现高带宽和增益。在本文中,预放大级由M1和M2组成的差分输入电路构成,这种结构能有效抑制共模噪声。M5和M6构成二极管连接的负载,而M3和M4则形成交叉耦合的负载,共同提升放大器的增益。第二级放大器由M7和M8组成,它们进一步增强信号。

接着,判断级是整个比较器的核心,负责实际的电压比较。本文采用了具有回滞效应的判断电路,这种电路结构利用正反馈实现快速比较,同时能抵抗噪声干扰。在时钟信号CLK的控制下,M9和M10的栅极交叉互联,形成正反馈。当CLK为高电平时,比较器工作,判断输入信号;而CLK为低电平时,比较器进入锁存状态,记录并保持上一时钟周期的比较结果。

最后,输出级将判断级的输出放大到数字逻辑电平,以便于系统其他部分处理。整个比较器的性能优化在于预放大级的噪声隔离、判断级的快速响应和时钟同步,以及输出级的逻辑转换。

低输入失调电压意味着比较器在不同输入电压下能保持较高的线性度,减少了由于制造工艺差异导致的误差。低踢回噪声则有助于减少电路内部反馈引起的不稳定性。这些特性使得设计的高速CMOS钟控电压比较器特别适合于需要高速转换和高精度的Flash ADC应用。

本文通过理论分析和仿真优化,提出了一种高效、高速的CMOS钟控电压比较器设计,其结构紧凑,性能优越,能够满足现代高速电子设备对数据转换速度和精度的需求。这一设计对于提升ADC的性能,特别是在高速信号处理领域,具有重要意义。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-01-20 上传

2020-11-04 上传

点击了解资源详情

2021-09-29 上传

2022-02-18 上传

点击了解资源详情

2024-12-02 上传

weixin_38602563

- 粉丝: 3

- 资源: 933

最新资源

- WordPress作为新闻管理面板的实现指南

- NPC_Generator:使用Ruby打造的游戏角色生成器

- MATLAB实现变邻域搜索算法源码解析

- 探索C++并行编程:使用INTEL TBB的项目实践

- 玫枫跟打器:网页版五笔打字工具,提升macOS打字效率

- 萨尔塔·阿萨尔·希塔斯:SATINDER项目解析

- 掌握变邻域搜索算法:MATLAB代码实践

- saaraansh: 简化法律文档,打破语言障碍的智能应用

- 探索牛角交友盲盒系统:PHP开源交友平台的新选择

- 探索Nullfactory-SSRSExtensions: 强化SQL Server报告服务

- Lotide:一套JavaScript实用工具库的深度解析

- 利用Aurelia 2脚手架搭建新项目的快速指南

- 变邻域搜索算法Matlab实现教程

- 实战指南:构建高效ES+Redis+MySQL架构解决方案

- GitHub Pages入门模板快速启动指南

- NeonClock遗产版:包名更迭与应用更新