10位高速高精度钟控电压比较器设计与仿真

175 浏览量

更新于2024-08-30

收藏 246KB PDF 举报

高速高精度钟控比较器的设计旨在提升10位A/D转换器的性能,特别是在速度和回馈噪声控制方面。该设计采用了前沿的技术策略来优化这些关键特性。

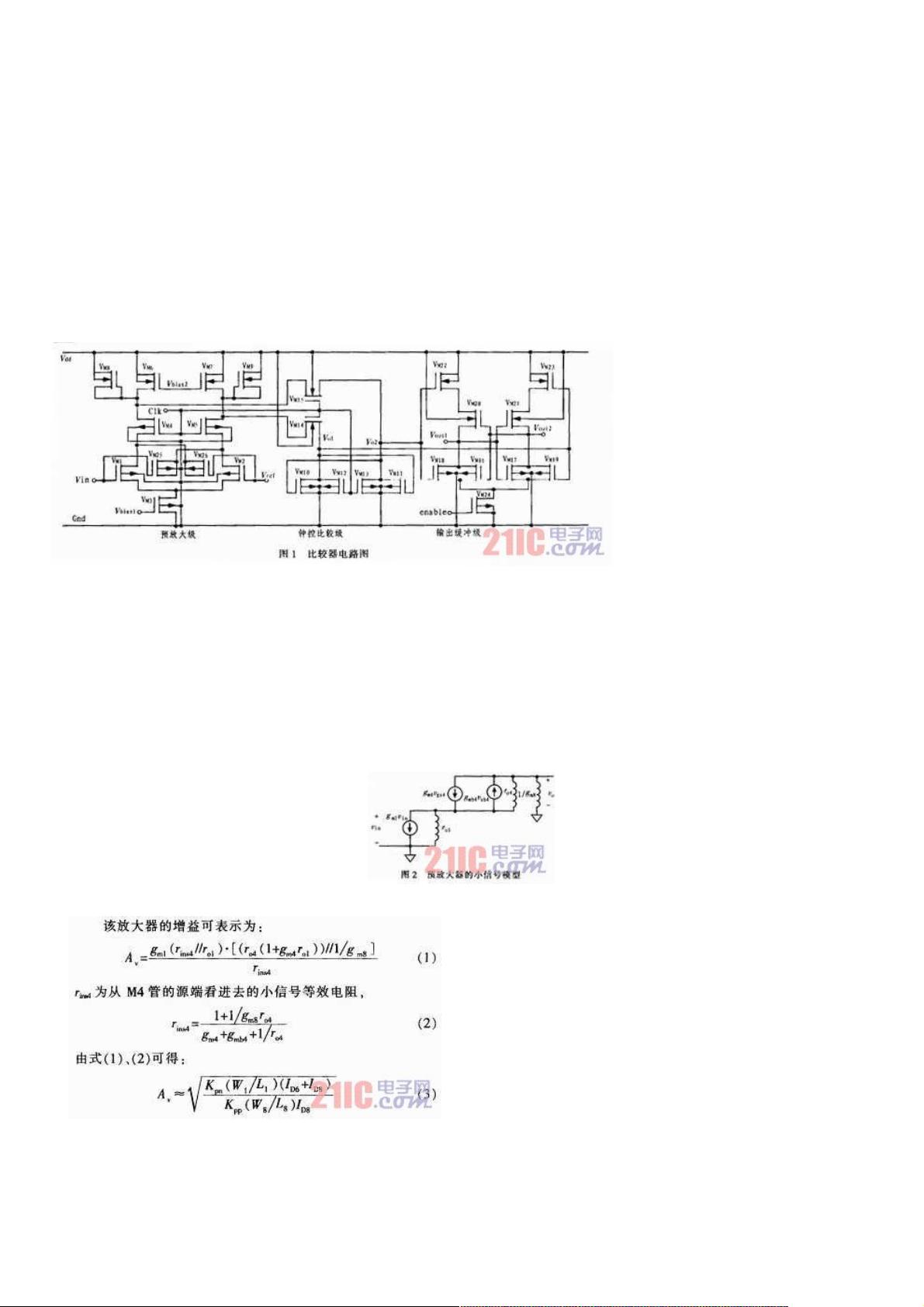

首先,前置预放大器结构是实现高比较精度的关键组件。预放大器采用差分放大器结构,其中VM1和VM2组成一个差分对,而VM8和VM9则是以二极管方式连接的MOS管,作为有源负载。通过引入PMOS镜像电流源VM6和VM7,输入晶体管的偏置电流得以部分由这些电流源提供,从而在不牺牲增益的情况下,通过调整管子的宽长比和注入电流,控制放大器的带宽和增益,确保了高速响应。

钟控开关晶体管VM4和VM5在时钟信号clk的不同状态下起作用:当clk为高电平时,它们构成共源共栅结构,增强电路对输入信号的放大能力;而在clk为低电平时,它们能够有效地隔离输入信号和再生节点之间的回馈噪声,这对于保持电路的稳定性和精度至关重要。预放大器的仿真结果显示,其增益达到18.352dB,-3dB带宽高达1.122GHz,满足了快速响应的需求。

接下来是钟控比较级,这是决定比较器速度的关键部分。它利用预放大器的输出信号来控制输入,通过两级正反馈环路结构的比较锁存器,显著提高了比较器的速度。这种设计允许快速地比较输入电压,从而实现高速转换。正反馈环路有助于加快响应时间,但同时也需要精细的平衡以防止不稳定。

在工艺上,该设计基于TSMC0.18μm CMOS标准工艺,这保证了电路的集成度和可靠性。通过Cadence Spectre模拟器进行仿真验证,验证了比较器在300MHz的工作频率下,最小可分辨电压(LSB)仅为±1mV,传输延时仅有360ps,且功耗低至2.6mW,确保了高精度和低能耗。

高速高精度钟控比较器的设计是为满足现代通信和信号处理系统对高性能A/D转换器的需求,尤其是在医学图像、高速数据变换和QAM调制器等领域。通过精心设计的预放大器和钟控比较级,以及严格的工艺选择和仿真验证,该电路在保证速度和精度的同时,实现了低回馈噪声,非常适合于高速高精度模数转换器和模拟IP核的开发。

808 浏览量

276 浏览量

276 浏览量

423 浏览量

276 浏览量

157 浏览量

421 浏览量

423 浏览量

327 浏览量

weixin_38624628

- 粉丝: 8

- 资源: 934

最新资源

- Phallanxpress:Phalanxpress允许您使用Wordpress作为后端来创建主干应用程序。 因此,您可以轻松创建单页wordpress。 它提供了一套完整的集合和模型,可以自动连接到您的wordpress安装

- 使用CORDIC算法的三角函数FPGA实现:使用CORDIC算法的三角函数在FPGA上实现。-matlab开发

- 烧瓶会议

- 冲突管理与沟通技巧

- LPC2300开发资料(原理图,例程代码)

- Catur:Bot Auto Chess.com

- Weather-Dashboard

- a8cas:用于存档 Atari 8 位磁带图像的便携式库和工具-开源

- priyamkhandelwal.github.io

- 电子功用-异步电机开环矢量控制方法和装置

- 个人职业生涯规划书

- python爬虫实验报告-3-类和对象的语法.ev4.rar

- VC6.0从开发activex ocx控件到发布到网上全过程

- Sweedly Webbyrå-crx插件

- DBS_Practice

- ShowCase:这是我的代码示例,用于展示我在c#中的编码经验