CPLD技术在嵌入式系统DRAM控制器设计中的应用

185 浏览量

更新于2024-08-30

收藏 211KB PDF 举报

"嵌入式系统/ARM技术中的基于嵌入式系统中DRAM控制器的CPLD解决方案,通过80C186XL的DRAM刷新控制单元,结合CPLD技术设计低成本、完整功能的DRAM控制器,使用VHDL语言进行编程实现。"

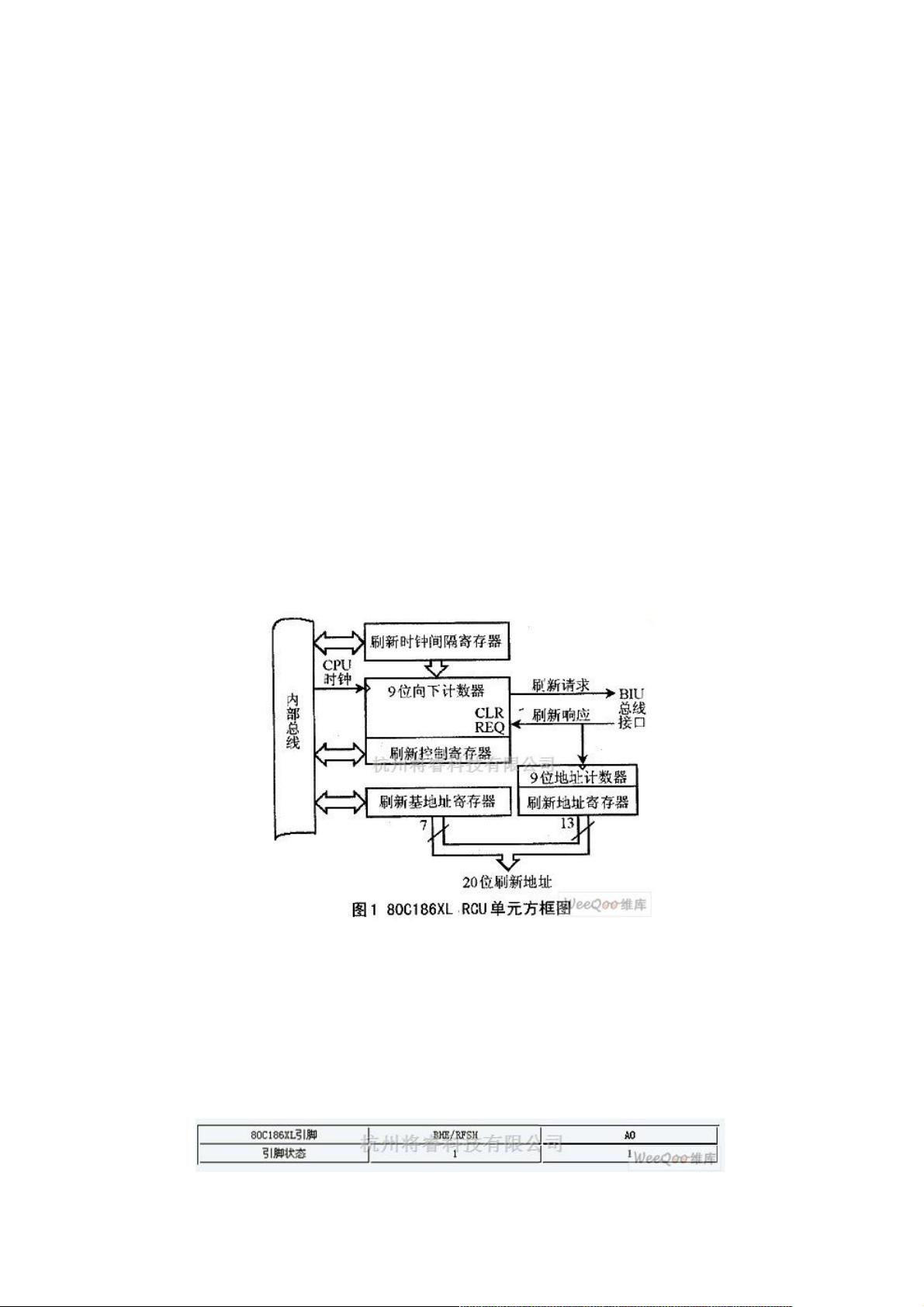

在嵌入式系统设计中,DRAM(动态随机存取存储器)由于其高容量和低成本的优势,常常被用作主要的内存组件。然而,DRAM的复杂时序管理是设计者面临的一大挑战。传统的80C186XL是一款16位嵌入式微处理器,由Intel公司制造,广泛应用于各种工业和通信领域。这款处理器内部集成了DRAM刷新控制单元(RCU),能够自动产生刷新总线周期,以保持DRAM中的数据有效性。

RCU单元的工作原理是在微处理器的增益模式下,通过编程设定,向总线接口单元(BIU)发送存储器读取请求。当设置好微处理器的存储器范围后,BIU在执行刷新周期时会选择相应的存储器区域。这种方法简化了对DRAM的访问,但也限制了其灵活性和功能。

为了克服这些限制并降低成本,本文提出了一个创新方案,即使用CPLD(复杂可编程逻辑器件)技术来设计一个独立的DRAM控制器。CPLD具有高度的灵活性和可编程性,能根据80C186XL的时序特性定制DRAM的控制逻辑。VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于编写CPLD的逻辑设计,以实现更复杂和精确的时序控制。

设计流程包括分析80C186XL的RCU单元提供的资源,如地址总线、控制信号和计数器结构,然后利用这些资源在CPLD中构建一个完整的DRAM控制器。控制器应包含地址生成、刷新控制、预充电和行/列地址解码等功能,确保DRAM的操作符合其特定的时序要求。

通过这种方式,嵌入式系统设计师可以利用CPLD和VHDL实现更高效、可靠的DRAM管理,同时降低系统设计的复杂性和成本。这样的解决方案特别适用于那些需要大容量内存且对成本敏感的嵌入式应用,例如工业控制系统、通信设备或数据处理终端。该方法提供了一种灵活且经济有效的途径,使得在嵌入式系统中使用DRAM变得更加可行和便捷。

2020-10-21 上传

2008-11-18 上传

2024-03-13 上传

2020-08-11 上传

2021-02-03 上传

2014-05-13 上传

2021-04-01 上传

120 浏览量

2023-03-04 上传

weixin_38656662

- 粉丝: 2

- 资源: 898

最新资源

- StarModAPI: StarMade 模组开发的Java API工具包

- PHP疫情上报管理系统开发与数据库实现详解

- 中秋节特献:明月祝福Flash动画素材

- Java GUI界面RPi-kee_Pilot:RPi-kee专用控制工具

- 电脑端APK信息提取工具APK Messenger功能介绍

- 探索矩阵连乘算法在C++中的应用

- Airflow教程:入门到工作流程创建

- MIP在Matlab中实现黑白图像处理的开源解决方案

- 图像切割感知分组框架:Matlab中的PG-framework实现

- 计算机科学中的经典算法与应用场景解析

- MiniZinc 编译器:高效解决离散优化问题

- MATLAB工具用于测量静态接触角的开源代码解析

- Python网络服务器项目合作指南

- 使用Matlab实现基础水族馆鱼类跟踪的代码解析

- vagga:基于Rust的用户空间容器化开发工具

- PPAP: 多语言支持的PHP邮政地址解析器项目