EDA技术在时序逻辑电路中的应用

需积分: 9 159 浏览量

更新于2024-07-31

收藏 429KB PPT 举报

"本资源主要探讨了EDA技术在时序逻辑电路设计中的应用,包括Latch锁存器(如RS锁存器和D锁存器)和触发器的相关知识,并提供了相应的VHDL代码示例。"

EDA技术,全称为电子设计自动化(Electronic Design Automation),是现代数字系统设计的核心工具之一,它涵盖了从概念设计到硬件实现的全过程。在本资源中,重点讲解了EDA技术在时序逻辑电路设计中的应用。

时序逻辑电路是数字电路的一种,其状态不仅取决于当前输入信号,还与之前的状态有关,常用于存储和处理数据。在4.2章节中,首先提到了Latch锁存器,这是一种简单的时序元件,用于保持数据。具体有两种常见的类型:RS锁存器和D锁存器。

1. RS锁存器:由两个非门交叉连接构成,其状态由输入S(Set)和R(Reset)决定。当R为低电平时,电路被置位(Set);当S为低电平时,电路被复位(Reset)。在VHDL代码中,展示了两种不同的实现方式:一种是数据流架构,另一种是行为架构。这两种架构分别展示了如何通过电平触发来控制Q和Qbar的输出。

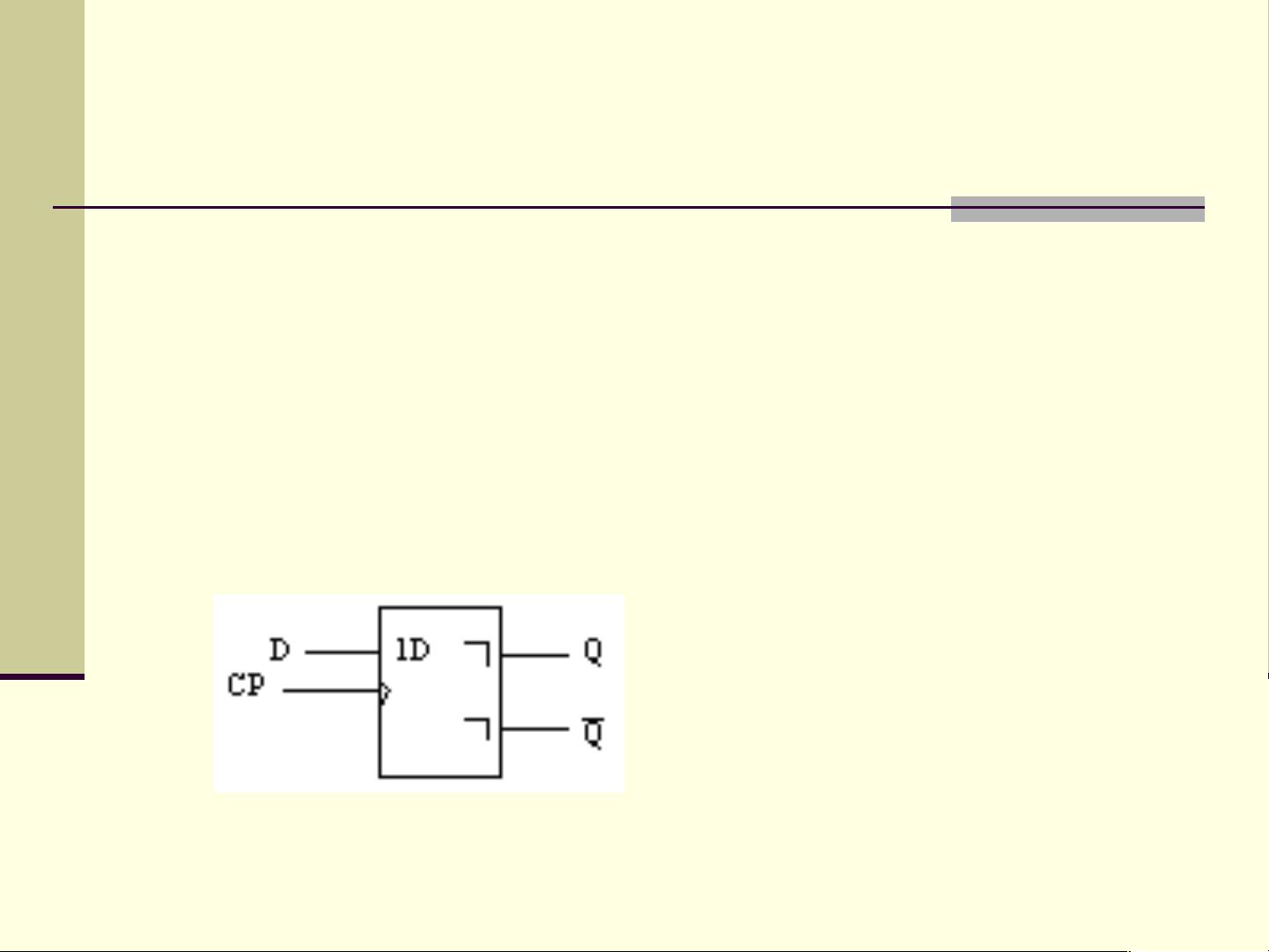

2. D锁存器:其名称中的"D"代表数据(Data),它在使能信号(Enable)为高时,将数据端(D)的值直接传递到输出端(Q)。VHDL代码中展示了D锁存器的实现,通过一个进程来处理使能信号和数据信号的交互,只有在使能信号为高时,数据才会被锁存。

4.2.2部分提到了触发器,它是时序逻辑电路的核心,具有边沿触发特性,比Latch更稳定且不易出现竞争-冒险现象。触发器通常有D触发器、JK触发器、T触发器和RS触发器等,它们能够存储一位二进制信息,并在特定的时钟边沿更新状态。

该资源深入浅出地介绍了EDA技术在设计时序逻辑电路中的应用,包括基本的锁存器和触发器的原理以及VHDL实现,对于理解数字系统设计和学习EDA技术具有很高的参考价值。

122 浏览量

568 浏览量

1047 浏览量

195 浏览量

150 浏览量

193 浏览量

116 浏览量

192 浏览量

503 浏览量

wuyulin0528

- 粉丝: 0

- 资源: 2

最新资源

- CI--EA实施

- 24L01模块原理图+PCB两种天线三块板子

- Horiseon-proyect

- SimbirSoft

- 钟摆模型:用于不同实验的 Simulink 模型-matlab开发

- shopcart.me

- 6ES7214-1AG40-0XB0_V04.04.00.zip

- hivexmlserde jar包与配套数据.rar

- KeepLayout:使自动布局更易于编码

- worldAtlas

- AdvancedPython2BA-Labo1

- lsqmultinonlin:共享参数的全局参数非线性回归-matlab开发

- STK3311-WV Preliminary Datasheet v0.9.rar

- js实现二级菜单.zip

- 微店助理 千鱼微店助理 v1.0

- tao-of-rust-codes:作者的回购