使用quartusII设计时序逻辑电路——模60计数器

需积分: 9 88 浏览量

更新于2024-08-01

收藏 465KB PPT 举报

该资源是一个关于使用Quartus II软件设计时序逻辑电路的PPT,特别关注如何通过图形编辑器设计模60计数器,这个计数器由两个模10计数器通过同步置0法连接。讲解了74160同步10进制计数器的功能和状态转换,并提供了两种构建六进制计数器的方法。

在电子设计自动化(EDA)领域,Quartus II是一款由Altera公司(现已被Intel收购)开发的流行的FPGA(Field-Programmable Gate Array)设计软件。它提供了全面的工具集,包括逻辑综合、布局布线、仿真、时序分析等,用于数字电路的设计、实现和测试。

时序逻辑电路是数字电路中的核心组成部分,它们不仅包含组合逻辑,还具有存储状态的能力。在Quartus II中,设计时序逻辑电路通常涉及以下几个步骤:

1. **项目创建**:首先,需要在Quartus II中创建一个新的工程,指定工程名称和保存位置,例如在示例中创建了名为`counter60`的项目。

2. **图形输入**:使用Quartus II的原理图编辑器,可以将所需的逻辑元件从库中拖放到设计区域。在本例中,为了构建模60计数器,使用了两个74160同步10进制计数器。74160元件具有使能端(ENT、ENP),同步置数端(LDN),异步清零端(CLRN)以及进位输出(RCO)等功能。

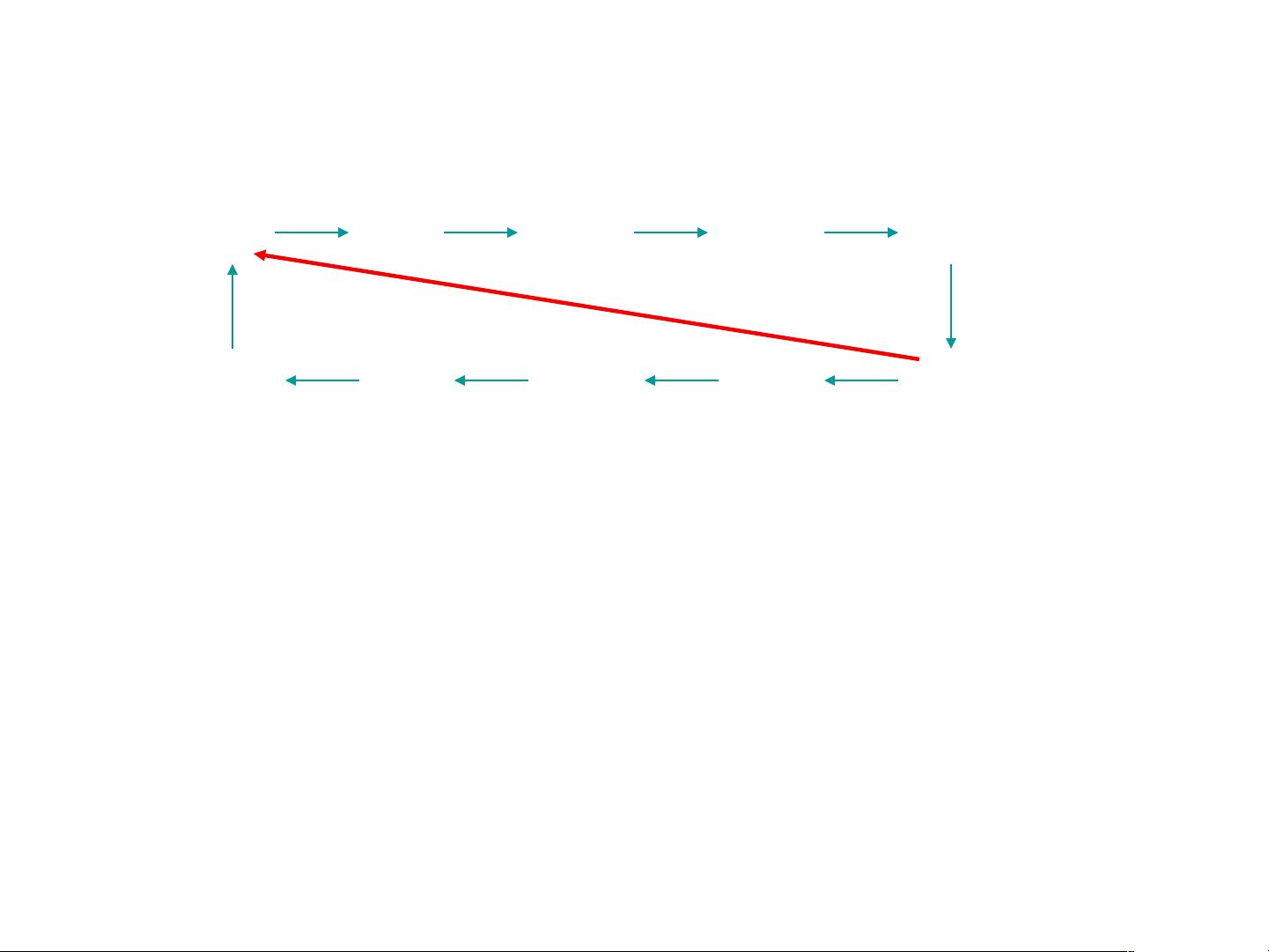

3. **状态转换**:时序逻辑电路的状态通常通过状态图表示。74160作为10进制计数器,其状态转换遵循特定的顺序。若要构造6进制计数器,可以通过反馈电路改变其行为。

4. **反馈连接**:有两种方法实现模6计数器,即同步置数法和异步清零法。同步置数法中,将74160的输出引回输入,同时利用一个2输入与非门进行反馈。异步清零法则是通过清零端实现。

5. **仿真验证**:在Quartus II中,可以使用波形编辑器设置激励信号,然后运行逻辑仿真以验证设计是否按预期工作。这有助于发现和修复设计错误。

6. **编译与分析**:在图形编辑完成后,执行编译过程,Quartus II将综合设计并生成逻辑等效的门级网表。通过时序分析器,可以评估电路的延迟性能,确保满足时序约束。

7. **层次化设计**:Quartus II支持层次化设计,允许将复杂的设计分解为多个模块,便于管理和复用。在本例中,虽然未详细提及,但可以通过层次显示工具实现自顶向下的设计方法。

Quartus II为时序逻辑电路的设计提供了强大的工具,使得设计师能够利用图形化界面轻松地构建和验证复杂的数字系统,包括计数器、移位寄存器等各种时序逻辑组件。通过熟练掌握这些工具,工程师可以有效地将概念转化为可编程硬件的实现。

2010-06-03 上传

2023-09-17 上传

2023-06-05 上传

2024-12-07 上传

2023-09-05 上传

2023-06-28 上传

2024-03-08 上传

dou19890806_

- 粉丝: 3

- 资源: 22