DDR2与DDR3 PCB高速信号完整性设计详解:4层板挑战与策略

需积分: 50 196 浏览量

更新于2024-07-18

2

收藏 784KB PDF 举报

本文主要探讨DDR2和DDR3在PCB(Printed Circuit Board,印刷电路板)信号完整性设计中的关键要素,这对于高速数据传输系统至关重要。随着DDR2速度提升至800Mbps甚至更高(如1066Mbps),以及DDR3达到1600Mbps,PCB设计者面临的挑战在于确保严格的时序匹配,维持信号波形的完整性。文章重点针对4层PCB(常见限制)和更高级的6层设计技术,强调了以下几点:

1. **叠层(StackUp)与阻抗**:

- 在4层板中,信号线仅限于顶层(TOP)和底层(BOTTOM),中间两层分别用于地(GND)和电源(VDD)平面。6层设计提供了更多灵活性,有助于提高电源完整性(PI)。

- DDR2要求单端信号线阻抗为50欧姆并匹配,差分信号线则需100欧姆终端匹配电阻。所有匹配电阻应连接到VTT,并保持50欧姆。

- DDR3在ADDR/CMD/CNTRL信号线上的终端匹配电阻范围在40-60欧姆,差分信号的阻抗匹配更为复杂,需要根据实际走线阻抗进行调整,通常在30-70欧姆。

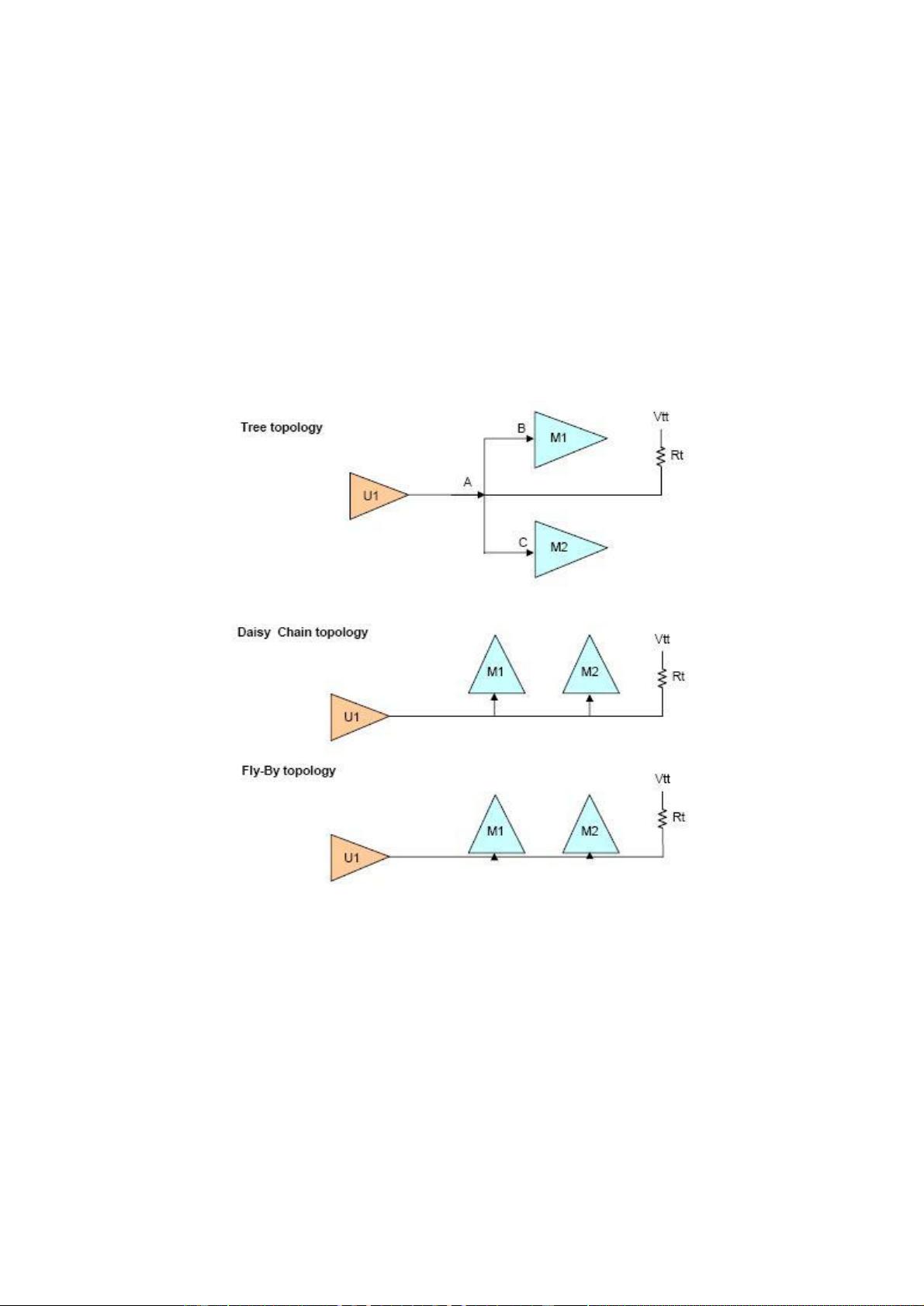

2. **互联拓扑与时延匹配**:

- 设计者需考虑信号之间的互联拓扑,以最小化延迟并避免串扰。使用合适的信号布局和路径规划至关重要。

- 时延匹配是通过精确计算和仿真工具(如Cadence ALLEGRO SI-230和Ansoft's HFSS)来实现的,确保信号到达目的地的时间一致性。

3. **电源完整性**:

- 对于高频率操作,电源平面(Power Plane)和地平面的紧密布局有助于减小电源噪声,保证稳定供电。

4. **技术要求对比**:

- 表1列出了DDR2和DDR3技术要求的共同点和差异性,展示了两者在速度、阻抗控制和信号特性上的区别。

本文深入剖析了在DDR2和DDR3高速内存系统中,PCB信号完整性设计的关键策略和技术细节,尤其是在资源有限的4层板设计中,设计师如何通过优化叠层、阻抗控制和利用现代仿真工具来实现高效、可靠的信号传输。这对于从事此类PCB设计的专业人士和学习者来说,是一篇极有价值的参考资料。

1206 浏览量

105 浏览量

128 浏览量

415 浏览量

2021-10-11 上传

128 浏览量

weixin_42647881

- 粉丝: 0

最新资源

- Java在AWS上使用Spring构建WebService教程

- Rust实现LeetCode与IRC模块应用探索

- Taro多端UI库:微信/支付宝/百度小程序及H5打包示例

- 优化Android市场新客户端页面滑动体验

- Raspberry-pi实现网络摄像头视频流的html展示

- Scipy 1.2.0版本在3399pro平台安装教程

- Windows下RabbitMQ 3.8.2环境搭建与otp_win64_22.1安装指南

- Fiddler规则自定义教程:多环境切换与高效线上代码调试

- Chrome浏览器书签管理与备份技巧分享

- Free-cofree: 探索HTTP基础之Scala函数式编程应用

- React项目开发入门:启动、测试与生产部署指南

- pymechtest-0.1.4-py2.py3-none-any.whl:Python库的安装与使用

- Atom包简化LeetCode编程挑战体验

- 美国农产品灭蝇胺残留限量标准分析

- R语言源代码文件管理与压缩技巧

- OrmLite数据库框架:Android开发一键集成方案