DDR2与DDR3 PCB设计:信号完整性和电源完整性策略

需积分: 31 168 浏览量

更新于2024-09-16

收藏 1.53MB PDF 举报

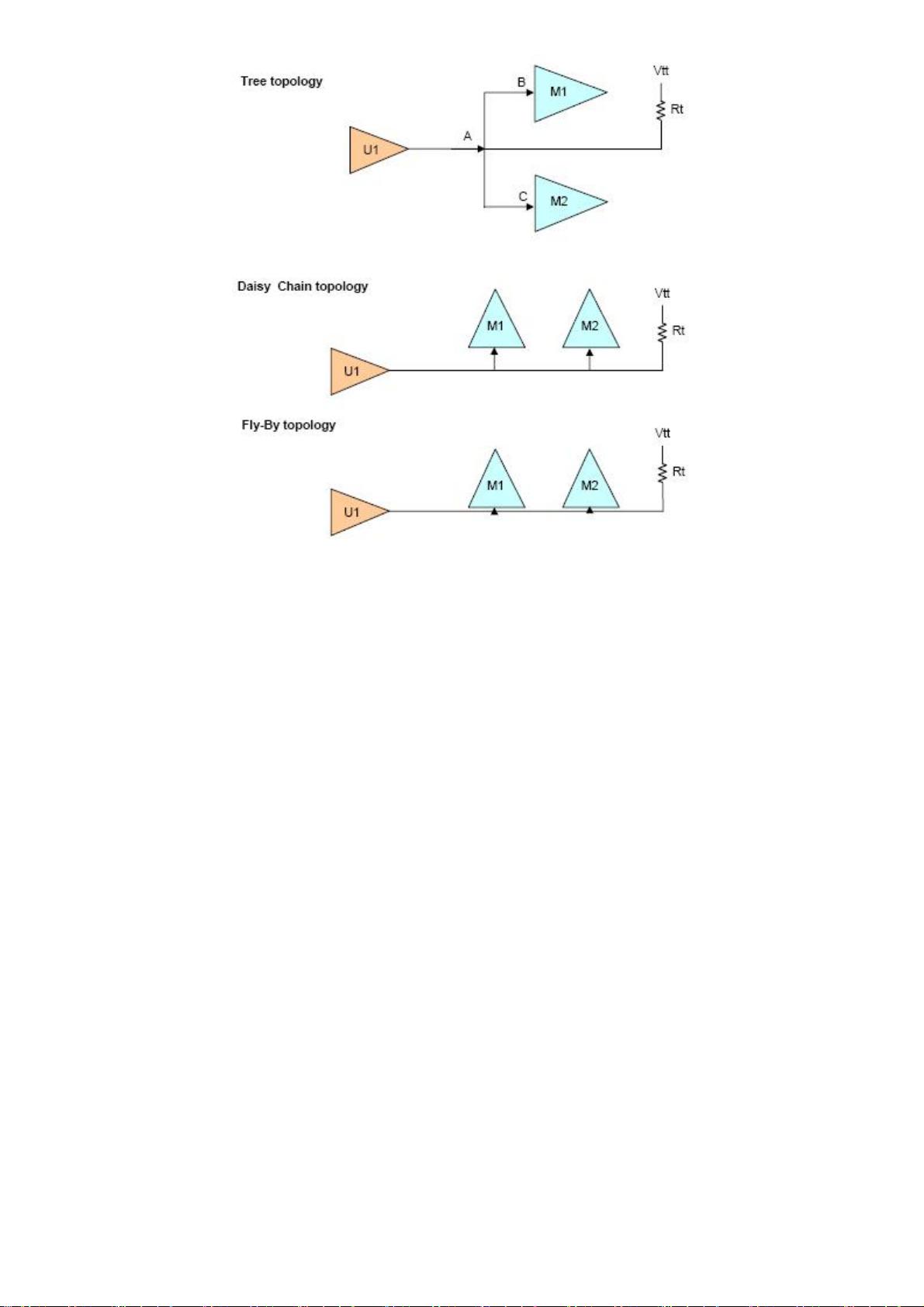

"本文主要探讨了DDR2-800和DDR3在PCB设计中的信号完整性和电源完整性问题,特别是在4层PCB板上的设计挑战。内容涵盖了DDR2和DDR3的技术要求对比,PCB的叠层设计,阻抗控制,以及互联拓扑等关键点,并提及了EDA工具如Cadence ALLEGRO SI-230和Ansoft's HFSS在设计和仿真中的应用。"

DDR2-800和DDR3是两种不同代的动态随机存取内存(DRAM)标准,它们在速度和性能上有显著差异。DDR2工作在800Mbps至1066Mbps,而DDR3则达到了1600Mbps。高速的数据传输要求PCB设计者在设计过程中特别关注信号完整性和电源完整性,以确保数据的准确传输和系统的稳定运行。

在4层PCB设计中,由于层数限制,通常将信号线布置在顶层和底层,中间层则作为接地(GND)和平面电源层(VDD)。对于DDR内存,Vtt和Vref通常在VDD平面上布线。6层PCB则提供了更灵活的布局和更好的电源完整性,因为电源层和地层之间的距离更近,可以提升功率因数校正(PI)。

阻抗控制是确保信号质量的关键因素。在DDR2设计中,所有单端信号线应保持50Ω的阻抗,差分信号线如CLOCK和DQS应为100Ω,并通过上拉到VTT的电阻进行终端匹配。DDR3设计有所不同,单端信号的终端电阻可以选择40Ω至60Ω范围,具体取决于ADDR/CMD/CNTRL信号线,而差分信号线的终端阻抗仍维持在100Ω。

PCB叠层的选择也会影响信号完整性。4层和6层PCB的叠层方式不同,6层板可以提供更好的信号隔离和更低的串扰。图1展示了这两种叠层方式的差异。

除此之外,时序匹配和串扰控制也是设计中的重要环节。时序匹配确保所有信号在同一时刻到达接收端,减少错误概率。串扰是指相邻信号线间的相互影响,需要通过合理的布线策略和信号隔离来减少。

最后,使用像Cadence ALLEGRO SI-230和Ansoft's HFSS这样的电子设计自动化(EDA)工具,设计师可以对这些复杂的问题进行精确计算和仿真,以优化设计并确保满足DDR2和DDR3的严格技术要求。

DDR2-800和DDR3的PCB设计涉及多个层面,包括叠层设计、阻抗控制、信号布局和仿真,这些都是保证高速内存系统性能和可靠性的核心要素。在实际设计中,需要综合考虑各种因素,并借助先进的工具进行精细化处理。

128 浏览量

139 浏览量

127 浏览量

点击了解资源详情

265 浏览量

139 浏览量

415 浏览量

238 浏览量

209 浏览量

jomerwj

- 粉丝: 0

最新资源

- 小型宽带微带天线设计与进展

- QTP 8.0 中文教程:自动化测试与脚本操作详解

- OPC UA基础解析 - 概述与概念RC中文版

- Proteus入门教程:无需实验板的51单片机仿真指南

- Java面试必备:核心知识点详解

- 万方视景科技:虚拟现实内容与项目专家

- Dialogic CTI技术入门到精通:系统工程师指南

- OBJ文件详解:格式、特点与基本结构

- ntop简易安装教程:快速部署流量监控

- Oracle初始化参数深度解析

- WebSphere MQ for z/OS 消息与代码手册

- JFreeChart 1.0.9 开发指南:免费资源与付费版本对比

- 使用Java与WebSphereMQ v6.0交互

- Win32下MinGW与MSYS安装指南

- Linux软件安装指南:从新手到高手

- ADO技术详解:高效数据访问接口