Synopsys ICCompilerII Block-level Implementation Lab Guide

版权申诉

"ICC2_lab-2019.pdf - Synopsys ICCompilerII Block-level Implementation Workshop Lab Guide"

这篇文档是Synopsys公司2019年针对ICCompilerII的实验室指导,专注于块级(Block-level)实现。ICCompilerII是一款先进的集成电路设计自动化工具,它在IC设计流程中扮演着关键角色,特别是在逻辑综合、布局布线和物理验证等阶段。这个工作坊实验室指南可能是为了帮助工程师和学生深入理解如何有效利用ICCompilerII进行高效的芯片设计。

在IC设计中,块级实现是一个重要的步骤,它涉及到将电路设计分解成可管理的模块或“块”,然后对每个块进行优化和布局。这个过程包括了逻辑综合,即将高级语言描述的电路转换成门级网表;时序优化,确保电路满足速度要求;以及布局与布线,将逻辑门放置并连接在一起,同时考虑功耗、面积和性能等因素。

Synopsys的ICCompilerII提供了先进的技术来处理这些挑战。它包含了自动化的逻辑优化算法,可以实现更好的性能和面积效率。此外,该工具还支持高级的物理设计功能,如寄生提取、时序分析和功耗管理,这些都是现代VLSI设计不可或缺的部分。

本实验室指南可能涵盖了以下几个方面:

1. **逻辑综合**:介绍如何使用ICCompilerII进行综合,设置参数以优化电路性能,例如设置约束、选择不同的综合策略等。

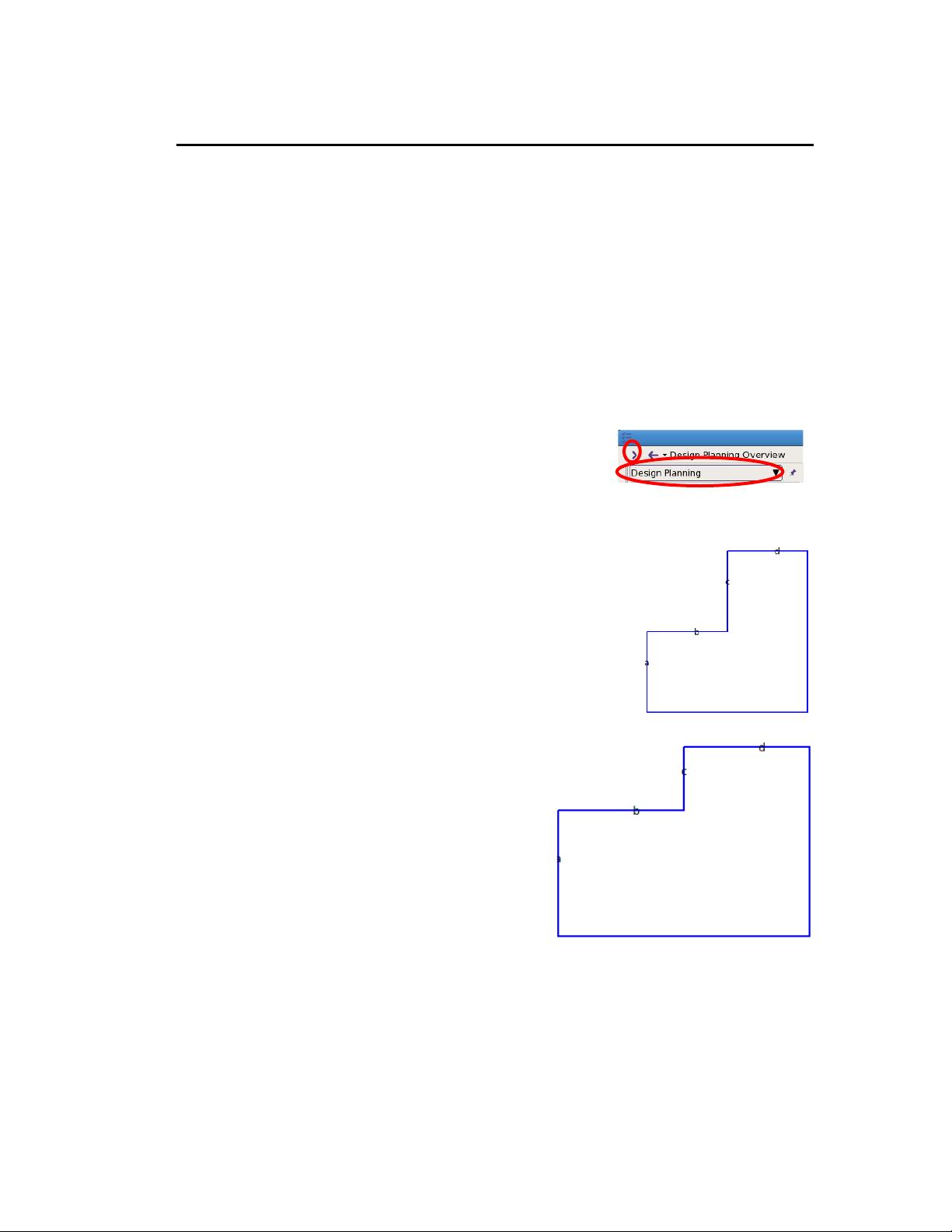

2. **物理设计**:包括块的布局规划、布线策略以及时序和功耗的考虑。

3. **时序分析**:讲解如何使用工具进行静态时序分析(STA),以确定设计是否满足速度要求。

4. **功耗管理**:讨论如何进行电源网络分析和动态功耗的优化。

5. **设计迭代**:如何根据分析结果反馈,调整设计并进行多次迭代,以达到最佳设计状态。

6. **接口与集成**:如何将优化的块与系统其他部分进行无缝集成。

此文档由Synopsys Customer Education Services提供,这意味着它包含了实践操作的指导和可能的案例研究,帮助用户通过实际操作来提升技能。然而,值得注意的是,文档中声明了所有内容为Synopsys的机密和专有信息,受版权保护,只能按照许可协议的规定使用或复制,未经许可不得复制、传输或翻译。

最后,文档还提到了美国的出口控制法律,表明其中包含的技术数据可能受到美国出口管制法规的限制,提示读者在分享或传播时需遵守相关法律法规。

181 浏览量

点击了解资源详情

202 浏览量

271 浏览量

2010-03-25 上传

166 浏览量

1449 浏览量

1449 浏览量

199 浏览量

chan_eric

- 粉丝: 1

- 资源: 13

最新资源

- j2me的eclipse配置

- JavaMail开发手册.pdf

- Pro LINQ Language Integrated Query in C# 2008

- java编码规约文档 写java程序必备的东东

- LoadRunner压力测试实例

- IEC62056-53中文版COSEM应用层

- Makefile使用手册.pdf

- java学习笔记--开发必备

- AIR Applications with HTML and Ajax

- Flex元数据标签详细简介

- 嵌入式linux入门笔记.

- Java 6 Platform Revealed

- MQ reason code

- symbian编码标准

- c# program

- 02界面编程-1(菜单).doc