FPGA实现的数控延时器设计:VHDL与延时精度优化

74 浏览量

更新于2024-08-29

收藏 589KB PDF 举报

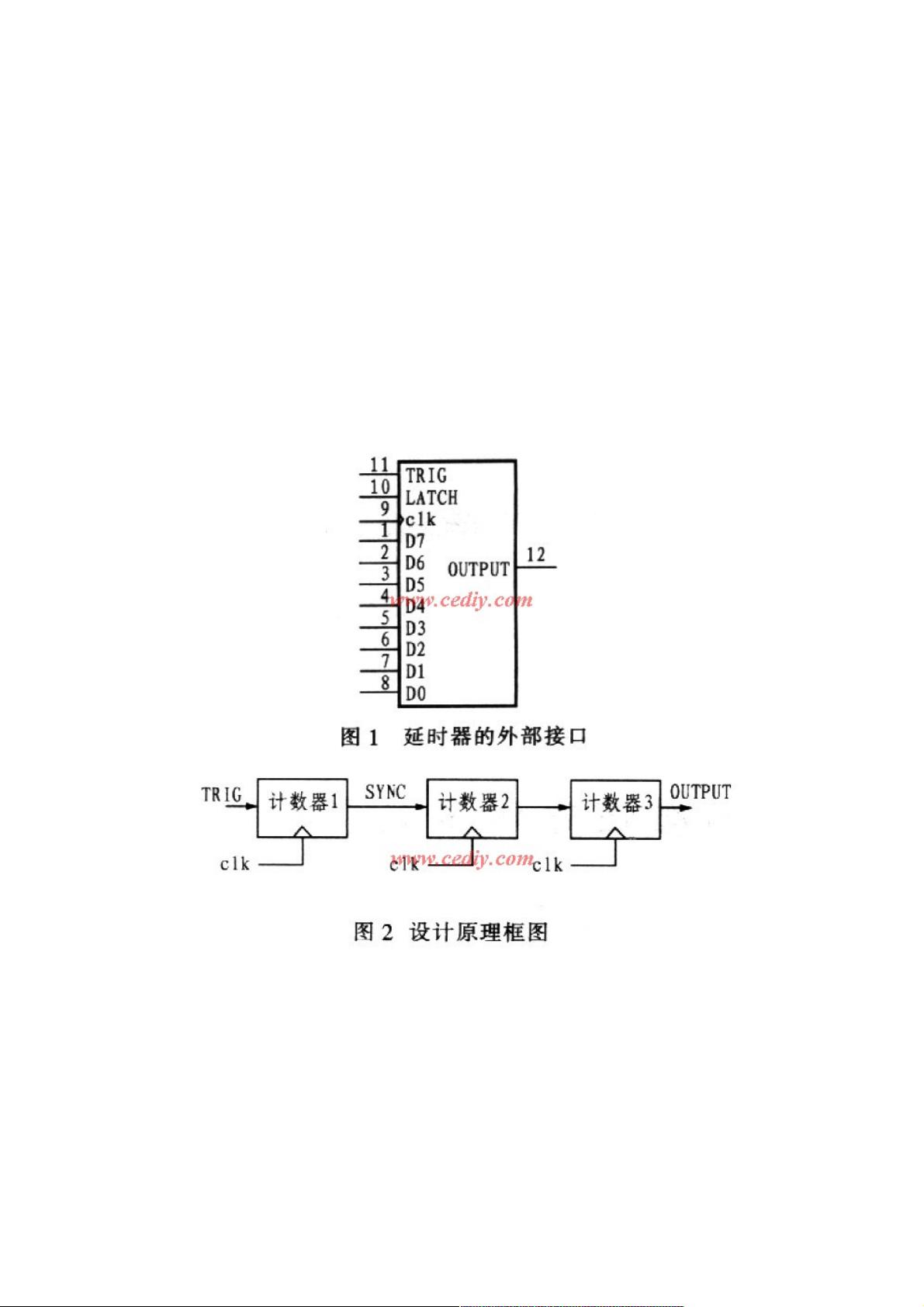

基于现场可编程门阵列(FPGA)的数控延时器设计是一种利用硬件描述语言VHDL和可编程逻辑器件(PLD)技术实现的数字集成电路。该设计的主要目标是创建一个可以根据8位输入数据线确定延时量的延时器,能够在接收到触发脉冲TRIG的上升沿时开始计数,以实现对触发信号的精确延时。

设计的关键点包括:

1. 计数器串联实现:延时器采用三个串联计数器,计数器1负责产生同步脉冲SYNC,同步时钟Tclk,触发计数器2计算延时长度,而计数器3则控制输出脉冲OUTPUT的宽度。这种设计确保了时钟稳定,减少毛刺和竞争冒险。

2. 外部接口设计:延时器的外部接口参考了AD9501的设计,具有高电平锁定数据的功能,但与AD9501不同的是,低电平表示数据锁定,而高电平则更新寄存器值。

3. 误差分析:如果触发脉冲与时钟上升沿不一致,可能导致延时误差。为了最小化这种误差,设计时序仿真模型,延时量由dlyLH信号的状态决定,数据总线data8上的数据实际决定了延时的具体值。

4. 硬件描述语言程序:使用VHDL编写程序,cntl变量表示延时量,cnt2表示输出脉冲宽度,cflag作为计数开始的标志。设计限制了最大延时量为256xTclk,当触发脉冲周期超过这个阈值时,延时器能够提供最大的延时能力。

5. 应用领域:该数控延时器与ARM开发板以及Altera公司生产的EPFl0K30AQC208-3 EPCI441专用电路结合,特别适用于雷达目标模拟器的控制部分,用于模拟目标的距离,体现其在实时控制系统中的实用性。

基于FPGA的数控延时器设计是一个集成硬件和软件的复杂系统,通过精确的时序控制和灵活的延时调整,满足了特定应用中对延时精度和范围的需求。VHDL的使用极大地简化了设计过程,提高了设计效率和灵活性。

127 浏览量

2021-05-18 上传

129 浏览量

128 浏览量

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

127 浏览量

weixin_38656142

- 粉丝: 6

- 资源: 909